行间转移CCD数字系统的VHDL设计*

和 琳,李彬华,尚媛园,金建辉

(1.昆明理工大学信息工程与自动化学院,云南 昆明 650051;2.首都师范大学电子信息工程系,北京 100048)

随着现代化生产过程和各领域科学研究应用对图像采集质量的要求日益提高,单独由ARM处理器或单片机为主控芯片的图像采集系统因为有限的程序存储空间与运行速度已不能满足某些市场的需要。而可编程逻辑器件 (如FPGA)依靠其集成度高、运算速度快、灵活性好等特点,逐渐占据了成像应用市场的主要地位[1]。

近年来,国内外通过FPGA控制CCD图像传感器成像的应用越来越多。如中国科学院西安光学精密机械研究所曾采用FPGA实现对TH7888A CCD芯片的控制[2-3]。日本大阪大学地球与空间科学学院研究的快速灵活CCD驱动系统也是在FPGA基础上开发的[4]。又如针对TH7899M面阵CCD设计的DSTIS相机和RDCCD相机[5-6],也是基于FPGA开发的面向天文应用的相机。

本文主要介绍了针对Kodak公司生产的KAI-04022行间转移面阵CCD构成的图像采集系统设计的一种数字控制方法。不同于之前所用的全帧CCD和帧转移CCD,行间转移CCD的垂直寄存器分布在遮光区,这样既可提高其光电二极管的光电转换效率,又能抑制漏光,成像质量会更高[7]。根据行间转移CCD特殊的电荷转移方式,选用Altera公司EP2C35F672 FPGA芯片,采用VHDL语言设计整个相机成像系统的数字控制部分,以便灵活、高效地实现数字系统的控制功能。本文详细介绍了该成像系统数字控制部分的设计思想与VHDL的实现过程,给出了关键的系统仿真与实测结果,并对结果进行了分析。

1 CCD图像传感器与模拟信号处理器的控制要求

KAI-04022是一款具有2048(H)×2048(V)像素,采用行间转移方式的CCD图像传感器,其结构示意图如图1。它一直被广泛应用到医学、科学、机械方面的可视设计中。带有微型透镜的7.4 μm×7.4 μm的像素具有高灵敏度、大容量的特点,有着很高的动态范围。它具有两个高速输出端口,以及像素合并的能力,能够以每秒16至50帧的速率进行图像的连续扫描和输出。垂直的溢流口结构提供了抗晕保护,自带的电子快门还可以实现精确的曝光控制。此外,它还具有暗电流、延迟比较小和无拖影的优点[8]。

行间转移方式是一种便于使用的标准CCD电荷转移方式。在CCD工作状态下,每个像素的光电二极管受到光的照射,随即发生光电转换,产生电子-空穴对,所有光电子都被收集到像素的势阱中。曝光结束后,全部像素中的光电子必须进行一次行间读出转移,即光电子从像素的光敏区势阱经过一个行间的转移门进入到与其相邻的遮光区(即非光敏的)CCD垂直寄存器(Kodak称之为VCCD)中。此后的光电子读出过程与通常的天文用全帧或帧转移CCD的读出过程类似。也就是垂直寄存器中的光电子在垂直转移时钟的驱动下,逐行地转移到CCD水平寄存器(Kodak称之为HCCD)中;其后光电子在水平转移时钟的驱动下,再逐个通过水平寄存器转移到输出传感节点,并在该节点上转换成电压信号,最后经输出放大器输出,如图1中虚线所示。

要使这些光电子有序无误地进行垂直与水平转移,并通过ADC将有效信号传输给用户端,就要严格按照CCD图像传感器以及模拟处理与AD转换器件数据手册要求的驱动时序对其进行控制。CCD图像传感器KAI-04022共需要4个驱动信号:垂直转移驱动信号、水平转移驱动信号、电子快门清零驱动信号和电荷快速转移清零驱动信号,分别将它们用符号V、H、VSUB和FD表示。

图1 CCD内部结构示意图Fig.1 Internal structure of the KAI-04022 CCD

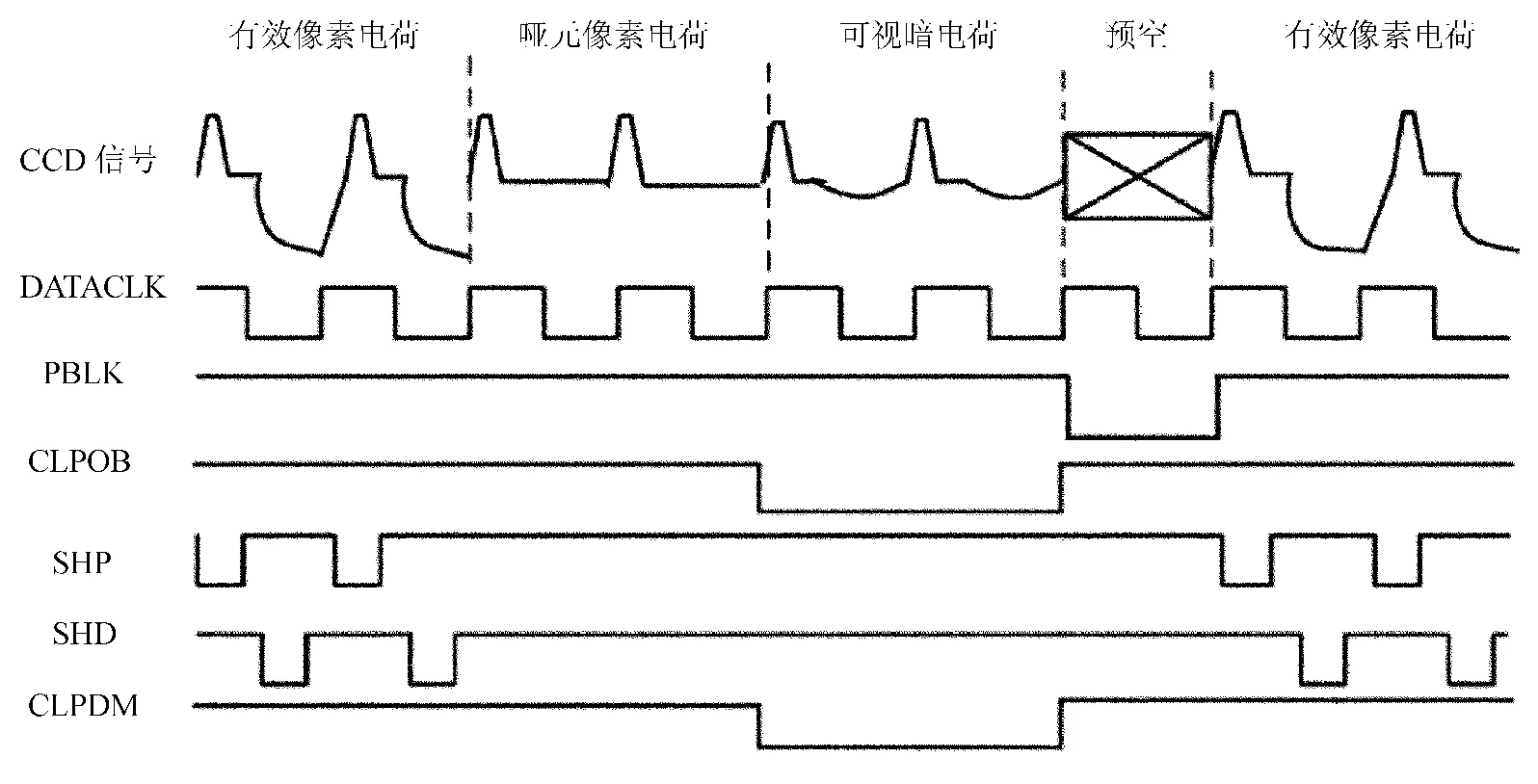

模拟处理与AD转换器件选用ADI公司的AD9845B,它是一款针对CCD应用的增强型信号处理器。它的采样速率可达30 MHz,而且自带一系列控制功能,如输入箝位、相关双采样(CDS)、像素增益放大(PxGA)、可变增益放大(VGA)、黑电平箝位和1个12位的 A/D转换器[9]。所以,AD9845B共需要6个驱动信号,包括读出数据时钟、消隐数据时钟、黑电平箝位时钟、相关双采样采集参考电平的时钟、相关双采样采集数据信号电平的时钟和输入箝位时钟。依次将它们用符号DATACLK、PBLK、CLPOB、SHP、SHD、CLPDM表示。根据KAI 04022的结构,6种驱动信号应按照图2所示的时序进行设置,这与AD9845B数据手册对时序的说明[9]稍有不同。

2 数字系统总体设计思想

根据CCD的用户数据手册,结合项目的具体要求,该系统主要实现CCD逐行扫描的全帧双路输出模式。并要求可设置4种水平转移读出频率,分别是8 M、4 M、2 M和1 M;以及2种清零模式:电子快门清除模式和电荷快速转移清除模式。同时要求可以控制曝光积分时间,选择是否超越读出(overscan),以及设置ADC的参数。根据VHDL语言自上而下的设计特点,采用一种由总体逻辑框架构成的顶层控制由各个逻辑模块组成的底层的程序结构,也就是将驱动程序分为顶层与底层两大模块分别进行设计。

图2 AD9845B驱动信号时序Fig.2 Sequences of driving signals for the AD9845B

顶层模块主要定义了数字控制系统部分与外部硬件连接的端口,以及与底层连接的一些端口,还定义了总体框架设计中所用信号与端口的映射关系,生成了4种水平转移读出模式时钟和底层各个模块所需工作时钟,并设计协调了如何切换底层模块中全帧输出、电子快门清零与电荷快速清除3种工作状态。

底层模块包括全帧输出、电子快门清零、电荷快速清除3个子模块部分。每个子模块都有独立的输入时钟信号与输出端口,可以独立完成各自任务。

3 数字系统的实现与仿真

在Altera QuartusⅡ8.0的开发环境下,采用VHDL语言分别对顶层模块与底层模块进行编程设计与仿真。下面介绍各模块的具体设计、仿真过程和一些实现技巧。

3.1 顶层模块的设计

这里主要定义了一些端口及其映射,生成了底层模块所需的一系列时钟信号,以及设定了底层3种工作模式的切换条件。以系统时钟clkin为输入主时钟,生成了3个控制用时钟:曝光阶段时钟clock_1ms、水平转移时钟clock_h、基本通用时钟clock_w。为了明确工作状态和模式切换条件,还设置了“cs”、“vsub_en”与“dump_en”3个条件判别信号,以便进行3种工作模式的准确切换及其正常运行。在QuartusⅡ中编译成功后,生成顶层模块,称之为TMGen。具体切换过程见图3 VHDL程序流程图。

3.2 底层模块的设计

底层由全帧输出、电子快门清零、电荷快速清除3个子模块构成。下面分别介绍各个模块的具体设计过程和仿真结果。

3.2.1 全帧输出模式

在相机系统的硬件设计过程中,已将KAI-04022 CCD按项目要求进行特殊连接,使其可以实现双路读出。在进行数字系统的设计之前,必须清楚CCD在整个全帧输出模式下的工作过程及要求。

按照KAI-04022的数据手册,CCD在上电初始状态下,所有输出都应保持初态;之后等待“clr”信号进行清零与曝光;曝光结束之后,要经过一个2台阶3电平的读出转移垂直时钟,将光电子由光电二极管转移到VCCD寄存器中;当读出转移结束之后,就进入图像的全帧读出过程,由垂直转移驱动信号先控制光电子由VCCD寄存器转移到HCCD寄存器中,再由水平转移驱动信号控制光电子通过HCCD、输出节点、输出放大器以及ADC逐个输出;在结束2072行×2048列光电子全帧输出的同时,生成一个输出结束的信号量“Frmend”,用来控制每一幅图像全帧完整输出后,程序可以停止下来。在此暂不实现逐行扫描的循环输出。

图3 TMGen模块程序流程图Fig.3 Program flowchart of the TMGen module

据上述分析,为了保证这一系列进程能够有序准确的运行,需要添加一些阶段性使能信号:CCD清零结束,使能信号sub_end<=‘1’,驱动曝光程序段开始运行;CCD曝光结束,使能信号VS_enable<=‘1’,触发行间转移程序段开始运行;行间转移结束,使能信号VH_enable<=‘1’,触发垂直转移程序段运行;垂直转移结束后,使能信号H_enable<=‘1’,触发水平转移程序段运行。每一行像素完成转移之时,都会产生一个Linend信号表示这次垂直/水平转移的周期结束;当2072次全部经过垂直水平转移结束之后,Frmend<=‘1’,将所有信号置于初态。

在水平转移光电子阶段,信号处理器AD9845B要对哑元、黑电平、缓冲及有效像素做出相应的处理,这就需要按照其时序要求(如图2),配合CCD水平读出过程,同步地向ADC提供一系列时钟信号,如前面所提到的数据读出时钟信号DATACLK、采样时钟信号SHP与SHD、其他箝位时钟信号PBLK、CLPOB、CLPDM。

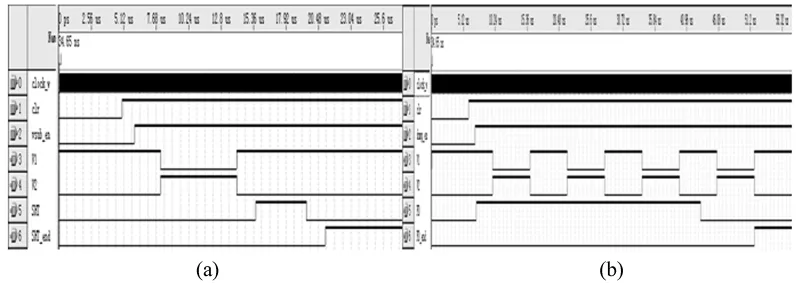

在QuartusⅡ8.0下进行编程与仿真,可以验证所生成的时钟信号是否正确,仿真结果如图4。图4(a)是电荷读出转移的仿真波形,其中自上而下的信号量依次是:clkin、V1、V2、V3。V1、V2、V3是垂直时钟控制信号,V1通过硬件电路之后成为第1相驱动时钟,V2和V3控制硬件电路产生2台阶3电平的第2相驱动时钟见图6(a)。

图4(b)是在全帧输出模式下光电子在水平转移读出过程中所需要的垂直、水平时钟以及AD处理器所需要的一系列信号时钟。图中自上而下的信号量依次是:clkin、V1、V2、V3、Reset、H1、H2、ADCLK、CLPDM、CLPOB、PBLK、SHD、SHP。

图4 全帧模式下行间转移、垂直与水平转移时钟的仿真波形Fig.4 Simulated waveforms of interline transfer,vertical-transfer and horizontal-transfer clocks under the full-frame mode

3.2.2 电子快门清零模式

KAI-04022 CCD具有电子快门的功能。由于衬底部位(SUB)的对地电压值决定了光电二极管储存电荷容量的大小,所以当SUB的电压值在8 V时,光电二极管能够储存最多的电荷量。如果逐渐增大该电压值,光电二极管的电荷容量将会随之下降。当电压值升高到48 V的时候,光电二极管中不能储存电子。也就是说,给SUB提供一个大约48 V大小的电压脉冲,就可以清除掉CCD面阵上全部光电二极管中所带的电荷[8],这样就完成一次电子快门动作,即完成电子快门清零。

该模块的主要设计任务是配合垂直转移时钟信号,产生一个电压为48 V的脉冲。根据需要增加一个VSUB的使能信号vsub_en,当其置‘1’的条件下才可以进行电子快门清零。根据CCD的数据手册,将VSUB的外部端口命名为SHT。此外,为便于检测和控制,还添加了标志该段程序运行结束的信号SHT_end。该模块的仿真结果如图5(a),其中信号量从上至下依次为clock_w、clr、vsub_en、V1、V2、SHT、SHT_end。

图5 清零时钟的仿真波形Fig.5 Simulated waveforms for the signal intervals of clearing clocks

3.2.3 电荷快速清除模式

在正常的电荷转移模式中,例如在全帧转移模式中,光电子是随着垂直转移时钟信号,按一定频率由VCCD寄存器依次朝向底部的HCCD寄存器方向转移的。即每一次垂直转移时钟来临,在下方最靠近HCCD寄存器的那行VCCD寄存器中(如图1)的光电子都将转移至HCCD寄存器中。然后等待水平转移时钟驱动此行光电子由CCD水平寄存器逐个转移至输出节点去进行处理。KAI-04022 CCD在VCCD与HCCD交接处,设置有一个快速行清除(Fast Line Dump,简称为FD)门,用以实现光电子快速倾泻的功能。当光电子受到垂直时钟驱动,在进行垂直向下转移的过程中,如果将FD置高电平,则最靠近HCCD寄存器的那行垂直寄存器的光电子,将全部通过FD被倾泻掉,不会转移到水平寄存器中[8]。这样就完成了一次快速的电荷清除过程,将其称为电荷快速清除模式。

该模块的设计任务是配合垂直转移时钟信号,在需要快速清除电荷的时候,对FD置高电平,并使其时序关系满足CCD数据手册要求。该模块也只有当其使能信号dump_en置‘1’的条件下才能运行,这样做同样是为了顶层模块方便操控。此外,也添加一个结束标志信号FD_end,以检测此段程序是否运行结束。具体仿真结果如图5(b)。从上到下,信号量依次为clock_w、clr、dump_en、V1、V2、FD、FD_end。

4 测试结果及分析

在进行上述VHDL设计与仿真工作的同时,CCD相机硬件电路的设计、制作等工作也在同步进行。当数字控制系统与实际的硬件电路、控制任务进程的NiosⅡ软核CPU模块以及实时操作系统μC/OSII中执行控制的C程序模块相连接后,可能会增加一些不确定因素,仿真与实际测试的结果可能会有所差别。因此,当硬件电路静态上电调试完成后,有必要加入上述数字控制系统进行动态综合调试。以下介绍在这一过程中的测试情况。

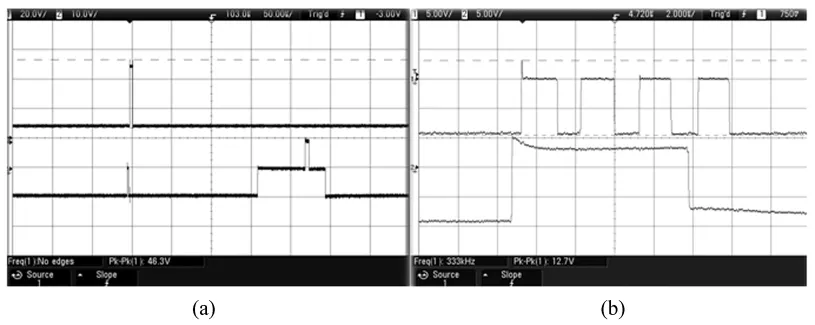

将FPGA开发板与所制作的电路板相连接,在电路板上CCD的管脚处进行实际测试。所用测试工具是安捷伦MSO6012A多通道混合信号示波器,由于文章篇幅有限,部分测试结果如图6~8。

图6 全帧模式下垂直与水平转移时钟的实测波形Fig.6 Measured waveforms of vertical-and horizontal-transfer clocks under the full-frame mode

图6是由示波器模拟输入端测试所得到的全帧输出模式下的垂直转移时钟波形与水平转移时钟波形。从图6(a)垂直转移时钟波形可以直观地观察到V2(下方)端口的2台阶3电平特性,这是仿真波形所不能观测到的。从示波器上可以读出垂直转移时钟的电压值分别为:V1=(-9 V~0 V),V2=(-9 V~0 V~9 V)。由于示波器信号V1(上方)与V2距离较近,导致V1与V2波形出现重叠情况。图6(b)水平转移时钟H1(上方)与H2(下方)的电压值分别读出为:(-4.5 V~0 V)、(0 V~4.5 V)。这次测试是在水平读出频率设定为4 MHz的条件下进行的,从示波器上可以读出H1、H2的信号周期为250 ns,也符合了设计要求。

图7(a)、(b)电子快门清零模式与电荷快速清除模式中的VSUB信号与FD信号,同样用示波器模拟输入端测试。如图7(a),由于电子快门信号与V2第2级台阶之间有一个曝光积分的时间关系,所以将V2(下方)与VSUB(上方)一起对照测试。从图中可以读出VSUB的电压值是(9.3 V~49.3 V)。这里的衬底电压之所以选择9.3 V,而不是上面提到的8 V,是因为所使用的CCD器件上Kodark标出的数值就是9.3 V。图7(b)也选择了V2(上方)为参考信号,进行FD(下方)信号的测试。FD的电压范围也可读出,为(-9 V~4 V),满足数据手册的要求。

为了确定CCD输出正常,观察其信号质量,还特别对2个CCD输出端口进行了测试,从图8中的两幅波形可以清晰地看出在一幅图像的采集过程中CCD一行图像信号的变化情况。图8(b)是对(a)中信号展宽所得的部分像素信号的细节,从中可以清晰地观察单个像素模拟信号的输出情况。

图7 清零时钟的实测波形Fig.7 Waveforms measured of the clearing clock

图8 CCD输出模拟信号Fig.8 Analog signals output from the CCD

通过观察示波器实测波形,可以清楚地获得所需信号的周期、频率与电压值。经过反复调试,各信号值现都已符合CCD与ADC数据手册要求。

5 结束语

采用VHDL硬件描述语言与FPGA器件进行的数字系统设计,完全达到了此成像控制与图像采集系统的逻辑控制要求。这种采用VHDL加Nios软核处理器的设计方法,使整个系统的设计、调试、修改、维护工作变得十分方便。目前,已基本完成了CCD图像采集与传输方面的调试工作,并成功地获得了图像,下一步的工作是对整个系统进行优化处理,以提高成像系统的性能。

[1]王道宪,贺名臣,刘伟.VHDL电路设计技术 [M].北京:国防工业出版社,2004.

[2]黎向阳,高伟.基于VHDL的面阵CCD图像传感器的驱动设计 [J].科学技术与工程,2007,7(14):3584-3586.Li Xiangyang,Gao Wei.Design of Area Array CCD Image Sensor Driving Circuit Based on VHDL [J].Science Technology and Engineering,2007,7(14):3584-3586.

[3]侯新梅,李自田,胡炳樑.基于FPGA的面阵CCD驱动电路的设计 [J].现代电子技术,2010,33(7):195-197.Hou Xinmei,Li Zitian,Hu Bingliang.Design of Driving Time Circuit for Area Array CCD Based on FPGA [J].Modern Electronic Techoique,2010,33(7):195-197.

[4]Emi Miyata,Chikara Natsukari,Daisuke Akutsu,et al.Fast and Flexible CCD Driver System Using Fast DAC and FPGA [J].Nuclear Instruments and Methods in Physics Research Section A:Accelerators,Spectrometers,Detectors and Associated Equipment,2001,459(1/2):157-164.

[5]王慧娟,李彬华,李勇明,等.同幅双速跟踪成像CCD相机数字控制器的设计 [J].天文研究与技术——国家天文台台刊,2007,4(4):369-375.Wang Huijuan,Li Binhua,Li Yongming,et al.Design of Digital Controller for a CCD Camera with Dual-Speed Tracking Imaging On Same Frame [J].Astronomical Research & Technology——Publications of National Astronomical Observatories of China,2007,4(4):369-375.

[6]陈建军,李彬华,张牛虎,等.基于FPGA的CCD相机的电路设计 [J].天文研究与技术——国家天文台台刊,2009,6(2):130-135.Chen Jianjun,Li Binhua,Zhang Niuhu,et al.Design of Electronic Circuits for an Astronomical CCD Camera [J].Astronomical Research & Technology——Publications of National Astronomical Observatories of China,2009,6(2):130-135.

[7]米本和也.CCD/CMOS图像传感器基础与应用 [M].北京:科学出版社,2006.

[8]KADAK KAI-04022 Image Sensor [EB/OL].http://www.kodak.com/go/imagers.

[9]Complete 12-BIT 30 MSPS CCD Signal Processor-AD9845B [EB/OL].http://www.analog.com/.