CMMB系统中RS编码器的实现

谭泽富 谢 红

(1.重庆邮电大学通信与信息工程学院,重庆 400065)

(2.重庆三峡学院物理与电子工程学院,重庆 404100)

全球移动由中国国家广电总局发布的行业标准CMMB(China Mobile Multimedia Broad-Casting,中国移动多媒体广播)采用卫星和地面网络相结合的“天地一体、星网结合、统一标准、全国漫游”的技术体系,可实现我国幅员辽阔,环境复杂的有效覆盖.其核心技术——STiMi技术,与大多数其他移动多媒体标准一样,采用具有高性能的RS码作为外码.不同的是,它采用LDPC码作为内码,与RS码一起构成CMMB的两级信道编码体系,两级信道编码在通信系统中可以有效抵抗干扰,其支持移动性的能力要好于一级信道编码.

RS码是一种特殊的分组线性码,由于它编码简单、构造方便,并且代数结构非常严格,所以在同样的编码冗余度下,RS码的纠错能力最强,特别是在短的中等码长下,其编码性能几乎接近于理论值,[1]故在无线通信领域中得到非常广泛的应用.本文探讨了CMMB系统中RS编码的基本原理,并根据其原理,给出了基于FPGA的RS编码器的设计.

1 CMMB系统中的RS编码原理

RS(Reed Solomon)码是一类纠错能力极强的多进制BCH循环码,能纠正多个错误,特别针对大容量的存储设备,无线和移动通信设施,数字电视(DTV),卫星通信,数字视频广播(DVB)和宽带调制解调器等突发性错误.

在CMMB系统中,RS编码器并不是完全独立的,通常和字节交织器一起使用,如图1所示.来自上层的比特数据流按低位优先的方式划分为字节,逐字节从左至右按列填满字节交织器的信息区(图1中白色区域),然后按行进行RS编码,字节交织器的校验区(图1中灰色区域)为RS码字的校验字节,每个RS码字的校验序列和该码字的信息序列在字节交织器的同一行,当编码完成之后,字节交织器中的数据就会逐字节按列从左至右取出.CMMB中采用的编码长为240字节的RS(240, K)截短码,该RS码由原始RS(255, I)系统码通过截短产生,其中 I=K+15.K为一个码字中信息序列的字节数,校验字节数为240-K.RS(240, K)码有4种工作模式,分别对应的K值为240,224,192,176.其中码的纠错能力为(240-K)/2个字节.很明显,K越小,该RS码的纠错能力就越强,但信息冗余会相应地增大.[2]

根据CMMB标准规定每个经过随机化的K = 240,K = 224,K = 192,K = 176字节的传输包都要进行RS编码.经过RS编码,每个传输包后面分别增加0,l6,48,64个校验字节,成为240个字节组成的错误保护包,记为RS(240, K).当K = 224时,RS (240, 224)就具有t = (240-224)/2 = 8字节的纠错能力.

图1 字节交织和RS编码

RS (255, K)码是基于有限域GF (256)的循环码,集合GF (256)包含的元素为:

截短码RS(240, K)的生成多项式表示为:

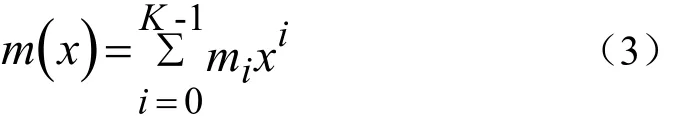

输入的信息序列多项式表示为:

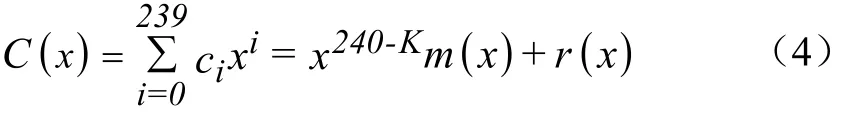

输出的系统码多项式为:

其中

2 CMMB系统中RS编码器的设计

在一些特定的应用域中,RS码的设计与实现是比较困难的.RS码由于在有限域上进行的代数运算,因而与其他常用的二进制系统有所不同,实现相对复杂一些,其复杂度主要取决于有限域的大小、码字的长度、采用的编码算法等.编码器的实现方式主要有:微处理器实现、DSP实现、ASIC实现和FPGA实现.[3]其中利用FPGA实现CMMB系统中RS编码是最简单的方法.FPGA能够既快速又经济地将电路描述转化为硬件实现,而且对设计的修订也比较方便.而通常的ASIC需要的设计时间较长,成本高,灵活性差,所以本文是基于FPGA设计RS编码的结构.

2.1 RS编码器结构

令CMMB系统中RS (240, K)码的K个信息符号序列m=(mk-1,mk-2,…,m1,m0),该信息的多项式可以用(1)式表示,首先将 m(x)左移240-k位得到多项式 m(x)x240-k,然后将它与生成多项式 g(x)相除,就可以得到RS编码后的多项式c(x),其中 r(x)为效验多项式,是 m(x)x240-k除以g(x)后的余式,其次数低于240-k.当且仅当域元素(c0 ,c1, …,c 239)组成的向量是生成多项式g(x)的倍数时,此向量才能为码字,当在 CMMB系统中能完全纠正(24 0-k)/2个错误时,RS编码的生成多项式的表达式为:

其中α是有限域 GF (2m)的元素.设输入信息码为 m(x),编码后的码组为 c(x),则

因为c(x )=m(x)x240-k+ r(x ),r(x)为多项式

m(x)x240-k除以 g(x)的余式.因此可以用240-k阶除法电路构成编码器.又由于生成多项式

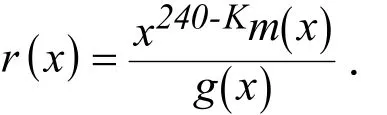

所以RS编码器的结构图可以设计为如图2所示.

图2 RS编码器结构图

此编码器的工作原理为:

1)将寄存器b0,b1 , …, b 239-k全部清零,打开门1,关闭门2,然后送入信息码组 m0, m1 , … ,mk-1.信息码组在电路中被分为两路,一路经过数据选择器直接输出,一路乘以 x240-k后进入 g(x)除法电路并移位,每个时钟移一个字节.

2)经k次移位后,信息码组全部进入电路,然后完成除法运算,此时电路中移位寄存器内保存的就是余式 r(x)的系数,也就是RS码的效验码组.

3)当k+1个时钟到来时,信息码组暂停输入,关闭门1,打开门2,这时经过240-k次移位后的数据全部移出,得到240-k个效验码组,跟在原来长为k的信息码组后面,就组成(24 0,k)码输出,这就完成了RS码的一组编码.

4)寄存器 b0,b1 , …, b 239-k全部清零,重复步骤(1)、(2)、(3),继续对下一组RS码进行编码.

2.2 RS编码器中的乘法器

从 RS编码器结构图可以看出编码器包含240-k个有限域乘法器,有限域乘法器是实现RS编码器的关键.它一般可以用查表法,线性反馈移位寄存器法[4],Messey-Omura法[5]和Berlekamp位串法[1,6]实现.为了实现高速可靠的计算,本文所使用的乘法器为并行结构,乘数与被乘数均使用标准基表示,不需要基与基之间的转换,其应用广泛,结构简单,且易于扩展至高阶有限域中.

CMMB系统中的RS码是基于有限 GF (28)的,GF (28)域中,本原多项式为x8+ x 4+ x3+ x2+1=0设a,b,c ∈GF (28),且c=a×b, GF (28)中的任何元素都可以表示为x的0~7次方的组合.

式中的⊕表示异或运算,可见结构中的乘法运算转换成了一组数字逻辑运算,而且结构简单,易于实现.尽管在实现逻辑运算时需要较多的门数,但可以节约大量的寄存器,从而可以明显减少芯片的面积.

3 结 语

当传输CMMB信号数据流时,传输信道中存在着各种干扰,严重影响传输信号的质量.为了提高数据的抗干扰能力及传输的可靠性,必须对信号数据进行RS纠错编码处理,这种编码具有发现和修正信号在传输过程中产生误码的功能,从而提高了CMMB的通信质量.本设计实现了CMMB系统中RS(240, K)的编码器设计,并通过FPGA来实现,与其他实现方法相比,用FPGA实现的RS编码电路更为简单,成本更低.其中乘法器是电路中的关键部分,合理的选择乘法器可以高速可靠的完成乘法运算,最终完成差错率低,延迟小的RS编码.

[1]王新梅,肖国镇编著.纠错码-原理与方法[M].西安:西安电子科技大学出版社,2002.

[2]中华人民共和国广播电影电视行业标 GY/T 220.1-2006,CMMB广播信道帧结构、信道编码和调制[S]. 2006.

[3]何秋阳.基于FPGA的RS编码器的设计与实现[J].电子科技,2009,22(2):44-46.

[4]Laws Jr BA,Rushforth C K.. A cellular-array multiplier for GF(2m)[J]. IEEE Trans Computer.1971.

[5]Wang C C.. VLSI architectures for computing multiplications and inverses in GF(2m)[J].IEEE Trans Computer,1985,34(8).

[6]Berlekamp E R.. Bit-serial Reed-Solomon encoders[J]. IEEE Trans Information Theory,1982,28(6).