1.2 V高线性度低噪声折叠混频器设计*

程知群,朱雪芳,高俊君,徐胜军

(杭州电子科技大学射频电路与系统教育部重点实验室, 杭州310018)

目前,无线通信设备正朝着低电压、低功耗、低噪声和高线性度的趋势发展。混频器作为收发机中的关键模块之一,对通信设备的上述性能产生直接的影响。随着微电子工艺的发展, CMOS器件的栅长进一步缩小, MOS器件的过驱动电压也进一步降低,这就为设计低压低功耗的射频电路提供了可能,但是依靠减小MOS器件的栅长降低工作电压是有限的。因此,电路设计者把更多的注意力集中到电路拓扑结构上,使设计具有低压结构的射频电路成为了热门课题。

传统的Gilbert混频器由跨导级、开关级、负载级堆叠组成,其结构自下而上分别为跨导级、开关级、负载级[1]。这种结构中,所有的直流电流都流经跨导级、开关级和负载级,跨导级与开关级电路都需要一个开启电压(Von),负载级也会有一定的电压降(VRL),因此,电源电压的最小值Vdd,min=2Von+VRL。如果采用低电源电压,这种结构不能保证所有的管子都工作在饱和区。也就是说, Gilbert混频器不能满足低电压的要求,需要对其做出改进,如:文献[2-3]提出省去尾电流管来减小电源电压,文献[4-11]用折叠结构代替堆叠结构来解决上述问题。

文献[8]给出了折叠结构和堆叠结构的比较,折叠结构增加了两个射频中断电路和一个耦合电容。这样对直流通道来说,跨导级与开关级、负载级的直流电路分开,两条支路相互独立,互不影响。电源电压只需提供相当于一个开启电压(Von)的值就能使跨导管与开关管都工作在各自的饱和区,即电源电压的最小值Vdd,min=Von+VRL。达到了低电源电压的目的。但是,射频中断电路一般用LC谐振网络实现,电感的使用增加了电路的版图面积和噪声。本文设计了一种新的折叠结构混频器,电路不使用具有大电感的LC谐振电路,工作于1.2 V电压时,得到了低电压、低功耗、低噪声和高线性度的性能。

1 电路设计与分析

1.1 电路拓扑结构

本文设计的折叠混频器拓扑结构如图1所示,M1~M4为跨导级, M5~M8为开关级, RL为负载电阻。RF输入端接匹配网络, IF输出端接源跟随器作为输出缓冲电路(bu ffer)。

图1 交流耦合折叠混频器拓扑结构

该折叠混频器电路的跨导级采用电流复用技术[12],由NMOS管(M1、M2)、PMOS管(M3、M4)和隔直电容Cd组成交流耦合互补跨导结构。跨导级的输出端(A、A′点)与开关管的源极相连。跨导级直接接于电源电压,使得跨导管M1和M2的直流电流由两部分组成,一部分来自M3和M4,另一部分来自开关管和负载电阻, 达到了低电源电压的目的。由于流经开关级与负载级的电流很小,这样一方面使得开关管产生的闪烁噪声减小,另一方面负载电阻RL值可以适当加大,从而提高了混频器的转换增益。所以该电路既满足了低电压的要求,又能保证混频器在低电源电压下有良好的性能。

1.2 跨导电路设计

图2是几种折叠混频器跨导电路。图2(a)在跨导级NMOS管M1漏端接负载电阻R, M1管的电流In在A点分流,一部分流经开关管(Is),另一部分流经负载电阻(Ir),但是这种跨导电路的缺点是射频信号一部分通过负载电阻R泄露到交流地。为了减少射频信号的损失,必须增加电阻R,这样又会使节点A的直流电压减小,在低电源电压下,不能保证M1管工作在饱和区。为了解决这个问题,用有源负载替代负载电阻R,如图2(b)。但是,这里的PMOS管仅仅增大了节点A与电源电压之间的阻抗,如果把M1和M2的栅极连起来,形成CMOS反相器结构,那么M2在增加阻抗的同时还能跟M1共同放大射频信号[12],如图2(c),这样就完全避免了射频信号通过M2泄露到交流地。由图可知, Is=In+Ip,总跨导gm=gmn+gmp(gmn是NMOS管的跨导, gmp是PMOS管的跨导),所以CMOS反相器有效地提高了混频器的转换增益。

图2 折叠混频器的跨导级几种结构

再来分析一下该结构的直流工作状况, M1和M2的栅极加相同偏置电压Vrfdc,假设Vt为MOS管的阈值电压, Vovn为M1的过驱动电压, Vovp为M2的过驱动电压,则有:Vovn=Vrfdc-Vt, Vovp=Vdd-Vrfdc-Vt,所以 电源电压 最小值 Vdd,min=Vovn+Vovp+2Vt。在0.18 μm CMOS工艺中, Vt典型值为500 mV,因此用反相器作为跨导电路的混频器只适用于1 V以上的电源电压。为了使混频器能满足更低的电压,在M1和M2之间增加隔直电容Cd, M1和M2管偏置分开,如图2(d)。这种结构称为交流耦合互补跨导。假设Vrfdcn为M1的偏置电压, Vrfdcp为M2的偏置电压,则电源电压的最小值Vdd,min=Vovn+Vovp+2Vt+Vrfdcp-Vrfdcn,可见,在Vrfdcn>Vrfdcp时, Vdd,min比常规反相器更小,适用于更低的工作电压。

1.3 性能分析

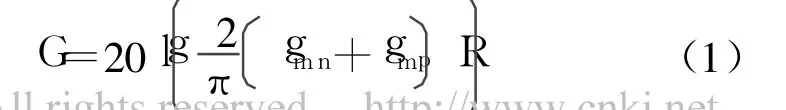

1.3.1 增益

假设本振信号LO为理想方波信号,则该混频器(如图1)的增益可表示为:gmn是M1和M2的跨导, gmp是M3和M4的跨导, R即负载电阻RL的值。因为开关管的漏极电流很小,所以负载电阻值可以适当增加,由式(1)知,混频器的增益将随之提高。值得注意的是,增大负载电阻值的同时必须保证节点A的直流电压足够使得M1和M2工作在饱和区。

1.3.2 噪声系数

假设本振信号为理想方波信号,并考虑镜像频率的影响,噪声系数的表达式[9]为

RS为源阻抗, RL为负载电阻值,系数γn对长沟道晶体管来说等于2/3,对于亚微米MOSFET, γn的值较大。由式(2)知,只要选择合理的偏置电压Vrfdcn、Vrfdcp和M1 ~M4的宽长比,噪声系数随着跨导的增加而减小。

1.3.3 线性度

如果节点A(见图1)的电压过高,开关管将会关断。也就是说,如果M1和M3的电流很大, M1和M2的输出端电压也增大,这样就会关断开关管M7和M6或者M5和M8。开关管进入线性区,影响混频器的线性度,所以降低节点A的电压,并让开关管远离线性区[9],即Vgs≈Vth,能提高混频器的线性度。

2 电路仿真

该混频器设计基于SMIC 0.18 μm标准CMOS工艺,用Advanced Design System软件进行电路设计与仿真。电源电压1.2 V;RF频率为2.5 GHz,功率为-30 dbm;LO频率为2.6 GHz,本振信号的电压摆幅VLO=600 m Vpp。

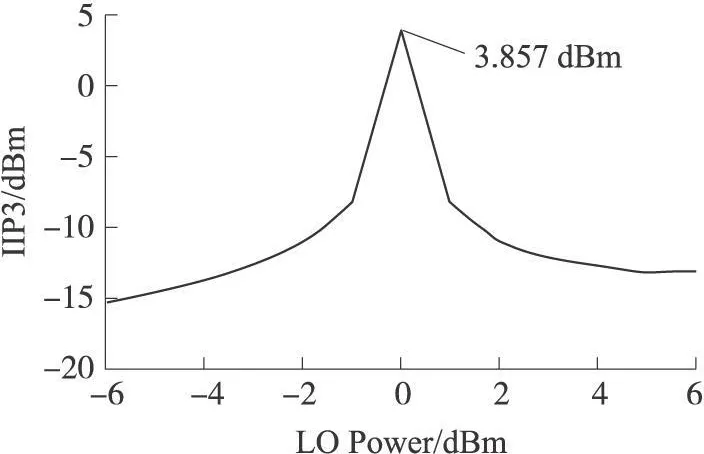

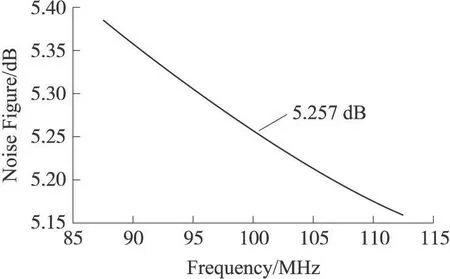

图3是三阶交调点(IIP3)随本振功率变化曲线,在本振功率为0 dBm时, IIP3达到最大值3.857 dBm。当本振功率大于或小于0 dBm时, IIP3都会急剧下降。图4是噪声系数(NF)和转换增益(Conversion Gain)随本振功率变化曲线,本振功率为-3 dBm时,噪声系数达最小值4.982 dB,本振功率为-5 dBm时,转换增益达到最大值11.23 dB。考虑到混频器的整体性能,必须采取折衷,所以选择本振功率为0 dBm,此时,噪声系数为5.257 dB,转换增益为9.787 dB。图5是当本振功率为0 dBm时,噪声系数随输出频率变化曲线,噪声系数随着输出频率的增加不断减小,在输出频率为100 MHz时,噪声系数为5.257 dB。

图3 IIP3随本振功率变化曲线

图4 NF与转换增益随本振功率变化曲线

图5 NF随输出频率变化曲线

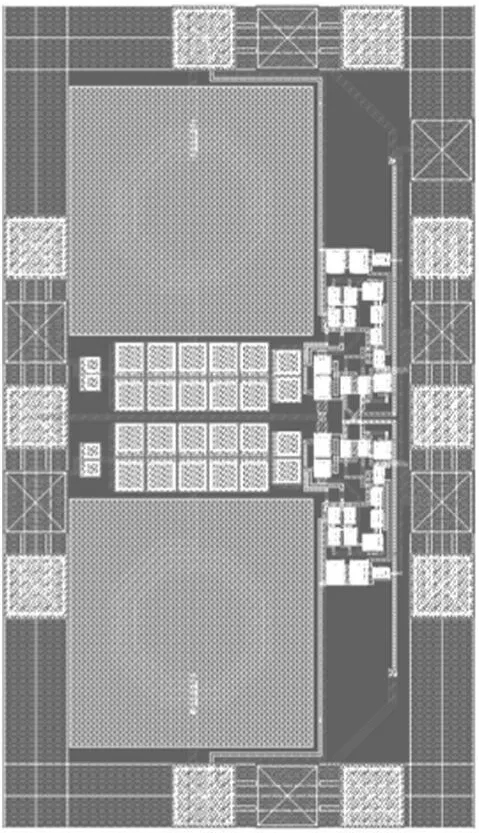

图6是该折叠混频器的版图,该版图用Cadence Virtuoso Layout editor进行设计及优化。 RF输入端的匹配网络与IF输出端的buffer都集成在了片内,版图面积556 μm×966 μm。

图6 折叠混频器版图

表1是本文设计的折叠混频器整体性能的仿真结果,并与其他发表的论文做了比较,可以看出该混频器具有高线性度,低噪声的优点。

表1 混频器性能总结与比较

3 总结

本文采用交流耦合互补跨导级成功设计了一种适用于低电源电压下工作的折叠混频器。仿真结果表明,该混频器具有高线性度、低噪声的优点。

[ 1] Gilbert B.A Precise Four-Quadrant Multiplier with Sub-Nanosecond Response[ J].IEEE Journalof Solid-State Circuits, 1968, 3(12):365-373.

[ 2]Lee T H, Samavati H, Rategh H R, et al.5-GHz CMOSWireless LANs[ J] .IEEE Transactions on Microwave Theory and Techniques, 2002, 50(1):268-280.

[ 3]BakiR A, El-Gamal M N.RF CMOSFully-Integrated Heterodyne Front-End Receivers Design Technique for 5 GHz Applications[ M] .IEEE Proceedings of the International Symposium on Circuits and Systems, 2004, 1:960-963.

[ 4]H YWang, K FWei, Lin JS, et al.A 1.2V Low LO-Power 3-5GHz Broadband CMOSFolded-Switching Mixer for UWB Receiver[ M].IEEE Radio Frequency Integrated Circuits Symposium,2008, 621-624.

[ 5] Krcmar M, Spiegel S, Ellingeer F, etal.A Broadband Folded Gilbert-Cell CMOSMixer[ M] .2007 14th IEEE International Conference on Electronics Circuits and Systems, 2007, 820-824.

[ 6]Reja M M, Moez K, Filanovsky I, et al.A Novel 0.6V CMOS Folded Gilbert-cell Mixer for UWB Applications[ M].IEEE International SOC Conference, 2008, 169-172.

[ 7]E P Hong, Y SHwang, H JYoo.Direct Conversion RF Front-End with a Low-Power Consumption Technique for 2.4 GHz ISM Band[ J] .IEEE, IET Microwaves, Antennas& Propagation,2008, 2(8):898-903.

[ 8] 刘乾坤.超宽带系统中CMOS直接下变频混频器的设计和研究[ D] .2007届硕士研究生论文.

[ 9] Vidojkovic V, Tang JD, Leeuwenburgh A, et al, A Low-Voltage Folded-Switching Mixer in 0.18-μm CMOS[ J] .IEEE Journal of Solid-State Circuits, 2005, 40(6):1259-1264.

[ 10] Krcmar M, Subramanian V, Deen M J, et al.High Gain Low Noise Folded CMOSMixer[ M] .1stEuropeanWireless Technology Conference, 2008, 13-16.

[ 11] Chen CH, Chianq P Y, Jou C F.A Low Voltage Mixerwith Improved Noise Figure[ J] .IEEE Microwave and Wireless Components Letters, 2009, 19(2):92-94.

[ 12] Karanicolas A.A 2.7-V 900-MHz CMOS LNA and Mixer[ J].IEEE Journal of Solid-State Circuits, 1996, 31(12):1939-1944.