基于FPGA的除法器设计

姚茂群,叶汉能,张立彬

(杭州师范大学 信息科学与工程学院,浙江 杭州 310036)

在FPGA得到广泛应用的情况下,应用过程中有时需要确定数据之间的具体倍数关系,因此很多公司针对自己的芯片开发了相应的除法器IP核.但是这些算法存在一些限制,比如要求除数是2的指数幂、运算数据为整数以及精度受到限制[1-2]等.在加、减、乘运算的设计已实现的情况下,要实现除法运算,可以有2种方案:将除法转换为乘法或采用减法与移位的组合[3].结合实际电路的情况,该文以二进制数为例,采用减法与移位的组合,设计一种通用且任意精度的二进制数除法器.整个设计、分析过程均在Altera FPGA EP1C6Q240C8环境下进行验证.

1 实现过程

以8位无符号数的除法为例,商根据所需精度设计相应位数.具体设计过程如下:

1) 设计9位数中间变量C,其高8位的初始值为“00000000”,最低位置入A的最高位数,然后将被除数A进行一位左移,最低位置入“0”;设计9位数中间变量D,将其最高位设置为“0”,低8位为被除数B.

2) 在时钟的上升沿,将C与D进行比较.如果C大于或等于D,则由高到低将商中相应的位置“1”,并用C减去D,将其差值重新赋予C;如果C小于D,则由高到低将商中相应的位置“0”.

3) 在时钟下降沿,C左移一位,最低位置入A的最高位;A左移一位,最低位置入“0”.在时钟上升沿回到2)过程.

以上2)和3)间的循环次数取决于需要得到的商的精度.

2 实现方式

图1 除法器模块图

该设计采用EDA的基本思想,分模块进行,主要包括移位模块、比较模块、减法模块,并将各模块进行整合,实现完整的除法器电路.各模块如图1所示.

2.1 移位模块

根据时钟信号对移位寄存器中的数据C进行由低位向高位的移位操作,并将被除数A的最高位置入寄存器最低位.对被除数A进行左移时,将其最低位置入“0”.

2.2 比较模块

根据时钟信号对输入数据进行由高位到低位的逐次比较,并将结果中大于和等于归为一类,输出相应的比较结果“1”,将小于归为一类,输出相应信号“0”.

2.3 减法模块

根据比较模块输出的信号控制减法模块的工作情况,从而实现只有在被减数大于或等于减数的时候进行运算.设计中运用将减法转化为加法的思路来设计适合该除法器的减法器.

该模块用VHDL描述如下:

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL ;

USE IEEE.STD_LOGIC_UNSIGNED.ALL ;

ENTITY MINUS IS

PORT (

CLK : IN STD_LOGIC ;

INPUTA, INPUTB : IN STD_LOGIC_VECTOR(8 DOWNTO 0);

S : OUT STD_LOGIC_VECTOR(8 DOWNTO 0)

END;

ARCHITECTURE ONE OF MINUS IS

BEGIN

PROCESS(CLK)

VARIABLE DB : STD_LOGIC_VECTOR(8 DOWNTO 0);

BEGIN

DB := (NOT INPUTB)+1;

设计意图: 在前面的构建模型环节只是简要地提出种群数量J型增长的条件,该环节以澳大利亚野兔泛滥的实例具体分析原因,归纳出种群数量J型增长的条件。

IF CLK’EVENT AND CLK=‘1’ THEN

S <= INPUTA + DB ;

END IF;

END PROCESS;

END;

该减法器RTL图如图2所示.

图2 减法器RTL图

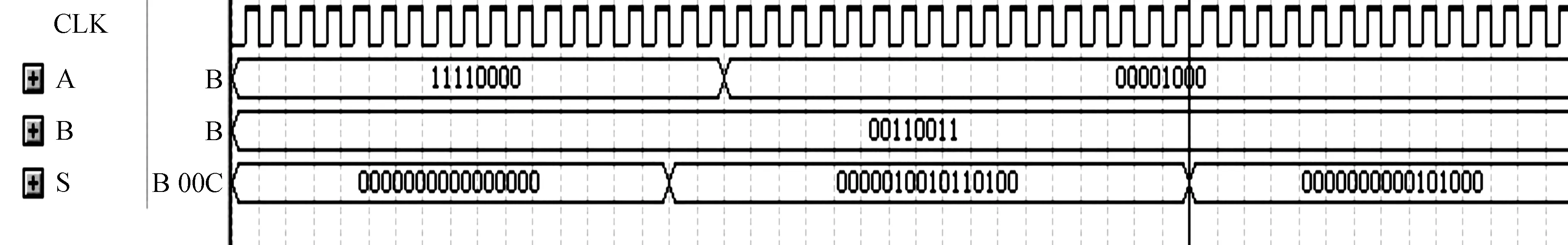

将以上模块整合,并要求商精确到二进制数小数点后面8位,用QuartusⅡ对除法器进行仿真,得到仿真波形如图3.

图3 除法器仿真结果

图3中A和B对应被除数和除数,S为商,且S高8位为整数部分,低8位为小数部分,图中除数为“00110011”,被除数或者除数的变化将触发除法器进行计算.当被除数是“11110000”时结果为“100.10110100”;当被除数是“00001000”时结果为“0.00101000”.可根据需要的精确程度来设置相应参数,控制循环变量和商位数,从而得到相应的商.

3 结 论

在已有的一些除法器设计中,较多采用的是结果带余数的办法,该设计是计算结果精确到小数的一种方法.由于减法操作中被减数和减数可能在最高位同时不为“0”,而且不够减,针对这种情况在设计移位寄存器时将其位数设计成比被除数和除数多一位,保证被除数在再一次移位时高位非“0”数据不会丢失.

设计过程中,仅涉及移位、比较和减法操作,原理简单,便于实现.采用VHDL语言编写,通过参数打包的办法[4],使得运用时能方便地实现可控精度的除法运算,增加了适用范围,具有较大的灵活性,便于移植.同时克服了部分除法器仅适用于除数是2的指数幂以及运算数据为整数等缺点,扩大了运算范围,提高了计算精度.

通过EDA的设计思想,采用VHDL语言对各模块进行描述,最后调用这些模块完成整个除法器的设计.对其结构和功能进行验证,结果表明其电路简洁、高效.通过控制循环变量和商的位数,可实现任意精度的除法计算,计算结果准确.

[1] 胡修林,杨志专,张蕴玉.基于FPGA的快速除法算法设计与实现[J].自动化技术与应用,2006,25(11):27-29.

[2] 陈玉丹,齐京礼,陈建泗.基于VHDL的8位除法器的实现[J].微计算机信息,2006,22(36):277-278.

[3] 郭松,徐世亮,万里勇.巧用数组实现除法的高精度计算[J].计算机与信息技术,2007,36:442.

[4] 雷伏容.VHDL电路设计[M].北京:清华大学出版社,2008:145-185.