基于AD9834的简易信号源设计*

张家田 王 华 严正国

西安石油大学 光电油气测井与检测教育部重点实验室 (陕西 西安 710065)

基于AD9834的简易信号源设计*

张家田 王 华 严正国

西安石油大学 光电油气测井与检测教育部重点实验室 (陕西 西安 710065)

采用模拟电路设计的信号源存在频率精度不高、调试与维修不方便以及直接升级困难等缺点。为了克服这些缺点,提出利用直接数字频率合成技术(AD9834)产生要求的正弦测井激励信号,利用小功率低压器件的串联实现信号的大功率大电压输出,利用电源跟踪技术在一定程度上降低功率器件的损耗,提高电路的工作效率。实验结果表明,信号源输出频率1~15 Hz,频率分辨率为0.004 Hz。

直接数字频率合成 功率放大 超低频信号源

目前使用的信号源大都是由运算放大器及其电子元器件如电容、电感及电阻组成的振荡电路产生,这些信号源电路存在结构复杂、参数固定、调试和维修比较困难以及频率精度不高等缺点[1]。直接数字频率合成技术 (Direction Digital Frequency Synthesis Technology,即DDS或DDFS)有相对带宽、频率转换时间快、相位连续性好及频率分辨率高等优点[2]。将DDS用于信号源的产生,不仅比传统振荡电路有更短的频率稳定时间和更高的频率分辨率,还可以实现信号源电路设计的软件化[3,4]。

基于DDS技术的信号源设计方案

信号源方案设计如图1所示。该方案主要由电源模块、液晶显示模块、键盘输入模块、外部通信模块、单片机控制模块、信号产生模块(DDS模块)、信号调理模块等部分组成。其中液晶显示模块显示信号源产生的波形、信号频率、信号幅度等参数;键盘输入模块可以手动输入待产生信号的频率、幅度以及波形等控制指令;外部通信模块与PC机连接,使得单片机可以接受PC机的控制,实时改变控制参数;单片机控制模块是整个信号源的控制中心,控制液晶显示模块、键盘输入模块、外部通信模块以及信号产生模块;信号产生模块接受单片机控制模块的指令,改变输出信号的波形、频率、输出幅度等;信号调理模块对产生的信号进行滤波、放大等处理,完成信号的输出。

信号产生原理及DDS技术

DDS的基本原理是利用采样定理,通过查表的方法产生波形。它以全数字技术,从相位概念出发直接合成所需信号。DDS系统电路结构由相位累加器、波形数据存储器、D/A转换器和低通滤波器组成,如图2所示。通过软件直接更改频率控制字K就可以改变信号源的频率,且能达到很高的频率分辨率;更改波形EPROM数据表的数据就能够产生不同类型的波形。因此,在设计信号源时,无需变动电路结构,只是通过设计不同的程序或更改不同的参数来实现。从而达到信号源设计软件化的目的。

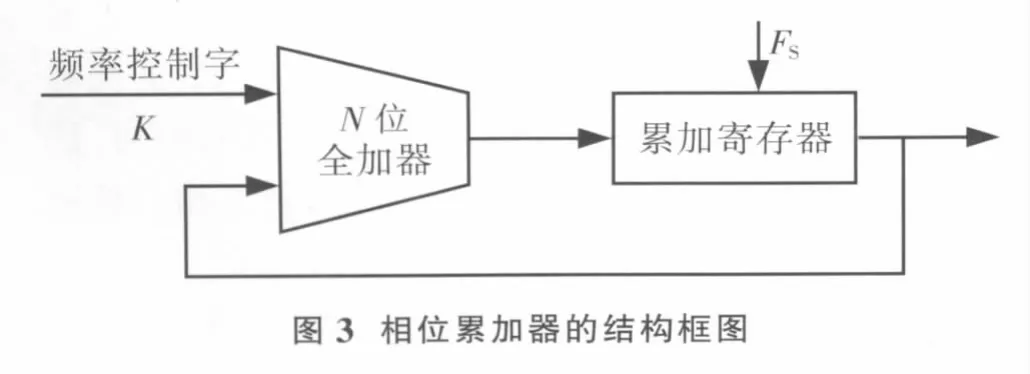

相位累加器由1个N位加法器与1个N位累加寄存器组成。对于每输入一个基准时钟Fs,加法器将频率控制字K与累加器馈入的相位数据相加,然后把相加后的结果送至累加寄存器的输入端。累加寄存器将加法器在上一个Fs作用后所产生的新相位数据反馈到加法器的输入端,以使加法器在下一个Fs作用时继续与频率控制字相加[5]。这样,相位累加器就可以不断地对频率控制字进行线性相加。同时相位累加器输出需要合成的相位信息,作为读波形数据存储器的地址。累加器的溢出频率,就是信号的频率。信号输出频率通过式(1)得到。

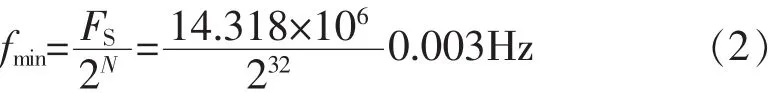

式中,FS为基准时钟,由振荡稳定的晶振产生;N为累加器位数;K为频率控制字。根据采样定理和实际应用情况,需要产生的信号频率不大于1/3FS。可以看出,在FS固定的情况下,可以通过改变K的值来改变输出频率的大小。累加器位数N决定了输出信号的频率分辨率。以FS=14.318MHz、N=32为例,则最小的频率分辨率为

相位累加器的结构如图3所示。

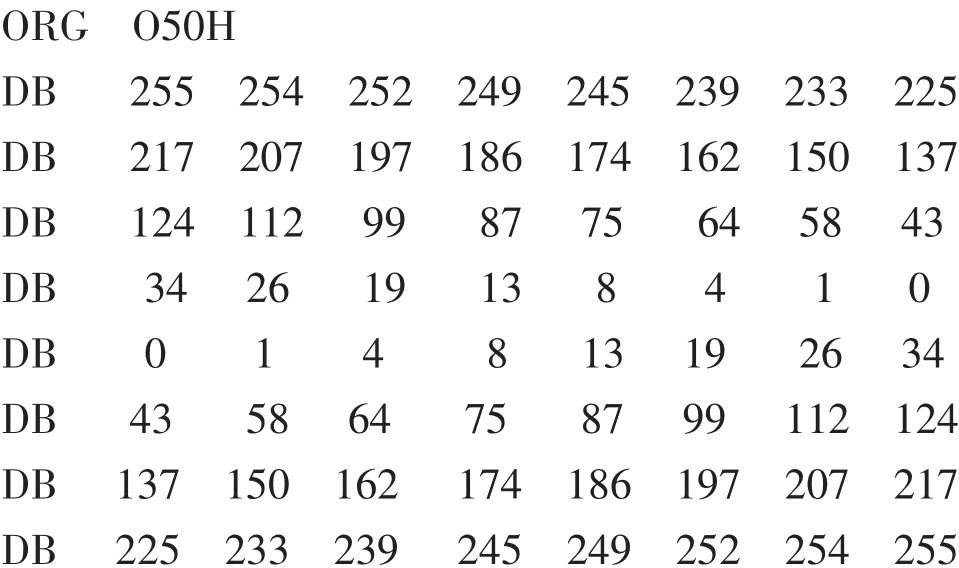

波形数据存储器存储了一个周期内的波形抽样数据,数据量的大小,取决采样的点数。一个周期正弦波信号如下:

采样点数为64,将这些数据编译后写入EPROM中。相位累加器的输出作为EPROM的寻址数据,经过查表,完成相位到幅度的转换。从EPROM中读出的二进制数据,经过D/A与低通滤波器,便得到所需要的正弦波信号。

1 DDS技术特点[6]

(1)高频率分辨率和相位分辨率。频率分辨率的高低与相位累加器、参考时钟频率有关,只要相位累加器的位数足够长,参考时钟频率合适,可以达到较高的频率分辨率。

(2)宽频率范围。根据采样定理,理论上DDS输出频率范围为0~0.5fc,其中fc是参考时钟频率。但实际上工程中可实现的DDS输出频率的上限为0.4fc。对于该设计来说,需要产生较低频率的信号,DDS可以完全满足。

(3)频率稳定度。DDS输出频率稳定度分为长期频率稳定度和短期频率稳定度。长期频率稳定度是指信号在规定外界条件下,在一定的时间(年、月、日)内工作频率的相对变化,它与所选用的参考源的长期频率稳定度相同。短期频率稳定度主要指各种随机噪声造成的瞬时频率或相位起伏,即相位噪声。为提高输出信号的频率稳定度,设计从以下方面考虑:首先DDS参考时钟源选用频率稳定度高的温补晶振或恒温晶振,选择性能优良的DDS芯片,其次增加电路的抗干扰设计等,从而在一定的程度上减少相位噪声,提高短期频率稳定度。

2 DDS设计模块

DDS模块设计框图(图4)。该模块主要完成控制命令接收、正弦信号生成、滤除信号噪声、信号输出放大等功能。该设计控制芯片采用C8051F020高性能8 bit单片机,DDS芯片采用AD公司生产的高性能AD9834DDS集成芯片。单片机与DDS采用SPI三总线接口,即串行时钟 (SCLK)、串行同步(FSYNC)以及数据(SDATA)三总线[7]。 AD9834 直接数字频率合成器是一款高性能、低功耗DDS芯片,内部集成10 bit的DAC、比较器等,能够产生高性能正弦波形、三角波形以及方波信号。为了产生高频率稳定度的信号,DDS采用恒温晶振,恒温晶振的稳定度在10~8量级以上,电路采用抗干扰设计,最大程度保证输出信号的频率稳定度。差分放大作用是将DDS输出的信号转换成单端输出,抵消输出信号的直流成分;低通滤波器实现对输出信号的滤波,滤除高频成分,该设计设置低通滤波器的截止频率为20 Hz。

AD9834的应用主要通过DSP的SPI口进行数据的写入。用户只要将数据写入控制寄存器即可。控制寄存器位功能如表1所示。

其中DB15、DB14为标志位,当DB15DB14=00时为控制寄存器,其它值时为选择频率寄存器或相位寄存器;DB13(B28)为配置数据写入的方式位;DB12(HLB)为控制写入寄存器的数据是低14位或高 14 位,和 DB13(B28)配合使用;DB11(FEL)为频率寄存器选择位,与DB9(PIN/SW)、管脚FSELECT配合使用;DB10(PSEL)为相位寄存器选择位,与DB9(PIN/SW)、管脚 PSELECT 配合使用;DB8(RESET)为复位位,与 DB9(PIN/SW)、管脚 RESET 配合使用;DB7(SLEEP1)为控制内部时钟位;DB6(SLEEP12) 为控制 D/A转换器电源位;DB5(OPBITEN)为控制方波输出位;DB4(SIGN/PIB)为控制内部比较器位;DB3(DIV2)为控制方波输出位;DB2为保留位必须设置为0;DB1(MODE)为控制输出波形位;DB0为保留位,必须设置为0。

3 DDS程序设计

表1 AD9834控制寄存器

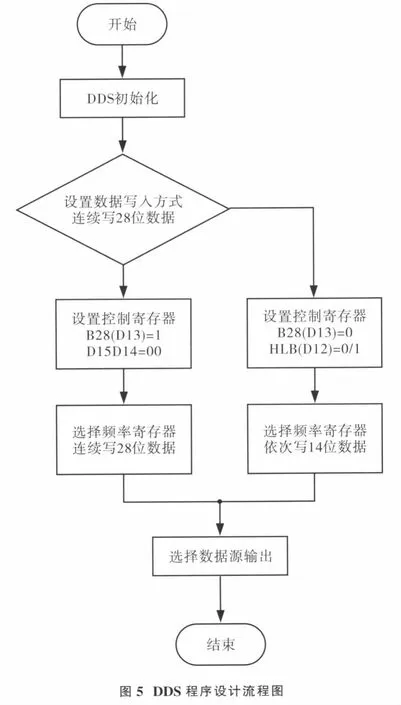

AD9834相位累加器为28位,当选择晶振频率为 1MHz时,输出信号的频率分辨率为:0.004Hz,减小晶振频率还可以进一步提高频率分辨率。以下以频率设置为例说明 DDS程序设计,程序设计共分为4个步骤:①计算要写入频率寄存器的值;②AD9834的初始化,复位器件内部寄存器;③写数据到控制寄存器,设置写入数据的方式,写数据到选择的频率寄存器;④选择输出信号的频率数据源,AD9834共两个频率寄存器,用户可以指定输出的数据源。具体DDS程序设计流程如图5所示。

实验结果

该信号源通过室内模拟试验装置测试,结果表明,信号源输出正弦频率1~15Hz,频率分辨率为0.004Hz,频率稳定度为±5×10~6/1h,输出电压范围为±300V,输出电流≤6A,输出功率为900W。通过模拟井实验,信号源指标能满足3 000m测井电缆的测井实验要求。

结 论

针对过套管电阻率测井技术的特点,提出利用直接数字频率合成技术产生要求的正弦测井激励信号,利用小功率低压器件的串联连接实现信号的大功率大电压输出,利用电源跟踪技术在一定程度上降低功率器件的损耗,提高电路的工作效率。该信号源是过套管电阻率测井模型机地面系统的一部分,已成功用于过套管电阻率测井技术的研究中,取得较好的试验效果。

[1]中国石油天然气集团公司测井重点实验室.测井新技术培训教材[M].北京:石油工业出版社,2004.

[2]吴银川,张家田,严正国.过套管地层电阻率测井技术综述[J].石油仪器,2006,20(5):1-5.

[3]王国庆,郭文广,陈文武.过套管电阻率测井数据处理及其在油气层评价中的应用[J].测井技术,2007,31(4):335-341.

[4]董军刚,蔡振江.基于DDS技术的智能信号发生器的设计[J].微计算机信息,2007,4(2):298-301.

[5]Singer B Sh,Fanini O,Strack K M,Tabarovsky L A, Zhang X.Measurement of Formation Resistivity Through Steel Casing[C]∥SPE 30628,1995.

[6]刘光辉.并行DDS频率源技术研究[D].成都:电子科技大学,2002.

[7]高吉祥.数字电子技术[M].北京:高等教育出版社,2003.

The signal source designed by the analogue circuit has some defects like the low accuracy of frequency,the inconvenience in debugging and maintaining,the difficulty of direct upgrade and so on.In order to overcome these shortcomings,it is proposed that the direct digital frequency syntheses technique (AD9834)should be applied to the production of the required sine logging exciting signals.It is also suggested that series devices of low power and voltage are used to the output of signals with high power and high voltage,and that power tracking technique should be adopted so as to lower the wastage of power devices and improve the working efficiency of circuit to some degree.The result of experiment shows that the output frequency of signal source is 1~15 Hz,and the frequency resolution is 0.004Hz.

the direct digital frequency syntheses;power amplification;ultra-low frequency signal source

��萍

2010-04-06

陕西省自然科学基金(2007D01);西安石油大学创新基金(YS28030533)