直放站回波消除器中数字抗混频滤波器的设计

李学易,郝禄国,卢晓锋

(1.广东工业大学 信息工程学院,广东 广州 510006;2.中国电信阳江分公司,广东 阳江 519500)

1 引言

在DVB地面数字电视和CMMB手机电视的应用中,直放站是提高无线信号覆盖范围[1]的必备设备。由于DVB/CMMB直放站是同频直放站,且DVB/CMMB发射频率一般为几百兆赫兹,下行方向存在直放站的发送天线到接收天线之间的回波(即信号反馈)干扰问题,工程上通常采用物理方法来提高收发天线之间的隔离度,但这种方法不能有效解决DVB/CMMB直放站的回波干扰问题,必须采用数字回波消除方法加以解决[2-3]。在DVB/CMMB数字回波消除直放站的研发中,关键的技术问题就是中频信号数字化后进行数字下变频抽取时出现信号频谱的混叠,数字抗混频抽取滤波器能很好地克服信号频谱混叠问题[4-6],这也是后面进行回波消除的先决条件。对几种抽取滤波器进行对比分析后,笔者提出一种有别于文献[7]中的新颖、高效、可靠的抽取滤波器的设计实现方法。

2 数字抗混频抽取器的基本结构[6-8]

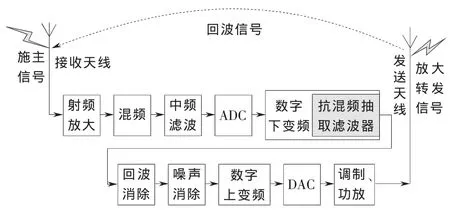

具有回波消除功能的DVB/CMMB数字直放站的整体设计原理如图1所示,笔者介绍的抗混频抽取滤波器(图1中的阴影部分)的设计会影响到后续回波消除及带内噪声消除的效果。

图1 数字回波消除直放站整体设计原理示意图

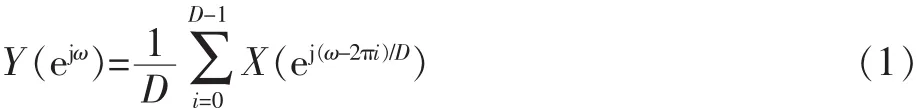

所谓抽取是指从原始采样序列x(n)中每隔(D-1)取1 个数据,形成一个新序列 y(m),即 y(m)=x(mD)。 设原信号 x(n)的频谱为 X(ejω),则抽取序列的频谱为

即 Y(ejω)是原序列频谱 X(ejω)先作频率的 D 倍扩张,然后按2π/D整数倍移位后的叠加和。由图2可知,当信号的带宽过大或者抽取倍数过高时,极易造成数字域频谱的混叠。所以有必要在抽取前进行抗混叠低通滤波,以防止发生混叠。抽取器的结构如图3所示。

图2 抽取前后(D=2)的频谱结构图

图3 完整的抽取器结构图

3 3种数字抗混频抽取滤波器对比

抽取滤波器也叫减采样滤波器,设计目的是为后续的处理模块提供符合要求的输入信号[6,8]。降低采样率在理想情况下应达到这样的效果:如果把输入信号x(n)看作是以频率fs对连续时间信号x(t)的采样,则理想抽取后的输出序列y(n)等于以频率为fs/L的采样率对原始信号x(t)进行采样所得的离散序列。典型的抽取过程包括2个步骤:首先是用带宽为π/L的理想抗混频抽取滤波器对x(n)进行滤波,使原始序列中只含有小于π/L的频谱的原始样本分量;然后再对滤波后的样本x(n)每隔(L-1)取1个数据,形成新序列y(n)。在实际应用中,理想的低通滤波器是不可能真正实现的,因而理想抽取也无法达到,但可以通过改进设计,得到对理想抽取的良好近似,因此抗混频抽取滤波器的设计十分关键。

3.1 FIR滤波器

有限长单位冲激响应(FIR)数字滤波器,可以设计成具有严格的线性相位,同时又具有任意的幅度特性。此外,FIR滤波器的单位抽样响应是有限长的,因而滤波器一定是稳定的。FIR滤波器在设计上较灵活,可以设计出理想正交交换器、理想微分器、线性调频器等各种网络。对于低倍的抽取,直接利用FIR来设计,在资源和速度上都可以达到较理想的效率。

3.2 半带滤波器(HBF)

HBF适合实现变换因子为2的抽取,是一种特殊的FIR滤波器。半带滤波器的阻带宽度与通带宽度是相等的,且通带、阻带纹波相等,即ωp=π-ωs,δp=δs。同时,n 为偶数的抽头系数值为0。半带滤波器的传递函数具有如下特性

3.3 级联积分梳状滤波器(CIC)

CIC滤波器结构简单,如图4所示。它没有乘法器和寄存器,是一种基于零极点相消的FIR滤波器,已经被证明是在高速抽取系统中非常有效的单元。

图4 N级CIC用于抽取器的实现原理图

抽取器左侧为积分器,右侧为梳状部分。在多级CIC抽取滤波器中,积分器工作在高频率fs,梳状器工作在低频率fs/D。

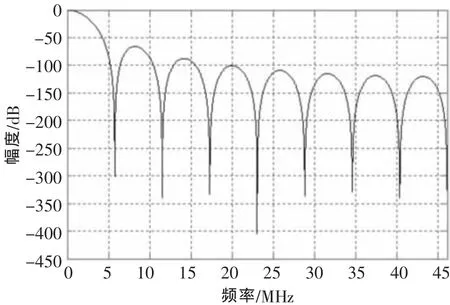

多级CIC滤波器的性能由3个参数N,D,M决定,如图5所示。但由于CIC的通带波动较大且阻带衰减较小,通常不能很好地满足设计者的要求。因此,一般要引入补偿滤波器,如直接幅度补偿、内插二阶多项式(ISOP)补偿和锐化的CIC滤波器等。

图5 D=16,N=5,M=1的 CIC 滤波器

4 数字直放站中3种滤波器的性能对比

4.1 CIC与FIR的性能对比

CIC滤波器虽然在速度上占优,但由于数字直放站数字下变频设计中仅采取2倍抽取,这需要CIC的过渡带非常窄,且通带最大衰减达到-10 dB以上,所以一定要使用补偿滤波器(比如ISOP),才能较好地遏制通带衰减问题,使频谱不失真。这样的话,会产生以下问题:1)由于增加了补偿滤波器,所以在FPGA上实现时硬件资源消耗增加了;2)对于CIC而言,通带衰减和阻带衰减就是一对矛盾,所以采取补偿滤波器对CIC进行通带补偿,肯定会减小阻带衰减,从而影响抽取抗混频的性能;3)由于CIC的通带衰减非常大,达到-10 dB以上,补偿后的滤波器在进行功能仿真时会产生较大的毛刺问题,滤波器性能变差。

对比直接采用CIC的方法,FIR滤波器存在以下优点:1)由于是在FPGA上实现,通过采用CSD编码和流水线结构,在速率上不成问题;2)代码设计简单明了,由于降低了总体程序体的复杂性,功能仿真后的毛刺较CIC低;3)一般而言,采用40阶以上的FIR可以实现-50 dB阻带衰减,滤波性能良好,可以很好地满足设计要求。对于40阶的FIR,其FPGA资源消耗肯定低于CIC加补偿滤波器的总体消耗。

4.2 HBF与FIR的性能对比

由于其结构上的特点,采用HBF会存在一些为0的滤波常系数,在理论上可以减少FPGA硬件资源的消耗。但用于数字直放站数字下变频设计时,会存在以下主要问题:1)由于HBF的结构问题,其过渡带会很宽,过渡带的宽度和滤波器常系数0点数是一对矛盾;2)由于HBF滤波器的通带宽度和阻带宽度必须相等,限制条件太多,灵活性差,用于数字直放站数字下变频设计时,还是会造成很大的FPGA资源消耗。

对比直接采用HBF的方法,FIR滤波器存在以下优点:信号经过ADC芯片中前级CIC或HBF滤波抽取后,采样速率相对来讲已经比较低。所以在一定的处理时钟下,可以采用更高阶的、灵活性好的FIR抽取滤波器,实现多级抽取的同时使其通带波动、过渡带宽、阻带衰减等性能指标能够设计得更优,从而满足滤波器特性的总体要求。

结合数字直放站数字下变频设计及回波消除器设计的实际情况,最终选取FIR滤波器来实现信号的抽取抗混频。

5 数字抗混频抽取滤波器的实现及仿真

本设计的开发、测试平台为FPGA+Matlab。图6为针对回波消除目的而设计的抗混频抽取滤波器的总体结构图。图7为部分仿真数据时序图。

图6 抗混频抽取滤波器总体模块结构图

图7 数据仿真时序图

本设计利用Simulator tool仿真器与Matlab相结合对基于FPGA的FIR滤波器进行仿真并验证设计的正确性。仿真验证方案结构如图8所示,激励信号由Matlab生成.mif文件,此激励信号的频谱如图9所示。将IP core配置成的ROM读入.mif文件,从而形成一个可用于FPGA的test_mif激励信号。编写代码调用test_mif来驱动echo_dvb_down硬件模块,通过Simulator tool进行仿真,仿真后保存生成.tbl文件,并利用Matlab画出其频谱图,如图10所示。与图9对比可以发现:设计的滤波器对高频信号具有很好的滤除效果,也直观地验证了滤波器设计的正确性。

图8 仿真方案结构图

图9 输入FIR滤波前的信号频谱图

6 小结

针对信号的混叠,对几种抗混频抽取滤波器(CIC,HBF及FIR)进行了深入的分析对比。根据数字回波消除直放站数字系统设计的实际要求,选取了FIR进行FPGA设计、仿真与验证。采用的FPGA+Matlab的设计方法,可以更直观、可靠地设计出符合设计要求的抗混频抽取滤波器,有效地减少开发周期。同时,在FPGA硬件设计上采用DA算法与CSD编码实现滤波器抽取系数的乘法,提高了运算速度,降低了资源消耗与芯片功耗。本设计加快了整个数字系统的开发效率,并为其他相关系统的研发提供了有益的参考。

图10 经FIR滤波后的信号频谱图

[1]SALEHIAN K,GUILLET M,CARSON B,et al.On-channel repeater for digital television broadcasting service[J].IEEE Trans.Broadcasting,2002, 48(2):97-102.

[2]KARIM M N,JOHN P C,MAURICE B,et al.Performance of an echo canceller and channel estimator for on-channel repeaters in DVB-T/H networks[J].IEEE Trans.Broadcasting, 2007, 53(3):609-618.

[3]HONG J, SUH Y, CHOI J, et al.Echo canceller for on-channel repeaters in T-DMB system[C]//Proc.ICACT 2008.Korea:[s.n.],2008,3:1735-1738.

[4]NEVES R F,FRANCA J E,MITRA S K,et al.Discrete-time N-path decimating filters[C]//Proc.ISCAS ′97.[S.l.]:IEEE Press,1997,4:2345-2348.

[5]NEVES R F,FRANCA J E.A switched-capacitor N-path decimating filter[C]//Proc.ISCAS ′98.[S.l.]:IEEE Press, 1998, 1:472-475.

[6]FABRICE L.Design and implementation issues in oversampled filter banks[C]//Conference Record of the Thirty-Sixth Asilomar Conference on Signals, Systems and Computers.[S.l.]:IEEE Press, 2002, 1:328-332.

[7]LIE I,TANASE M E, CARSTEA H C, et al.FPGA implemented decimating filter[C]//Proc.28th International Spring Seminar on Electronics Technology:Meeting the Challenges of Electronics Technology Progress.[S.l.]:IEEE Press,2005:229-235.

[8]HUANG D.The optimally reconstructed design of the causal stable synthesis filters in the M-band maximally decimated filter bank system[C]//Proc.ICNN&B ′05.[S.l.]:IEEE Press, 2005, 2:855-858.