8PSK全数字解调技术的实现

张 浩,张 彧,潘长勇

(清华大学 微波与数字通信国家重点实验室,北京 100084)

1 引言

调制方式8PSK能够提供更高的比特率和频带利用率,它在数据中继卫星通信、有线电视网络高速数据传输等领域得到广泛应用,并被数字卫星电视标准DVBS2采用。笔者对8PSK全数字解调算法进行研究,并采用Altera公司的FPGA进行硬件实现,结合实验室已经设计的8PSK调制器,完成了8PSK中频全数字解调。

2 8PSK解调的整体结构

本接收机实现方案见图1,接收到的中频信号直接经ADC采样,送入FPGA进行处理。采样信号在FPGA内先经过数字下变频(Digital Down Conversion,DDC),再送入时钟环进行时钟恢复,经过时钟同步信号送入载波环,对载波频差和相位差进行恢复,最后经过8PSK的解码映射、解差分译码,恢复出发射信号。

图1 8PSK数字接收机实现框图

3 数字下变频(DDC)

数字下变频由数字混频器、数字控制振荡器(NCO)和低通滤波器3部分组成,如图2所示。

图2 数字下变频

经过数字下变频后,得到数字基带信号,再经过抽取以降低数据速率,送入后续处理模块。抽取滤波器采用FIR滤波器,通过设置参数,可达到较好的通带特性和阻带衰减特性。

4 时钟恢复

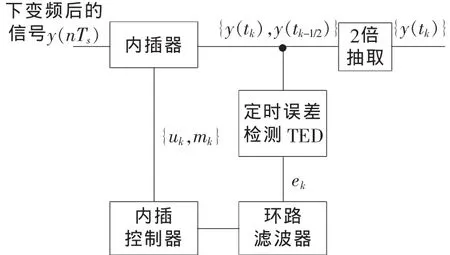

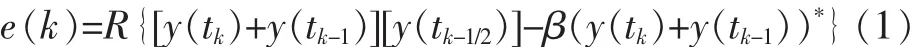

全数字接收机采用固定的采样频率,一般独立于调制端符号频率,这就需要采用数字信号处理的方法进行时钟恢复,从采样序列中恢复出最佳采样点的值。根据Gardner提出的理论[1],定时恢复可以由插值滤波完成(见图3),由内插器、定时误差检测器、环路滤波器、内插控制器等组成[2]。

采样时钟独立于发送端符号时钟,两者存在误差,定时误差检测器(TED)估算出此误差,经过环路滤波器后,送入内插控制器,通过控制内插滤波器,完成时钟恢复。

图3 定时恢复环路

Gardner在文献[3]中提出的定时误差检测算法,由于其结构简单易于实现,且独立于载波恢复,因此得到了广泛应用。然而其明显的缺点是对限带信号会产生定时抖动,所以对于8PSK信号,现实中采用文献[4]中提出的改进算法

定时误差信号通过环路滤波器进行滤波,提取出平稳分量。环路滤波器采用二阶滤波器,传递函数为

滤波器包括比例支路和积分支路,通过改变gp和gi来改变滤波器性能,将误差信号传递给控制器。

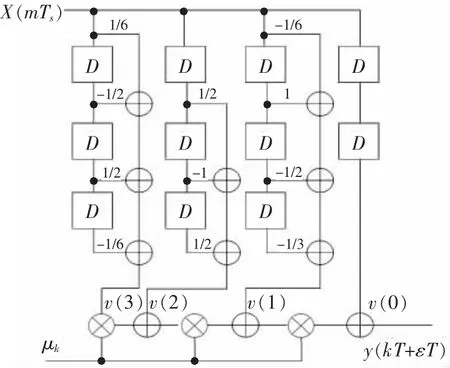

内插控制器根据定时误差信号估算出内插滤波器的控制量基本指针mk和分数指针uk,传递给内插滤波器。采样信号经过内插滤波进行速率转换,使输出信号周期Ti与调制信号的符号周期T同步,即 Ti=T/k,k是小的整数,现实中取k=2。插值滤波器采用多项式插值函数,用Farrow结构[5]实现。Farrow结构类似于FIR结构,具有固定的乘法器系数,同时又具有可变数字延时元素,是一种易于硬件实现的滤波器结构。对于拉格朗日三次多项式,有

5 载波恢复

图4 三次多项式插值滤波器的Farrow结构

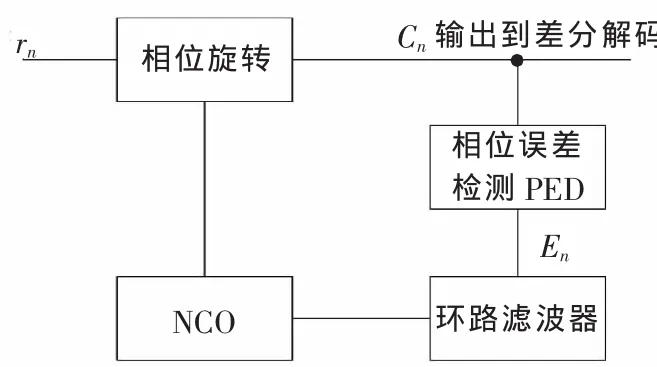

经时钟恢复的信号,送入载波环路,对载波频差和相位差进行估计和恢复。载波环路如图5所示,由相位旋转器、相位误差检测器、环路滤波器和NCO等组成。

图5 载波恢复环路

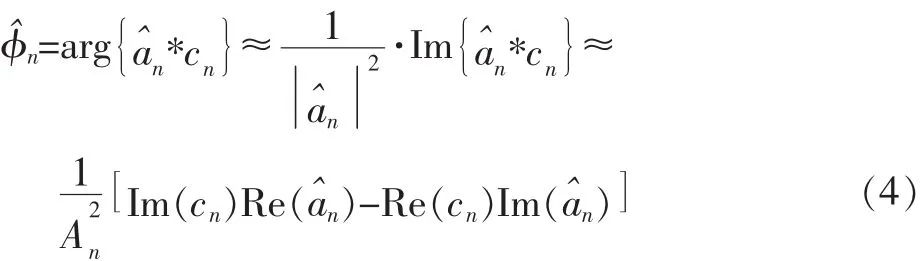

瞬时相位差φn估计由下式给出

连续2个采样点处的瞬时相位差之间的差值,可以用来表示对频率误差信号的估计,即

载波环应能完全纠正载波频差和相位差,因此需对式(5)进行修正,以较低的硬件复杂度完成频差和相位差的恢复,此时环路误差信号变为[6]

载波恢复的环路滤波器与时钟恢复的环路滤波器相似,数据位宽和具体系数按仿真有所不同。

NCO根据环路滤波器传递的环路误差En,累加计算出相位偏差ΔΦ,结合载波环工作频率,产生cos(2π/T+ΔΦ)和 sin(2π/T+ΔΦ),再送入相位旋转模块中,与接收到的信号相乘,纠正载波频差和相位偏差,从而获得两路基带信号。

8PSK载波恢复存在8重相位模糊度问题,因此加入了差分编解码。

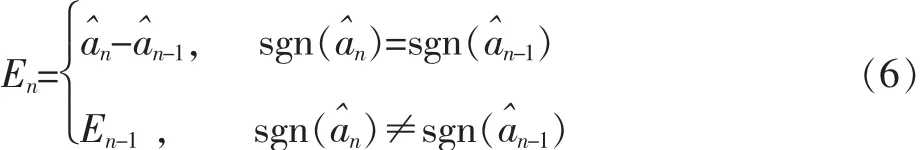

6 8PSK解码映射、差分解码

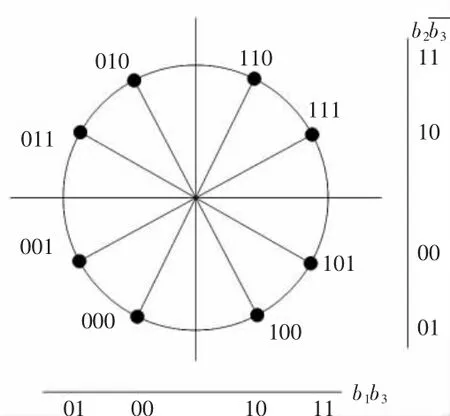

图6 8PSK正交调制星座图

在8PSK调制方式中,输入的串行二进制序列经串并转换,每次产生3位并行码组 b1b2b3。b1和 b3分别决定I路的极性和幅度,b2和分别决定Q路的极性和幅度,星座图如图6所示[7]。

经过时钟恢复和载波恢复后的I,Q两路信号,会因为一些原因(如信道衰落等)导致幅度的变化,只需根据I,Q两路极性和相对大小来判决接收到的信息,算法为

此时判决出的并行码组b1b2b3需要经过差分解码才能恢复出调制端发射序列。本方案8PSK的差分编解码采用文献[8]提供的逻辑运算。

7 FPGA实现结果

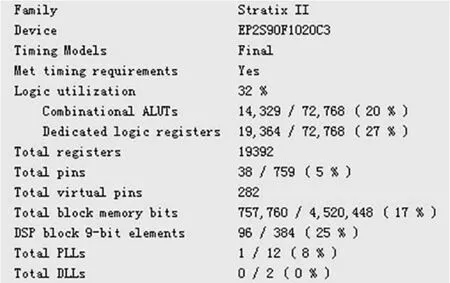

采用Altera公司Stratix II芯片实现,针对EP2S90F 1020C3进行程序设计。在Modelsim仿真通过后,采用Quartus II 8.0软件根据芯片内部各种资源和设计工具提供的优化功能,进行程序优化和硬件调试。

未加信道解码的8PSK数字解调器FPGA芯片占用资源如图7所示。

图7 8PSK数字解调器FPGA芯片资源占用

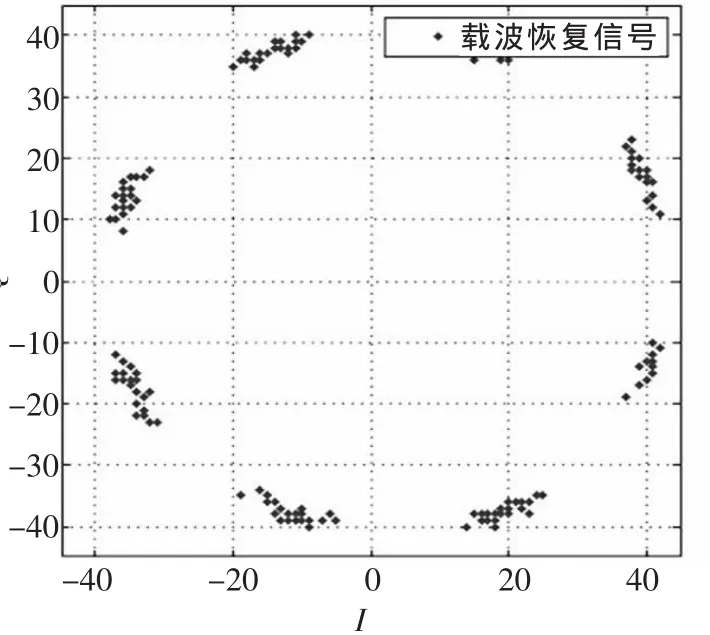

实验室8PSK调制器暂未加入信道编码模块。用电缆线将调制器和解调器环接起来,进行测试。Signal Tap是Quartus中提供的虚拟逻辑分析仪,在JTAG下载的同时,下载Signal Tap逻辑模块,采样片上信息并存储下来,通过JTAG接口传回计算机,在Quartus中显示。将载波恢复后的I,Q两路信号从Quartus中提取存为.txt文件,用Matlab画星座图如图8所示。由图8可以看出,8PSK解调后的星座点已经收敛为8个点。8PSK中频全数字解调器在功能上通过硬件实现,下一步需要根据不同应用,加入信道编解码、信道均衡、多普勒补偿等模块,使系统性能更优良。

图8 Signal Tap采样数据的星座图

[1]GARDNER F M.Interpolation in digital modems-part I:fundamentals[J].IEEE Trans.Commun., 1993, 41(3):501-507.

[2]MEYR H,MOENECLAEY M,FECHTEL S A.Digital communication receivers[M].New York:Wiley,1998.

[3]GARDNER F M.A BPSK/QPSK timing-error detector for sampled receivers[J].IEEE Trans.Commun., 1986, 34(5):423-429.

[4]LENG Weimin, ZHANG Yu, YANG Zhixing.A modified Gardner detector for multilevel PAM/QAM system[C]//Proc.ICCCAS 2008.[S.l.]:IEEE Press,2008:891-895.

[5]张公礼.全数字接收机理论与技术[M].北京:科技出版社,2005.

[6]LIU Qijia, YANG Zhixing, SONG Jian, et al.A novel QAM joint frequency-phase carrier recovery method[C]//Proc.IEEE International Conference on Advanced Communication Technology 2006.Phoenix Park,Korea:IEEE Press, 2006, 2(3):1617-1621.

[7]曹志刚,钱亚生.现代通信原理[M].北京:清华大学出版社,1992.

[8]冯重熙.现代数字通信技术[M].北京:人民邮电出版社,1987.