高速数字电路信号完整性问题分析与解决方案

董小军,陈 岩,杨忠孝

(1.电子科技大学自动化学院,四川 成都 610054;2.中国电子科技集团第30研究所,四川 成都 610041)

1 引 言

现在的集成电路中开关切换速度已经从几十赫兹增加到几百兆赫兹,甚至可以到达几个吉赫兹,所以,元器件和PCB板的参数、元器件在PCB板上的布局、高速信号布线以及电路的拓扑结构等因素,都会引起信号完整性的问题,导致系统不稳定甚至崩溃。因此,在高速电路设计中所面临的信号完整性问题已经成为高速电路设计者必须关心的问题之一。

2 信号完整性概述

信号完整性(Signal Integrity)是指信号在电路中以正确的时序和电压做出响应的能力。如果电路中信号能够以正确的时序和电压电平值做出响应,则没有信号完整性问题,反之,当信号不能正常响应时,就出现了信号完整性问题。信号完整性问题主要包括反射、串扰、地弹、振铃、时延等。

2.1 反射和串扰

反射由阻抗不匹配引起,阻抗不匹配可以由驱动源、传输线和负载的阻抗不同引起,也可以由传输线的不连续引起(如过孔)。反射会引起信号的振铃现象,如果过冲过大,会造成误触发。传输线末端端接阻抗与其特征阻抗不匹配,形成末端反射(负载端反射)。反射信号到达源端,若传输线源端阻抗与特征阻抗不匹配,将形成源端反射(第二次反射)。可以通过阻抗匹配的方式来消除反射的影响。匹配阻抗的端接有多种方式,包括并联终端匹配、串联终端匹配、戴维南终端匹配等。

串扰是指当信号在传输线上传播时,因电磁耦合对相邻的传输线产生的不期望的影响,在被干扰信号表现为注入了一定的耦合电压和耦合电流,过大的串扰可能引起电路的误触发,导致系统无法正常工作。PCB板层的参数、信号线间距、驱动端和接收端的电气特性以及端接方式对串扰都有一定的影响。不良的拓扑结构设计也会造成串扰的危害。

在Cadence的信号仿真工具中可以同时对6条耦合信号线进行串扰后仿真,可以设置的扫描参数有PCB的介电常数、介质的厚度、沉铜厚度、信号线长度和宽度、信号线的间距。仿真时还必须指定一个受侵害的信号线,也就是考察另外的信号线对本条线路的干扰情况,激励设置为常高或是常低,这样就可以测到其他信号线对本条信号线的感应电压的总和,从而可以得到满足要求的最小间距和最大并行长度。

2.2 振铃

振铃和地弹都属于信号完整性问题中单信号线的现象,信号的振铃由传输线上过度的电感和电容引起的接收端与传输线和源端的阻抗不匹配而产生的,通常发生在逻辑电平门限附近,多次跨越逻辑电平门限会导致逻辑功能紊乱。振铃可以通过适当的端接予以减小但是不能消除,电路中有大电流涌动时会引起地弹。一般信号完整性问题的解决办法有终端接地、以交流负载替换直流负载、使用上升时间缓慢的主动驱动源以及替换或重新布线等。通常在设计具体高速电路时候就要具体问题具体分析。

2.3 信号延迟

电路中只能按照规定的时序接收数据,过长的信号延迟可能导致时序和功能的混乱,在低速的系统中不会有问题,但是信号边缘速率加快,时钟速率提高,信号在器件之间的传输时间以及同步时间就会缩短。驱动过载、走线过长都会引起延时。必须在越来越短的时间预算中要满足所有门延时,包括建立时间、保持时间、线延迟和偏斜。由于传输线上的等效电容和电感都会对信号的数字切换产生延迟,加上反射引起的振荡回绕,使得数据信号不能满足接收端器件正确接收所需要的时间,从而导致接收错误。

3 Cadence工具的理解和使用

Cadence是全球最大的电子设计技术、程序方案服务和设计服务供应商,其EDA产品涵盖了电子设计的整个过程。Cadence SPB15.7是Cadence公司推出的EDA设计的软件,其系统互连设计平台能够跨IC、封装和PCB系统设计高性能互连,可以更好地帮助我们来解决信号完整性的问题。SpecctraQuest Interconnect Designer是Cadence公司为了满足高速系统和板级设计需要而开发的工程设计环境。它将功能设计和物理实际设计有机地结合在一起,设计工程师能在直观的环境中探索并解决与系统功能息息相关的高速设计问题。在进行实际的布局和布线之前,SpecctraQuest Interconnect Designer使设计工程师在时间特性、信号完整性、EMI、散热及其他相关问题上作出最优化的设计。这种统一的考虑不仅在单块板的系统中得到完美体现,更能在多块板构成的系统中,包括ASIC芯片、电路板、连接电缆、插接件等之间的连接进行分析。

在SpecctraQuest的参数设置环境中可以针对不同设计要求规定不同的约束条件。这些不同的约束条件可以通过参数分配表分配给电路板上不同的特定区域,或者分配给某一个信号组(Group),甚至具体到某一个网络。这些约束条件包括了范围广泛的物理和电气性能参数,如常见的PCB线宽、过孔数目、阻抗范围、还有峰值串扰、过冲特性、信号延时、阻抗匹配等。

4 拓扑结构的设计

在某通信系统项目设计中,采用了MIPS公司的OCTEON CN31系列CPU串联多个DDR内存设计控制电路。从器件供应商提供的IBIS模型中提取M.ibs文件,通过Cadence工具转换成M.dml文件,再由Cadence仿真软件将模型导入到器件中。经研究需设计8层PCB才可以满足设计要求,通过国内知名PCB厂家提供的印制板材料参数,调整PCB的每一层的物理厚度和走线层的线宽,使PCB各层上的走线的特征阻抗符合设计要求,以确保仿真结果的精确性。具体操作步骤如下:

(1)调整介质的厚度参数

(a)在 SPECCTRA Quest中选择 Setup->Crosssection或快捷按钮。

(b)这时会弹出Layout Cross Section对话框。此对话框中,可以添加或删除叠层,也可以更改每一层的类型、材料、厚度、电导率、介电常数、线宽、特征阻抗等参数。一般而言,PCB叠层的数量和顺序以及每一层的类型、材料、电导率、介电常数等已经确定了,需要按照给定的要求设置。而为了达到要求的特征阻抗,对于前仿真,一般调整的是线宽(一定的范围内)和介质厚度,对于后仿真,由于走线已经结束,能调整的主要就是介质的厚度。

(2)仿真参数的确定

在进行仿真前,需要对各种不同的仿真参数进行设定,以使仿真结果能够更精确地反映设计者的要求。当然,如果需要的话,仿真分析过程中也可以调整仿真参数。具体操作步骤为:

(a)在 SPECCTRAQuest中选择 Analyze->SI/EMI Sim->Preferences(或是在Sigxplore中选择Analyze->Preferences)。

(b)这时会弹出Analysis Perferences对话框。这里可以设置的参数包括器件模型参数、互联模型参数、仿真设置参数、单位、EMI参数和电源完整性参数等。其中常用的大致有仿真的周期数(Measurement Cycle)、时钟频率(Clock Frequency)、占空比(Duty Cycle)、偏移量(Offset)、固定仿真时间(Fixed Duration)、波形取样时间(Waveform Resolution)、截止频率(Cutoff Frequency)、仿真模式(FTS Mode)、驱动激励(Drive Excitation)、测量模式(Measurement Mode)等。一般可以使用默认值,个人根据自己的要求进行个别调整。

得到图1的参数,后计算得知差分阻抗100Ω,其单端阻抗50Ω。

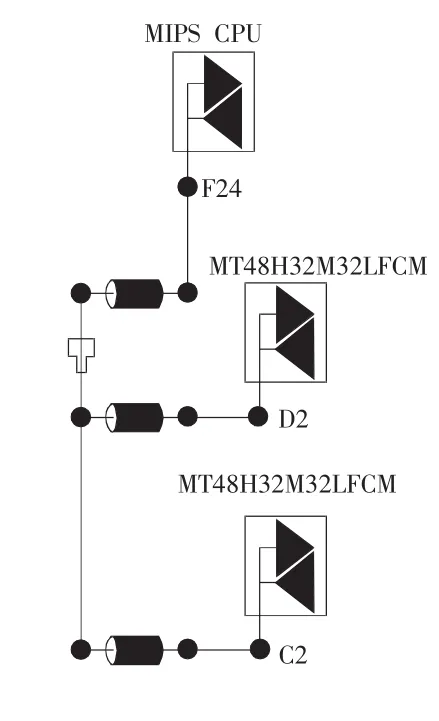

图2 菊花链管脚连接拓扑图

图3 菊花链40MHz时钟仿真波形

走线的拓扑结构是指走线的布线顺序及布线结构,当使用高速逻辑器件时,除非走线分支长度保持很短,否则边沿快速变化的信号将被信号主干走线上的分支走线所扭曲,会造成信号的串扰、反射,对电路产生十分明显的影响,为了满足信号完整性的要求,设计过程要对电路结构进行分析并通过合理的仿真选择合适的拓扑结构,通常情形下,PCB走线采用两种基本拓扑结构,即菊花链(Daisy Chain)布线和星形(Star)分布。提取传统的拓扑结构,如图2所示的菊花链,一根走线上串联多个专有芯片,对于菊花链布线,布线从驱动端开始,依次到达各接收端。如果使用串联电阻来改变信号特性,串联电阻的位置应该紧靠驱动端。在控制走线的高次谐波干扰方面,菊花链走线效果最好。

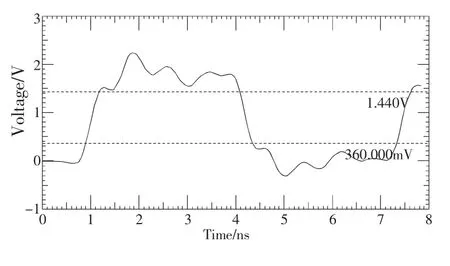

图4 菊花链120MHz时钟下的仿真波形

通过对Allegro PCB SI参数(如Pulse Stimulus、Simulation Parameters等)设置后,执行反射的仿真,在40MHz下反射仿真波形如图3,此时信号质量良好。

由于此项目设计中,时钟至少要120MHz以上,修改激励参数设置提高时钟频率至120 MHz,此时通过Cadence得到仿真波形如图4所示,信号边沿严格不单调,在实际电路信号采样中极有可能出现误采样,尤其在此高速电路设计,出现信号误采样就会严重影响系统正常运行,因此必须进行结构的改进。

对电路结构进行传统方式改进,如端接、阻抗匹配等,但都无法解决这个问题,仍然会出现图4中的信号波形,在此提出新的结构改进方式,进行等臂处理,改进拓扑结构。通过调整Net Scheduling对电路拓扑结构进行修改,使D2和C2到CPU总线的距离相等。改进后的拓扑结构如图5所示。

对修改后的电路进行反射仿真,得波形如图6所示。可以从图中看到的是,经过拓扑结构改进后,信号仿真波形明显好于处理前的信号波形,使信号边沿严格单调,消除了振荡等影响,满足实际电路需求。在设计完成后需再次对关键信号进行仿真,确保信号质量满足设计要求。

图5 调整后的拓扑结构

图6 调整拓扑结构后高速仿真波形

5 结束语

文中在Cadence下的反射仿真均是在实际的某通信项目中得出的结果,从结果对比中可以得知,采取合适的拓扑结构,可以很好地解决信号反射所带来的问题。但信号完整性问题是非常丰富和复杂的,必须对其进行全面充分的考虑,具体问题具体分析,综合各种方式,选取最合适的解决方式,及时尽可能提前地发现和解决电路板中信号完整性问题,避免重复制板,从而可以大大缩短设计周期,节约设计成本。

[1]HowardW,Johnson,Graham M.High-speed digital design:a handbook of black magic[M].The USA New Jersey Prentice Hall,1993.

[2]Bogatin E.Signal integrity:simplified[M].北京:电子工业出版社,2007.

[3]Brooks D.Signalintegrity issues and printed circuit board[M].The USA New Jersey Prentice Hall PTR,2003.

[4]Brooks.信号完整性问题和印制电路板设计[M].北京:机械工业出版社,2005.

[5]黄德勇,张 扬,杨云志.高速电路设计中的信号完整性研究[J].电讯技术,2004(2):149-152.

[6]曾 铮,郑建宏.高速PCB板设计中的串扰问题和抑制方法[J].电子设计应用,2006(4):81-84.

[7]孙宇贞.高速电路的信号完整性分析 [J].电子技术应用,2005(3):73-76.

[8]彭元杰.高速电路信号完整性分析[D].长沙:湖南大学,2007.

[9]曲 伟,刘 全.高速数字电路信号完整性设计[J].指挥控制与仿真,2006,28(3):106-116.

[10]周润景,袁伟亭.Cadence高速电路板设计与仿真[M].北京:电子工业出版社,2006.

[11]乔 洪.高速PCB信号完整性分析及应用[D].成都:西南交通大学,2006.