基于SOPC的嵌入式导航计算机设计

李良仁,汪临伟,彭雪峰

(九江职业技术学院 电气工程系,九江 332007)

0 引言

导航计算机是导航系统的核心部件,应具备较强的数据处理能力,以适应复杂的数据融合算法,保证导航实时性和精度要求,并要求在体积、功耗性等方面与系统环境相适应;本文以捷联导航系统为例,采用SOPC设计技术,对导航计算机硬件所需的数据处理、接口通信和控制软件进行设计,通过测试,系统的体积和功耗大幅降低,并满足捷联导航系统对空间的苛刻要求,同时片内设计可靠性提高;利用丰富的IP库,在FPGA逻辑资源中可根据导航系统应用场合对通信接口和信号采集功能的要求实现各种功能外设;在SOPC上选用高性能处理器,并在FPGA逻辑资源中硬件实现部分算法,形成软硬件协同的处理模式,可实现较好的实时性和较高的精度。

1 SOPC导航系统的整体方案设计

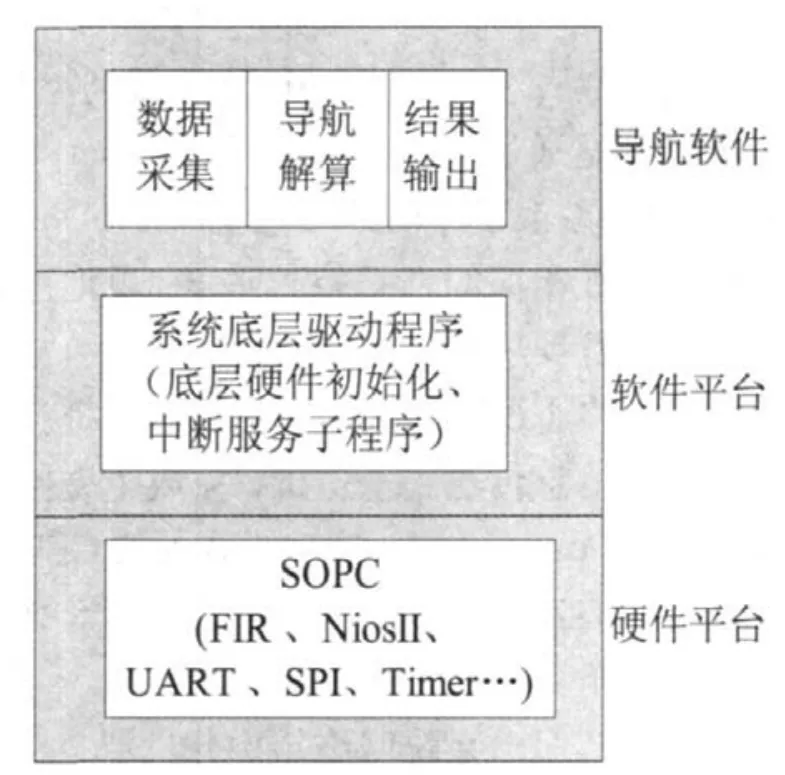

作为捷联导航系统核心部件的导航计算机负责从敏感元件获取导航原始数据,并进行捷联导航算法处理,最后将解算得到的导航结果进行输出控制。捷联导航计算机系统设计可由系统硬件平台、软件平台以及导航软件三个部分组成,具体设计方案如图1所示。

2 导航计算机硬件电路设计

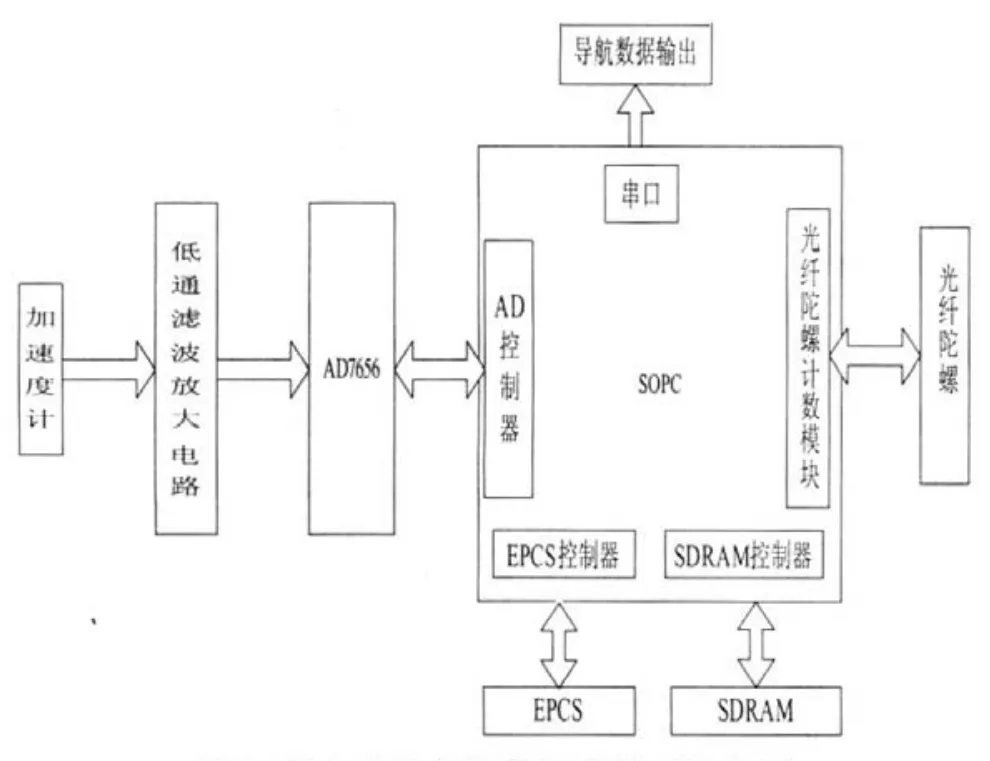

嵌入式导航系统的硬件可划分为四大部分,即惯性测量组件、数据采集电路、导航计算机和通讯接口部分。惯性测量组件包括光纤陀螺仪和加速度计两部分,主要用来测量敏感角速率和比力信息。数据采集电路是惯性测量组件和导航计算机之间的联系桥梁,为了能够保证系统正常工作,数据采集电路必须正确实时地采集到惯性器件的输出信号,并且要把这些数据以一定速率实时准确地传送给导航计算机。导航计算机是捷联导航系统的核心,系统中“数学平台”的建立、捷联解算工作及整个系统的管理和控制工作都由它来完成,采用FPGA芯片可以满足捷联导航系统要求高速运算和数据动态范围大的特点。根据以上分析,可以确定嵌入式导航计算机硬件系统框图,如图2所示。

图1 SOPC导航系统的整体方案

图2 嵌入式导航计算机硬件系统框图

在嵌入式导航计算机系统中,信号的采集和处理,导航解算都是通过在FPGA中嵌入NiosⅡ 软核处理器构成SOPC系统来实现。石英挠性加速度计传感器输出经过信号调理后送入A/D芯片转换成数字信号后通过FIR数字滤波后送入SOPC,光纤陀螺输出的脉冲信号经过脉冲整形后送入FPGA内用Verilog HDL 实现的硬件计数模块实现计数。

2.1 加速度计的数据采集电路设计

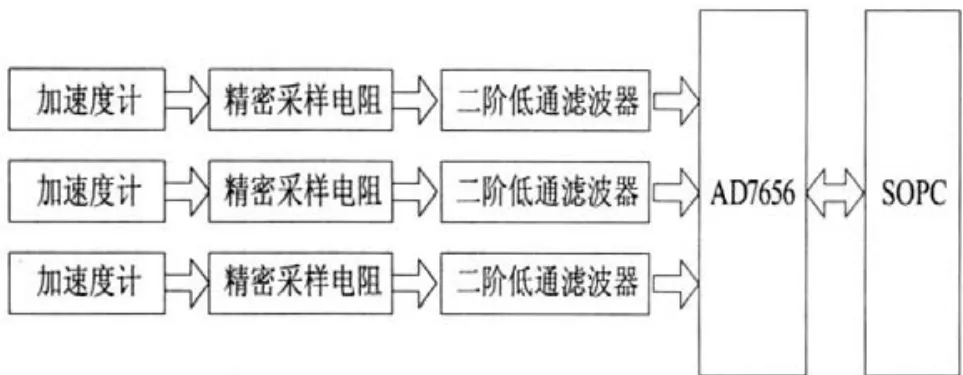

系统对惯性元件输出信号的采样频率直接影响了捷联解算的速度和精度,本系统每1ms采集一次陀螺和加速度计的数据,每10ms进行一次导航解算。基于上述因素,设计了快速高效的AD7656和FPGA的高精度加速度计接口电路方案,电路结构图如图3所示。石英加速度计输出微弱电流信号,经过精密采样电阻,转换成电压信号,以便于A/D转换,通过二阶低通滤波器滤掉高频噪声后,送入6通道并行转换的AD7656中,由FPGA控制AD转换,并读取转换结果,存储于内部缓冲区中,最终与陀螺仪的数据组合,进行数据处理和导航解算。它实际上是3个单通道的组合,可以满足不同精度,不同数字读出速度的要求,且相互之间电路干扰较少。为了保证三个加速度计的同步采样,采用同一器件的不同通道进行转换,以取得同样的读出速度。

图3 加速度计数据采集电路框图

2.2 光纤陀螺的数据采集电路设计

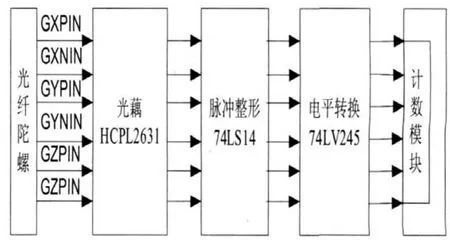

本设计采用国内某型全数字闭环保偏光纤陀螺,标度因数,分辨率,带宽200Hz,工作电流0.7A,其输出信号为脉冲信号,X、Y、Z各轴分别输出正反两路信号,即GXPIN、GXNIN、GYPIN、GYNIN、GZPIN、GZNIN,一定周期内正反信号脉冲个数的差值与标度因数相乘即为该轴向陀螺输出的角速度值。光纤陀螺的数据采集电路如图4所示。

图4 光纤陀螺的数据采集电路结构图

2.3 脉冲信号计数模块

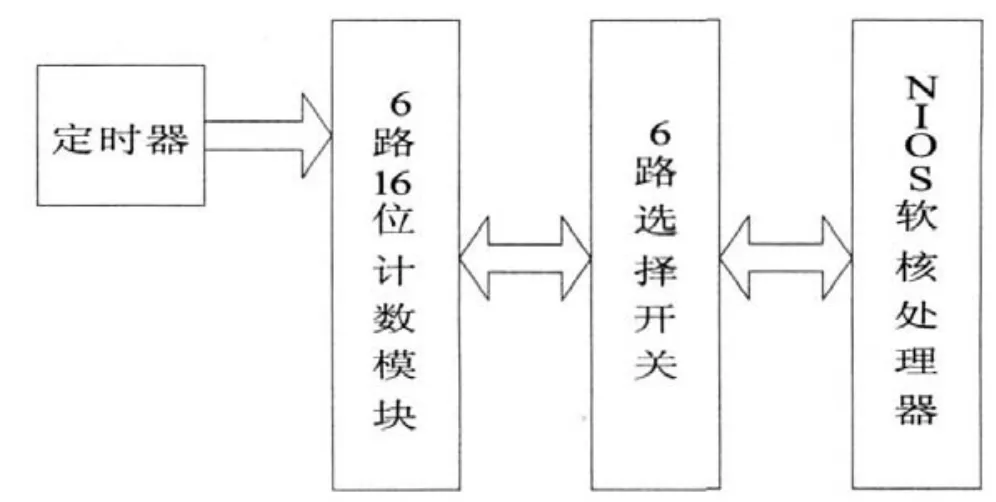

光纤陀螺的脉冲信号经过前端处理电路后进入计数模块,本设计在FPGA内部用Verilog HDL语言编写计数器模块,实现在规定时间内记录每路信号的脉冲数。计数模块内部包括16位计数器,定时器,六路选择开关。由于系统采样频率设为1000Hz,因此定时器的定时中断设为1ms。该模块能对六路脉冲信号同时计数,通过Nios II软核处理器的I/O口对其控制,确保对光纤陀螺计数的准确性和实时性。光纤陀螺脉冲计数的原理框图如图5所示。

图5 光纤陀螺脉冲计数原理框图

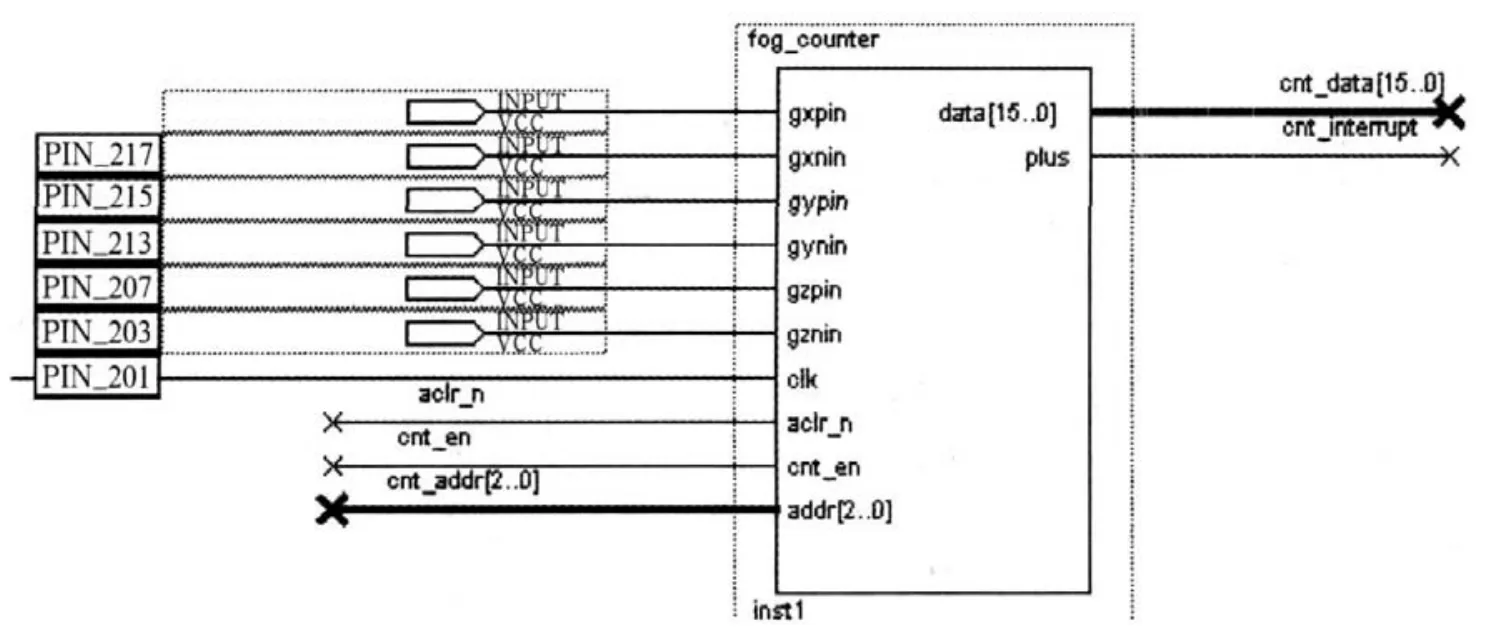

通过用Verilog HDL语言分别编写上述各单元的功能模块,然后在上层文件中例化,编译后生成的文件符号如图6所示,引脚定义如下:

GXPIN、GXNIN、GYPIN、GYNIN、GZPIN、GZNIN:光纤陀螺输入脉冲信号;

图6 光纤陀螺信号接收计数器

aclr_n:计数器清零使能信号;

cnt_en:计数器计数使能信号;

clk:时钟信号;

cnt_addr[2..0] :六路信号选择输出信号;

cnt_data[15..0] :数据输出;

cnt_interrupt:定时中断输出信号;

3 导航计算机软件设计

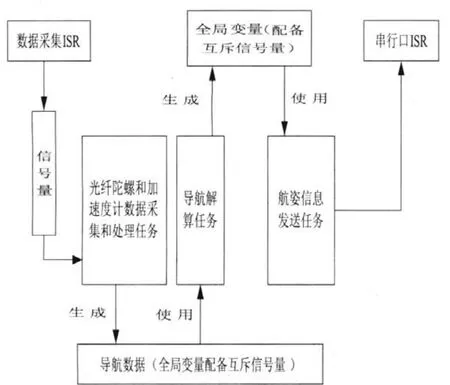

导航计算机的实时性和可靠性要求很高,采用嵌入式实时操作系统设计导航计算机软件。由于Nios II IDE已经移植好了uC/OS-II,再加上uC/OSII小巧、源代码公开、注解详细、实时性强、可移植性好、多任务、基于优先级的可剥夺型调度的特点,选择它作为嵌入式导航计算机的软件运行环境。光纤陀螺捷联导航系统应包含三个ISR(光纤陀螺数据采集ISR、加速度计数据采集ISR和串口发送ISR)和4个任务:“初始化任务”、“数据采集任务”、“捷联导航解算任务”、“串口发送任务”。光纤陀螺和加速度计采集的数据经过滤波处理后分别用一个全局数组来存储,供导航解算任务使用,并配备了一个互斥信号量。导航解算任务生成的数据存储在全局数组变量中,配备互斥信号量,串口通信任务根据接收到的指令发送导航信息。系统总体任务关联图如图7所示。

图7 系统总体任务关联图

在本系统中的4个任务设计中,初始化任务创建其余的三个任务,因此优先级最高,设为8,陀螺和加速度计的采样是关键任务,优先级设10,导航解算任务优先级设为12,串口通信任务设为14。在本设计中,因为要用到两个互斥型信号量,所以必须为这两个互斥型信号量分配优先级,这个优先级要高于所有申请互斥信号量的任务优先级,分别设为5,6。本系统中的4个任务的声明如下:

void initial_task(void *pdata); //初始化创建任务,优先级8

void fog_task(void *pdata);//陀螺计数和加速度计采样任务,优先级10

void calc_task(void *pdata); //导航解算任务,优先级12

void scom_task(void *pdata); //串口发送任务,优先级14

在以上任务中,initial_task()为一次性任务,创建完其它任务后自行删除,其他任务都是周期性任务。

4 结束语

通过对整个系统与三轴转台进行软硬件联合测试,测试结果表明该系统在姿态、位置、速度误差都控制在1%以内,具有很高的实用价值。使用SOPC方法在FPGA上设计嵌入式导航计算机,其软硬件协同的设计模式适合了捷联导航系统对处理能力和接口能力的要求,具有很强的应用价值和应用前景。

[1] 陈哲编.捷联惯导系统原理.北京:宇航出版社,1986.

[2] 龙达峰.基于SOPC技术的弹载组合导航系统的应用研究[D].中北大学,2008.

[3] 李兰英,等.Nios II嵌入式软核处理器SOPC设计原理及应用[M].北京:北京航空航天大学出版社,2006.