S3C2440开发板在某型雷达中的应用

王立彬,周 衡

(1.总装备部武汉军代局驻3303厂代表室,湖北武汉430200;2.中国兵器装备集团武汉滨湖电子有限公司,湖北武汉430077)

S3C2440开发板在某型雷达中的应用

王立彬1,周 衡2

(1.总装备部武汉军代局驻3303厂代表室,湖北武汉430200;2.中国兵器装备集团武汉滨湖电子有限公司,湖北武汉430077)

介绍了S3C2440开发板搭载某型号内存在XXX-HA雷达开发中的应用,并对该型号开发板内存初始化过程进行了研究,提出了该系统的最优化设置方案。

雷达;S3C2440;内存;初始化

通讯系统和传输系统是雷达的关键组成部分之一。通讯分系统由两个通讯分机和通讯电缆组成。每个通讯分机均由三块通讯板组成。通讯板是较为容易出现问题的部分。其主要表现在数据传输中,有时会出现延时,传输误码率高,通讯板死机的情况偏多等。主要原因是:1)CPU和内存选型不合理,在通讯分系统数据处理量大时,系统运行在高负荷状态下,发热量大,易导致数据传输延时或死机。2)通讯板工作在强电磁环境下,由于前期设计时未能对硬件进行充分优化,导致通讯板受外界干扰时易发生故障。

XXX-HA设计数据处理量为同系列上一代产品的4倍以上,对通讯板的要求更加苛刻。因此,在对通讯板的开发方面,可从系统成熟度和性能方面综合考虑,选择了S3C2440嵌入式平台进行系统设计。

S3C2440采用了较先进的ARM 920T内核,集成了通讯所需要的网卡接口与CAN总线接口。此CPU上能运行Linux2.6嵌入式操作系统,这样避免了使用非开源系统造成的系统安全性和保密性方面的担忧。程序的编译,使用的是自行研制的嵌入式交叉编译工具,而并没有使用现成的交叉编译工具,这样能够更进一步的保证系统的安全与可靠性。

采用海天雄电子生产的成品S3C2440嵌入式开发板作为程序开发的平台,确定程序版本稳定之后,对电路进行了相应裁剪,只留下保障系统运行的基本部分,这样能使系统消耗的资源最少,功耗尽可能的低。

在系统的Bootloader选择方面,使用 uboot-1.1.6。选择U-Boot的理由主要有:1)开放源码。2)完善的支持Linux嵌入式操作系统内核。3)支持ARM处理器系列。4)较高的可靠性和稳定性。5)高度灵活的功能设置,适合 UBoot调试、操作系统不同引导要求、产品发布等。6)丰富的设备驱动源码,如串口、以太网、SDRAM、FLASH、LCD、NVRAM、EEPROM、RTC、键盘等。7)较为丰富的开发调试文档与强大的网络技术支持。

在内存的选型方面,由于该成品S3C2440开发板上所使用的内存型号为K4S561632E-UC7,工作温度为0~70℃。而根据XXX-HA研制任务书要求,该通讯板工作温度为-40~100℃,因此选用可以满足该标准的XX公司生产的XXX-BU型军用级内存芯片。

由于更换了内存芯片,内存芯片的更改导致了电气特性如内存工作时序上相关时间特性的变化。为了进一步分析硬件的工作方式,使其既发挥了应有的性能,又工作在稳定可靠的状态。对这套系统内存初始化的代码进行了一系列研究。

1 时钟频率的分析

由于内存对时钟的频率有一定要求,时钟频率对内存产生直接影响。因此在对内存进行初始化之前,u-boot-1.1.6在start.S处对时钟频率进行了一个比例上的初始化,相关语句如下:

/*FCL K∶HCL K∶PCL K=1∶2∶4 */

/* default FCL K is 120 M Hz!*/

ldr r0,=CL KD IVN

mov r1,#3

str r1,[r0]

CLKD IVN寄存器存放了 FCL K,HCL K,PCL K三个不同时钟频率之间的关系。这个寄存器被设为3时,查询相关手册[1]可得到,UCL K=UPLL,HCL K=FCL K/2,PCL K=HCL K/2,即FCL K∶HCL K∶PCL K=1∶2∶4(见表1)。

表1 不同时钟频率之间的关系

通过查CL KD IVN值的初始值表得知,初始值全部为0,进一步查上表,得出 FCL K∶HCL K∶PCL K=1∶1∶1。更换开发板上的内存组件后,开始进行试验板的制板。在晶振的选型时,由于开发板自带晶振为12M Hz,但源代码中的一句注释"/* default FCL K is 120 M Hz!*/"对fclk的描述给元器件选型工作带来了疑问。

在S3C2440手册上提示:“大家都清楚,在开启电池与重起的过程中,PLL是不稳定的,所以这个时候,实际上是由Fin这个时钟代替了M p ll,给FCL K提供了时钟频率。一直到有软件重新设置PLLCON 寄存器。”[1]因此 ,可以看出 ,默认的FCL K是频率,是与Fin频率是一致的,直到有软件重新设置了 PCCLON寄存器。如果这里 Fin的频率是 120M Hz,那么就应该选用频率为120M Hz的晶振。

但实际上,CPU的频率是由MPLL来生成的,而 M PLL又是由 Fin、MD IV、PD IV、SD IV 计算出来的。这里的值,都有一个范围,并不是仅满足相应的公式就可以,为了减少计算的麻烦,S3C2440手册[1]给出了一个可供参考的各个数值的大小的列表(表2),即推荐使用的值。

表2 参考数值

从表2中可看出,当输出的时钟频率为405.00M Hz的时候,Fin为12M Hz。这里的值,就是Fin的频率值,也即默认的FCL K值。由于:

1)S3C2440以ARM 920T为核心,可以运行在200M Hz至533M Hz之间,但是400M Hz左右是保证其稳定运行时速度最快并且发热量可控的结合点,所以一般将CPU的频率定在405M Hz。

2)Fin的频率越低,所实现这个Fin的代价就最小,消耗的能量就最少。

根据以上两点,可以判断:使用这组数值为设置该系统的最佳方案,也是最常用的方案。

这里默认的FCL K的值为12M Hz。因此,可以采用频率为12M Hz的晶振。

2 内存时序的分析

u-boo t-1.1.6中内存时序的设置是在low level_init.S中进行的。为了正确设置XXXBU型内存,首先对开发板自带的 K4S561632EUC7内存进行分析。

根据S3C2440手册中第5章内存控制的说明[1],可以看出,内存是被映射在0x30000000-0x40000000的位置,即 bank6与 bank7。在内存时序设置时,主要关注bank6与bank7。

当M T的值为0x3(11bin)时,表示使用的是SDRAM,所以B6_M T与B7_M T的值为0x3。

当bank6与bank7为 SDRAM的时候,只需要设置 Trcd与SCAN的值。

1)Trcd值的确定。

通过查阅手册得知FCL K最大的频率值为400M Hz,HCL K最大为133M Hz,PCL K最大为67M Hz,而内存方面,是由 HCL K来控制的。那么经过简单的计算就可以知道,内存的一个时钟周期,最短为7.519ns。

K4S561632E-UC75数据手册[2]中 Trcd的内存最少需要20ns。如果Trcd为2clk,则时间不够,所以只能为3clk。如果最短的时间都能满足,那么当内存工作在比133M Hz低的情况下,就更加能够满足,所以这里的 Trcd为3clk。

2)SCAN的值的确定。

K4S561632E-UC75内存,地址组织形式为16M x 16,这个形式的内存地址的Co lum n A ddress为(CA 0~ CA 8),即9bit,内存参数[2]见表3,所以值为0x1。

以上各项参数都设置完成后,SDRAM的内存就能够被正确初始化。

从整个内存初始化的过程可以看出,系统在初始化内存的时候,尽可能的利用了内存的硬件性能,把延时做到了尽可能地小,这种设置方式下,内存可以在完全被有效地利用,保持在较为稳定的工作状态。

表3 O rderintg Info rmation

3)对XXX-BU型内存的设置。

在了解了 K4S561632E-UC7内存的初始化原理与步骤后,根据XXX-BU型内存的用户手册,对内存进行合理地初始化,并设置各项参数。

XXX-BU型内存 Trcd值为0x00,SCAN 0x01的值不变。由此可见新型号内存响应速度更快 ,为 2clk。

其相关设置源代码为:

#define B6_M T 0x3/* SDRAM */

#define B6_Trcd 0x0

#define B6_SCAN 0x1/*9bit*/

#define B7_M T 0x3/* SDRAM */

#define B7_Trcd 0x0/* 2clk */

#define B7_SCAN 0x1/*9bit*/

3 优化设置后开发板的可靠性验证

完成上述初始化后,我们根据开发板制作了通讯板试验样机。根据《研制任务书》和相关标准对其进行了相关试验验证,并与上代产品进行了纵向比较,其结果如下。

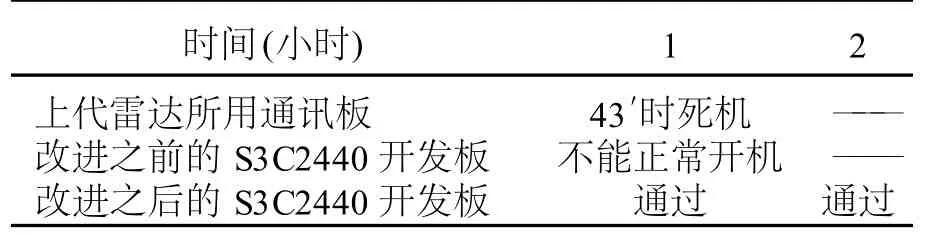

1)常温状态下满负荷工作。在环境温度19℃,相对湿度52%的条件下相关试验见表4。

表4 常温状态下满负荷工作

2)高温状态下满负荷工作。在环境温度60℃,相对湿度11%的条件下相关试验见表5。

表5 高温状态下满负荷工作

3)常温状态下传输误码率测试。在环境温度60℃,相对湿度11%,运行12小时的条件下相关试验见表6。

表6 常温状态下传输误码率测试

比较分析以上3个测试,可以看出进行了重新设计和内存初始化配置的S3C2440实验板,在系统运行稳定性方面,有着很大提升;同比上代产品,也有明显进步。

[1] S3C2440中文手册[ED/OL].[2010-03-25].http://wenku.baidu.com/view/2baafb1ea76e58fafab00357.htm l.

[2] K4S561632E-UC75[ED/OL].[2010-03-25].http://wenku.baidu.com/view/ee0d5f75a417866-fb84a8e25.htm l.

Application of S3C2440 in a Radar System

Wang Libin1,Zhou Heng2

(1.Military Representative Office of Factory 3303,Wuhan Military Delegate Bureau of Genera l Armament Ministry,Wuhan,Hubei 430200,China;2.Wuhan Binhu Electronics Co.,Ltd.,China South Industries Group Corporation,Wuhan,Hubei 430077,China)

This paper introduced the application of memory chip of S3C2440 evaluation board in XXXHA radar system,analyzed the memory initialization process,and proposed a best initialization solution.

radar;S3C2440;memory chip;initialization

TP333

A

1671-2544(2010)06-0058-04

2010-05-14

王立彬(1983— ),男,湖北广水人,总装备部武汉军代局驻3303厂代表室工程师。周 衡(1980— ),男,湖北广水人,中国兵器装备集团武汉滨湖电子有限公司工程师。

(责任编辑:陈锦华)