基于FPGA的小型无人机通信干扰系统设计与实现

摘 要:针对无人机快速发展带来的黑飞无人机、无人机扰民等问题,以直接式数字频率合成为技术原理,提出一种基于通信干扰的无人机干扰系统,选择现场可编程门阵列作为核心芯片,设计无需镜像抑制算法和滤波器的双边带发射干扰硬件结构。相关测试验证了本系统的可行性和有效性。

关键词:直接式数字频率合成;无人机;通信干扰;系统设计;现场可编程门阵列

中图分类号:TN972" 文献标志码:A" 文章编号:1671-5276(2024)05-0122-04

Design and Implementation of Communication Jamming System for Small UAV Based on FPGA

Abstract:To deal with the problems such as unauthorized UAV and UAV disturbing people due to the rapid development of UAV, according to the technical principle of direct digital frequency synthesis, proposes a UAV jamming system based on communication jamming. Field programmable gatee array is selected as the core chip to design a dual sideband jamming emitting hardware structure without image suppression algorithms and filters. And the feasibility and effectiveness of the proposed system is verified by relevant tests.

Keywords:direct digital frequency synthesis;UAV;communication jamming;system design; FPGA

0 引言

现在许多领域都需要使用无人设备进行探索,随着无线电技术的发展,使得无人机的身影随处可见,如利用无人机来运送快递、无人机的灯光秀表演、无人机灾后搜救等。但与此同时也带来许多问题,且存在一定的危险,如无人机飞入禁飞区域、无人机产生的噪声扰民、利用小型无人机运送毒品等。因此如何对无人机进行精准有效管控是迫切需要解决的问题。

目前对无人机的应对措施主要有物理摧毁和捕捉,如用石头打击、发射捕网弹进行捕获;利用激光枪直接击落无人机;利用声波攻击无人机的陀螺仪,使其飞行紊乱等。相较于对无人机进行通信干扰,其他方法局限性大,管控效果不高[1]。

无人机干扰技术是基于通信信号干扰原理,对无人机无线通信传输过程进行干扰,使无人机通信不稳定甚至中断。现有的无人机干扰系统或者干扰手段复杂,或者系统设计不合理而达不到预期的干扰效果[2]。鉴于此,本文在了解无人机干扰技术的研究背景、应用现状及发展方向后,提出了基于直接式数字频率合成(direct digital frequency synthesis,DDS)的无人机干扰系统,通过STM32和现场可编程门阵列(field programmable gate array, FPGA)芯片,在上位机发送指令,动态地生成所需的双边带干扰信号,对无人机的通信链路进行干扰,使得无人机无法正常飞行,最终降落或者悬停。

1 无人机干扰技术原理概述

无人机通信链路是无人机通信系统中最为重要的一部分,它是无人机能否正常飞行的关键。根据信号传输的方向,将无人机的通信链路分为上行链路和下行链路。下行链路是信号从无人机传输到地面控制系统或无线控制设备的方向,上行链路是信号从地面控制系统传输到无人机的方向。上行链路的安全性和稳定性对无人机至关重要,若未能接收到信号或接收到错误的信号会使无人机丢失目标甚至被敌方控制[3]。

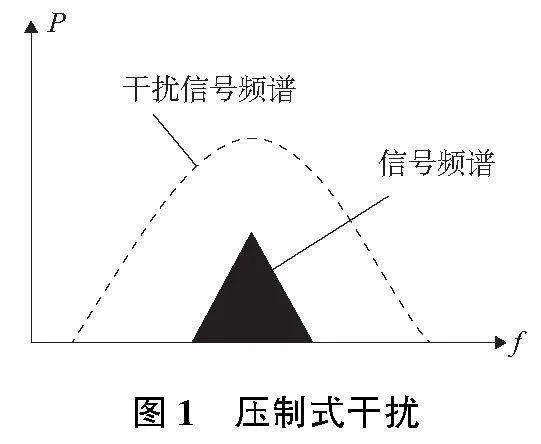

通信干扰的最佳干扰形式就是发射的干扰信号能够完全压制住敌方信号的无线通信。如图1所示,压制式干扰技术的原理是通过发射大功率信号压制目标通信信号,具体可以分为对无人机遥控信号的干扰和对无人机定位GPS信号的干扰,在进行信号干扰时,通过定向增益天线向目标发射无线电信号来实现干扰[4]。

2 系统分析与设计

随着FPGA的出现和不断发展,基于直接数字式频率合成原理,与传统硬件化信号发生器的整体设计不同的是,在FPGA上开发高性能的多种波形信号发生器,成本更低,操作更加灵活简便,可以根据需求进行更新配置,系统开发趋于软件化和自定义化[5]。

2.1 信号生成基本原理

本文所用方案的信号生成模块以FPGA芯片为基础,由无源晶振产生FPGA的时钟信号,使用Verilog HDL硬件描述性语言并基于DDS原理,初步实现信号生成的功能。具体来说,是通过MATLAB软件生成的目标信号以一定频率采样后存入FPGA ROM的IP核中,根据对无人机干扰的需要,选择生成的信号主要有噪声调幅信号、噪声调频信号、窄带高斯白噪声信号、线性调频信号、多音干扰信号。

如图2所示,输出目标信号频率为f0,输入系统时钟频率为fc,频率控制字为M,相位累加器的位宽为n,ROM中存储所需目标波形一个周期的2N点(N≤n),取相位累加器高N位作为地址对ROM进行寻址[6],满足以下关系:

2.2 系统设计

FPGA作为系统的实现核心,其性能直接决定了DDS系统的性能。综合考虑FPGA的速度和性价比,最终选用SPARTAN-6系列的XC6SLX16,STM32选用STM32F030C8T6。

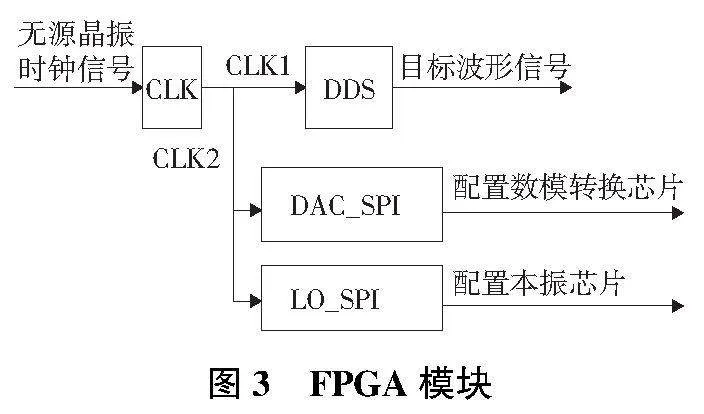

通过MATLAB软件生成所需信号,采样率与无源晶振产生的320 MHz时钟频率一样,采样1 024点存入FPGA的ROM IP核后,在ISE14.7软件上用Verilog HDL使FPGA综合实现DDS功能,选择相位累加器32位,取其高10位对ROM进行寻址,频率控制字为4 194 304。如图3所示,根据芯片手册,编写好数模转换芯片和本振芯片的配置文件,在CLK2下建立FPGA芯片与数模转换芯片和本振芯片的SPI通信,先读取高八位芯片寄存器地址,再读取低八位对该寄存器进行写入[7]。

如图4所示,接着实现上位机、STM32、FPGA之间的通信。上位机选择串口助手,在Keil软件对STM32进行编程烧写,调用对应的库函数,设置波特率,失能硬件流,实现上位机与STM32的串口通信。配置STM32的引脚,并在FPGA实现与STM32的SPI功能,实现STM32与FPGA的通信,最后构建三者的通信连接,使得上位机发送指令后经STM32传输到FPGA[8]。

图5所示为系统的总体设计,上位机发送特定指令,STM32将其转化成FPGA能接收的形式,FPGA根据指令生成的对应干扰信号和配置完成的本振芯片产生的信号混频到对应频段,经放大器放大后由天线发射至目标无人机。

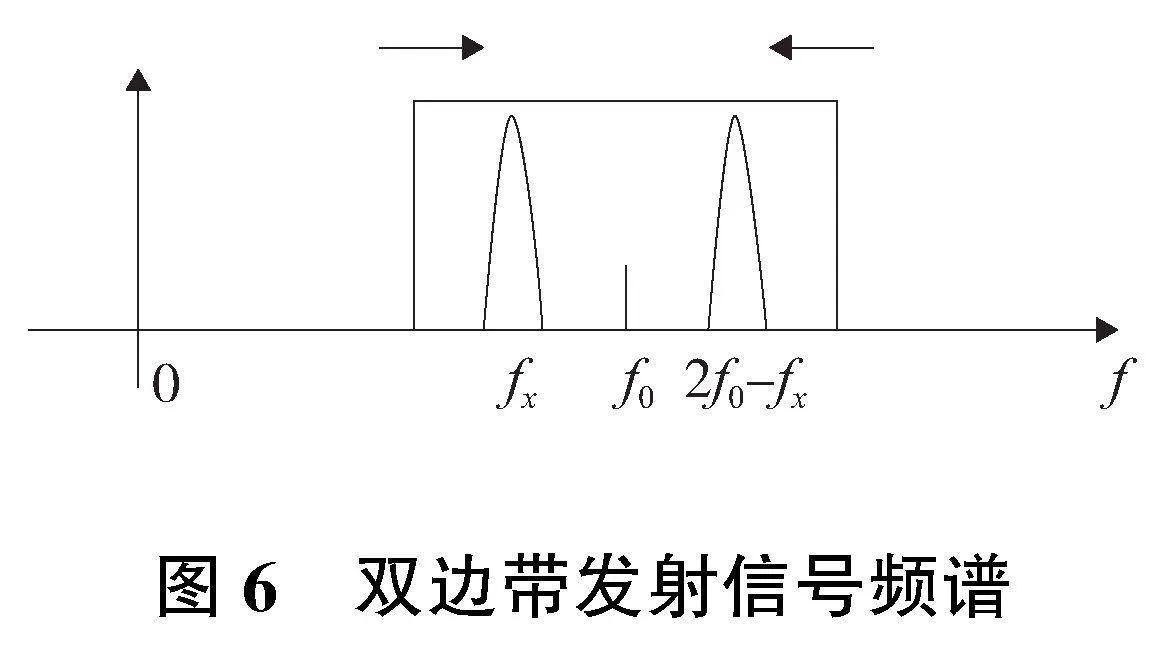

对无人机进行压制式干扰的信号一般为宽频带信号[9],因此对于镜像抑制的需求并不大,选择双边带发射,使得生成信号从本振左右两边开始同时扫频,相较于单边带发射只有一半带宽而言,生成信号的速度更快,且能量都在所需的干扰信号带宽内,无浪费功率,实现的硬件结构更简单,成本更低。

一线性调频信号和本振混频得到的理想信号频谱如图6所示,fx为信号频谱中在载波f0左侧的某一频点,相应会存在另一频点2f0-fx在载波f0右侧,此两频点关于载波f0对称。在干扰信号传输过程中,即使有一边带受到衰减,另一边带也能保证干扰效率[10]。因此干扰效果更佳。

3 系统测试

选用常用的民用无人机,本无人机干扰系统根据无人机GPS频段1 575.42 MHz、遥控频段2.4 GHz,配置本振芯片LTC6948,生成上述信号经过AD9122数模转换后混频成在无人机目标频段带宽100 MHz的双边带干扰信号,并经过放大器及定向天线发射,对无人机进行干扰,图7和图8所示为在频谱仪上呈现的信号。

如表1所示,选择干扰对象为无人机精灵4pro2.0,干扰频段为1 575.42MHz,设置干扰源与无人机的垂直距离为100m,水平距离为1 500m。不同干扰信号有不同的干扰效果,设定相应的信源通道功率和功放通道功率,所生成的噪声调幅信号、噪声调频信号、带限高斯白噪声信号、线性调频信号由于频谱能较大范围覆盖GPS信号,干扰距离可达1 503m,具有较好的干扰效果。而多音干扰信号仅能作用目标频段特定频点处的信号,干扰效果不佳[11]。

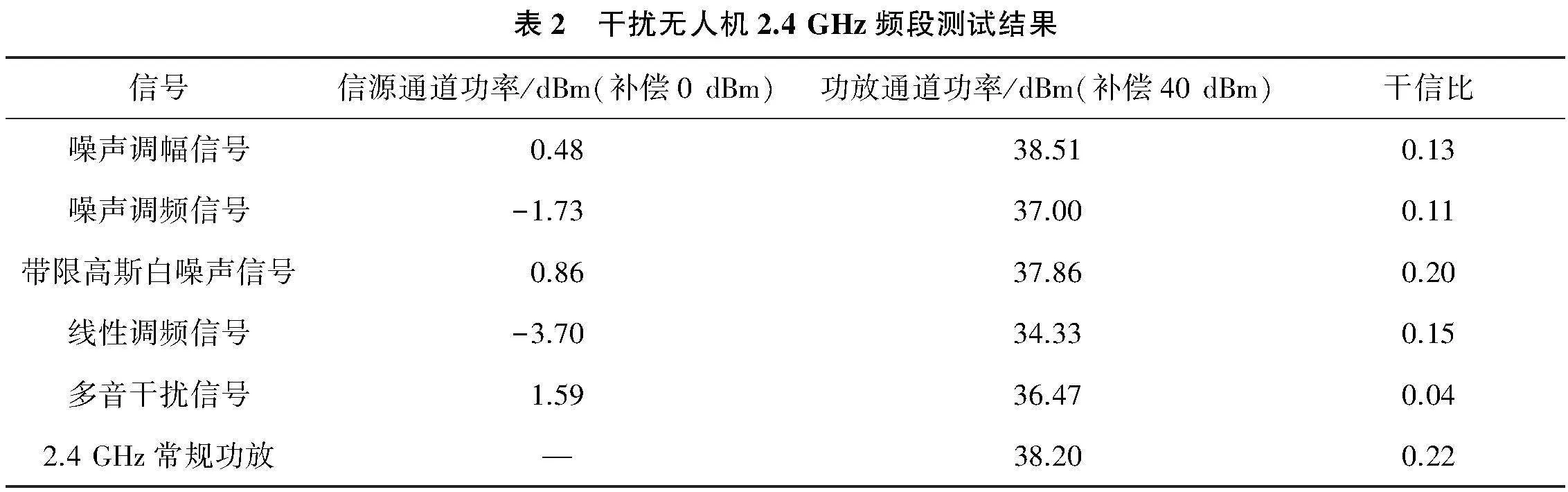

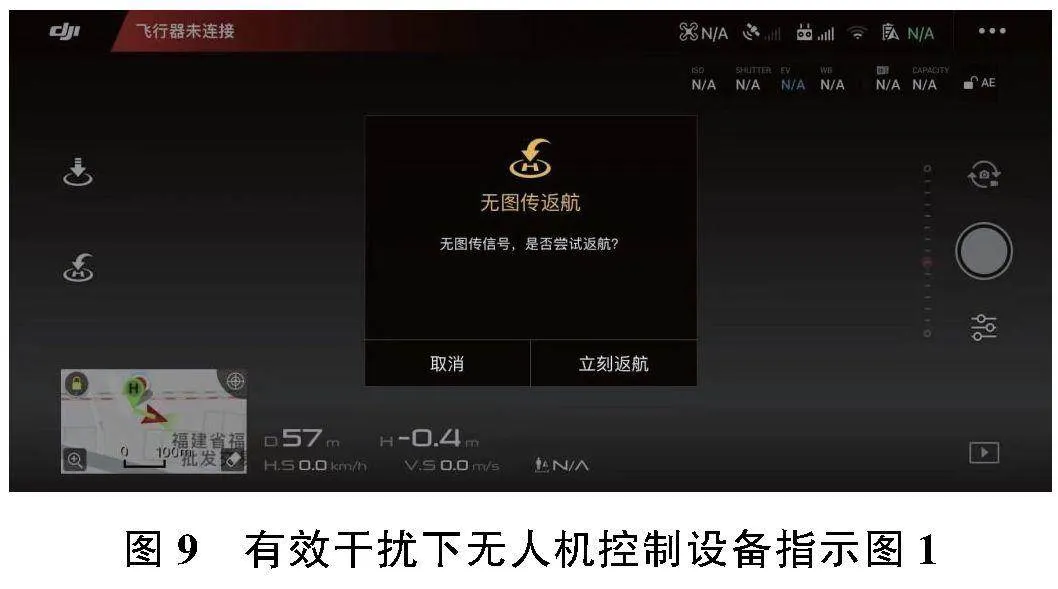

如表2所示,干扰频段为2.4GHz,设定相应的信源通道功率和功放通道功率,测试干扰信号与无人机通信信号的功率比,以2.4GHz常规功放的干信比为基准,带限高斯白噪声信号的干扰效果最佳,其次是线性调频信号、噪声调幅信号、噪声调频信号,最差是多音干扰。图9、图10所示为在有效干扰下无人机遥控设备指示信息。

4 结语

本文针对市面上主流小型无人机的控制技术,提出了对GPS信号和遥控信号通信链路进行有针对性的压制式干扰的硬件设计结构,并且对方案的可行性进行了论证及测试。相关测试结果表明:本文的无人机干扰系统可根据需要生成1 575.42MHz、2.4GHz频段的干扰信号对无人机进行干扰,给无人机干扰系统的设计提供了有益的思路和方向。

参考文献:

[1] 李佳朋. 小型无人机通信干扰系统的研究[D]. 北京:北方工业大学,2021.

[2] 杨勇,张雪涛,张星昱,等. 小型无人机通信干扰器设计[J]. 河北工业大学学报,2017,46(3):23-28.

[3] 程擎,伍瀚宇,吉鹏,等. 民用无人机反制技术及应用场景分析[J]. 电讯技术,2022,62(3):389-398.

[4] 黄志忠,梁桂全. 一种小型无人机干扰器设计[J]. 电声技术,2020,44(10):65-67.

[5] 杨东霞,巨永锋. 基于FPGA和DDS的数字调制信号发生器设计与实现[J]. 电子设计工程,2013,21(6):90-93.

[6] 薛海峰. 浅析软件无线电收发信机中DDS技术的应用[J]. 通讯世界,2019,26(6):76-77.

[7] 夏港东,秦浩杰,王庆东,等. 基于FPGA的非接触式张力监测系统的设计[J]. 机械制造与自动化,2022,51(2):195-198,222.

[8] 李亚柯,黄永福,陈镇山,等.一种基于FPGA的信号源:中国,202123429600.4 [P]. 2022-05-27.

[9] 冯伟坡. 小型民用无人机无线电反制技术研究[D]. 西安:西安电子科技大学,2020.

[10] 朱泽坤. 无人机通信干扰系统前端研究[D]. 成都:电子科技大学,2018.

[11] 何道敬,杜晓,乔银荣,等. 无人机信息安全研究综述[J]. 计算机学报,2019,42(5):1076-1094.