D—BLAST基带系统的FPGA实现研究

黄虎+孔勇+李华+孙乐

【摘 要】设计了适合于现场可编程门阵列实现的多输入多输出系统的对角分层空时码编译码算法。采用Verilog硬件描述语言在Xilinx Virtex4-VC4VSX55现场可编程门阵列开发板上实现了3×3对角分层空时编码基带处理系统。通过现场可编程门阵列仿真评估了采用迫零串行干扰抵消和最小均方误差串行干扰抵消检测算法时3×3对角分层空时编码基带系统的误码率性能。仿真分析和实验表明了现场可编程门阵列对角分层空时编码基带处理系统设计的正确性和高效性。同时,还论证了在同样条件下对角分层空时编码系统的性能优于垂直分层空时编码系统。

【关键词】多输入多输出 对角分层空时编码 串行干扰抵消 现场可编程门阵列 误码率

doi:10.3969/j.issn.1006-1010.2016.20.015 中图分类号:TN911.23 文献标志码:A 文章编号:1006-1010(2016)20-0077-07

1 引言

未来移动通信的空中接口将采用多输入多输出(Multiple-Input Multiple-Output,MIMO)技术成倍地提高通信系统的容量和频谱利用率[1]。Foschini所提出的贝尔实验室分层空时(Bell Laboratories Layered Space-Time,BLAST)编码方案是一种有效的MIMO处理算法[2]。BLAST系统的基本思想是把高速数据业务分解为若干个低速数据业务,通过普通并行信道编码器编码后,使用向量编码器对其进行并行的分层编码,编码信号经调制后用多个天线发射,实现发射分集[3]。

根据分层后的天线映射方式和数据流的不同,BLAST可分为对角分层空时码(Diagonally–Bell Laboratories Layered Space-Time,D-BLAST)与垂直分层空时码(Vertically–Bell Laboratories Layered Space-Time,V-BLAST)结构。D-BLAST是将每一层的数据流在N根天线上依照次序循环地发送,即每一个数据层都是在发射矩阵的对角线上;而V-BLAST的映射关系是固定的,即每层数据流都在同一根天线上传输,每个数据层都对应于发射矩阵的某一行。D-BLAST的数据流在各发射天线上是遍历的,其优点是D-BLAST具有较好的空时特性和层次结构,子信道的深衰落对它的影响要比V-BLAST小。

现场可编程门阵列(Field Programmable Gate Array,FPGA)具有架构灵活、算法高效、吞吐率高、可实现并行计算和动态配置等优势,特别适合用于设计并验证无线通信系统基站中的基带处理部分功能。

为此,通过Xilinx FPGA开发平台,设计了基于FPGA的D-BLAST系统结构、算法,实现了D-BLAST高效的编译码器和检测,并对不同的检测算法进行了分析和性能仿真,对研发D-BLAST类MIMO原型系统具有重要的参考价值。

2 MIMO D-BLAST系统模型

图1为MIMO D-BLAST系统结构模型,QPSK调制后的信息流,经过串并变换、信道编码和D-BLAST空时编码后,分别通过N根天线发送出去,接收端为M根天线,M≥N。假设信道为准静态的、平坦瑞利衰落信道,即信道传输矩阵H在发送L个符号的期间是恒定的,并且信道信息状态可得到有效估计。这样,接收信号和发送信号的关系表示为:

式(1)中,信道传输矩阵H为一个N行M列的矩阵,其中hi,j表示的是第j根发射天线到第i根接收天线的信道系数,hi,j服从单位方差、零均值的复高斯分布;X=[xi]T,i=1, 2, …, N表示N根发射天线所发射信号矢量;Y=[yi]T,i=1, 2, …, M表示M根接收天线上所收到信号矢量;n=[ni]T,i=1, 2, …, M表示M根接收天线上的噪声矢量,ni服从高斯分布,均值为0,方差为σ2。

3 MIMO D-BLAST的FPGA实现

基于Xilinx的ML402的FPGA开发平台,采用Virtex-4 XC4VSX55芯片和Verilog硬件描述语言实现了3×3 MIMO D-BLAST基带系统的FPGA设计。该系统主要包含D-BLAST编码模块,对映射后的符号先进行串并转换后再进行交织来实现D-BLAST编码;MIMO检测模块对空间复用的数据流进行分离和检测;D-BLAST译码模块对检测后的信息流进行D-BLAST空时译码,恢复原始比特流的估计值。

3.1 D-BLAST编码

D-BLAST系统的基本思想是把高速数据业务分解为若干低速数据业务,通过普通的并行信道编码器编码后,使用交织编码器对其进行并行的分层编码,编码后信号使用多个天线发射,实现发射分集[3]。在接收端,把多根接收天线同时接收的所有数据进行解交织,再通过并串变换最终输出译码后的串行数据。V-BLAST编码是对数据流进行串并变换,而D-BLAST与V-BLAST不同的是在串并变换后还要对数据流进行交织,因此D-BLAST的复杂度要比V-BLAST大,但是其性能却要比V-BLAST好。图2为D-BLAST结构图。

如图1所示,D-BLAST编码器从并行信道编码器输出的码元接收数据,再根据图2所示的对角线方向来进行空间编码,第1个信道编码器输出的开始N个码元排在第1个对角线,第2个信道编码器输出的开始N个码元排在第2条对角线上。一般第i个信道编码器输出的N个码元排在第(i+(j-1)×N)条对角线,没有排满的空位置零[4,5]。空时码元矩阵中的每一列就是编码后的数据,通过N个发射天线同时发射。

如图3所示,假设输入信号c=[c1, c2, c3…]来自于QPSK星座图Q,调制信号经串并变化后得到的矢量为uj[6]:

这样,通过一个交织矩阵M,可以得到D-BLAST发射信号xj为:

D-BLAST编码模块主要就是实现对角分层循环发送功能,本文设计的是3×3系统,根据式(3)提出了一种易于FPGA实现的D-BLAST编码算法。首先通过状态机产生交织图案,从而实现待编码字与矩阵M的乘积。如图3所示,D-BLAST编码FPGA实现共包括4个模块,分别为串并变换、时序控制模块、状态机和存储器。FPGA硬件仿真对时序的要求很严格,因此采用了一个单独的时序控制模块来控制FPGA实现中的时序。先对调制信号c=[c1, c2, c3…]进行串并变换成uj=[uj1,…,ujk]存入寄存器RAM中,然后在时序控制模块控制下产生一个状态机,再利用状态机来产生一个交织图案,映射到寄存器中控制RAM输出信号xj=[xj1,…, xjk],最终实现了D-BLAST的对角分层编码。本设计的核心就是采用状态机来实现传输符号的交织。

接收端根据特殊的结构方式与信号处理过程分离各子信号流,分别进行MIMO检测、空时译码、信道解码,再通过并串变换将各子信号流合并为原来的串行数据信息。

3.2 MIMO检测

接收端首先要根据不同的准则接收信号进行MIMO检测,从而确定每根天线的权值。MIMO检测的准则主要有迫零(ZF)和最小均方误差(MMSE)准则。

ZF算法是简单的利用信道矩阵H的伪逆矩阵H+作为权值矩阵GZF。

可以看出ZF算法在检测时损失了有用信息,影响了系统性能,MMSE算法用满足下式的权值矩阵GMMSE代替ZF中的GZF。

其中,表示矩阵的共轭转置,表示矩阵的Moore-Penrose伪逆,σ2为噪声方差,IM是M×M维的单位矩阵,GMMSE的行矢量gi是接收天线对于发送信号ci所形成的权矢量。

ZF和MMSE这两种算法的唯一不同之处就在于检测矩阵GZF和GMMSE的求解。因为GZF=H+,而GMMSE=HH(HHH+σ2I)+,从上述两个算法的检测矩阵就可以看出,MMSE算法的复杂度比ZF算法的复杂度大,但MMSE算法由于考虑了噪声的影响,性能要比ZF算法好。

ZF和MMSE检测算法同时分离出M个子数据流,检测过程中任一个子数据流都将受到其他M-1个子数据流的干扰。为此,引入串行干扰抵消算法后的ZF和MMSE称为ZF-SIC(Zero Forcing-Successive Interference Cancellation,迫零串行干扰抵消)接收机和MMSE-SIC(Minimum Mean-Squared Error-SIC,最小均方误差串行干扰抵消)接收机,可以进一步提高系统的性能[7]。引入SIC后,对M个子数据流按照一定的顺序依次检测,计算各子数据流的信号估值并硬判决,之后再在下一个信号的检测中抵消掉硬判决的值,循环往复,直到检测完所有的子数据流。

为改善系统的性能,对MIMO D-BLAST检测的FPGA实现分别采用了ZF-SIC和MMSE-SIC这2种不同的检测方法。因此,该MIMO检测器的FPGA实现设计共包括4个功能模块:输入输出模块、检测矩阵模块、译码模块和时序控制模块。本设计中采用流水线操作进行并行处理来提高运算速度,功能模块框图如图4所示:

(1)输入输出模块

输入输出模块是与系统其他功能模块的接口。输入模块接收信道矩阵H和接收信号R然后送入检测矩阵模块进行运算。输出模块接收译码模块输出的信号存储在寄存器中,等待同一时刻的所有信号译码完成后输出译码数据。

(2)检测矩阵模块

在MIMO-DBLAST检测中,FPGA实现最重要的就是检测矩阵G的求解,而求解检测矩阵时最关键的就是矩阵求逆。矩阵求逆的算法如下所示:

其中H∈Cn×m,而H的前k列表示为Ak∈Cn×k,Hj代表H的第j列,则H=Am,Ak=(Ak-1,Hk)。

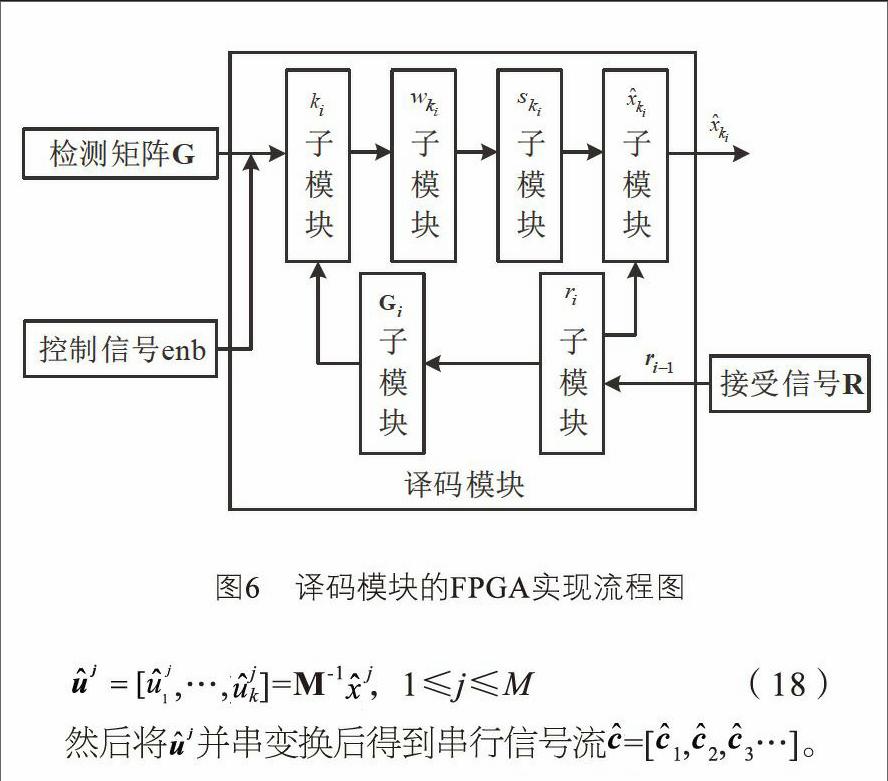

根据上面的矩阵求逆算法可以得到图5所示的FPGA实现流程图。本文FPGA设计采用了迭代运算、加法运算和乘法运算,采用复用的方式来减少资源占用,除法运算采用查表的方式来提高运算速度。如图5所示,首先初始化得到A1+,然后用一个计数器K来控制迭代次数,当k 检测矩阵模块首先根据ZF-SIC和MMSE-SIC算法特点选择相应的检测矩阵GZF和GMMSE,然后完成上述矩阵求逆子模块,把求逆的输出存入寄存器中,根据式(4)和式(5)进行相应检测矩阵的运算。当完成检测矩阵G计算后送入译码模块,同时输出一个使能信号enb送入译码模块。 (3)译码模块 计算出检测矩阵G后,开始进行接收信号译码。译码主要是通过逐步检测相消法来进行子流的区分和检测。串行干扰抵消检测器通过M次迭代实现所有M个子数据流的检测。每次检测出一个子数据流,然后将其从接收信号向量中减掉,如此循环,直到检测完最后一个子数据流[8]。其具体算法如下所示: 译码模块首先接收输入模块的用户信号R,存入缓存中等待检测矩阵的使能信号enb。当enb变高后,同时接收到检测矩阵送入的数据进行译码处理。译码处理部分总共包含6个子模块,分别完成公式(11)~(17)的计算。即首先计算ki、wki、ski和,再把判决的值送入输出模块同时反馈回去译码模块,同时接收信号再减去对剩余信号的干扰,如此不断循环直到最后一个信号译码完成。图6为译码模块的FPGA实现流程图。

检测矩阵模块和译码模块需要进行大量的运算,加法运算和乘法运算采用复用的方式来减少资源占用,除法运算采用查表的方式来提高运算速度。

3.3 D-BLAST译码

接下来进行D-BLAST译码,D-BLAST译码是按照对角线型方向来进行译码的,实际上是如图2所示编码的逆过程。由于在编码端对信号串并变换后再进行交织,因此接收端的D-BLAST译码是与发射端的编码相对应的操作,先进行解交织,然后再进行并串变换。

首先信号乘以解交织矩阵M-1,得到:

然后将并串变换后得到串行信号流=[1,2,3…]。

根据式(7),译码的重点是如何获得解交织矩阵M-1,然后与信号进行乘法运算。D-BLAST译码的设计实现共4个模块,包括存储器模块、状态机控制模块、时序控制模块、并串转换模块,如图7所示。译码时把检测后的信号=[,…,jk]存储在RAM中,时序控制模块控制状态机产生交织图案,时序控制模块控制从RAM中读出并行的译码数据,最后对译码后的3路并行数据流进行并串变换,形成串行数据流,实现D-BLAST译码。

4 性能仿真分析

通过Verilog硬件描述语言在Virtex4-VC4VSX55芯片上实现了带宽为33 MHz、速率为200 Mbps的3×3 D-BLAST基带FPGA硬件系统,并在独立同分布的平坦瑞利衰落信道下对系统的性能进行了FPGA运行仿真评估。全局时钟采用了100 MHz的时钟频率,发射端和接收端均采用了同步电路,以保证系统的稳定性。

图8是分别采用ZF-SIC和MMSE-SIC检测方法的MIMO D-BLAST系统在FPGA上运行的误码率曲线。从图8中很明显地可以看出MMSE-SIC性能优于ZF-SIC检测算法,在误码率为10-3时,MMSE-SIC的性能要比ZF-SIC大约有2 dB~3 dB的增益。在收发天线相同的系统中,MMSE-SIC的性能优于ZF-SIC。

从图8中还可以看出,在误码率为10-3时,采用16-QAM调制方式的ZF-SIC检测所需要的信噪比是23 dB,采用QPSK调制方式的ZF-SIC检测的信噪比是21 dB,因此16-QAM调制的性能略差于QPSK调制。同时QPSK承载2 bit信息,16-QAM符号承载4 bit信息,因此QPSK速率小于16-QAM。实际应用中需要通过自适应调制技术在不同的信道情况下自适应地选择不同的调制方式。

表1列出了两种不同检测算法接收机所占用硬件资源的情况。从表1可以清楚地看出,ZF-SIC算法消耗的硬件资源要少于MMSE-SIC,即MMSE-SIC检测算法性能的提高是以计算复杂度为代价的。

图9对比了3×3 D-BLAST和V-BLAST基带FPGA的仿真性能,可以看到,D-BLAST的性能相对于V-BLAST系统大约有1 dB的增益。

表2列出了D-BLAST和V-BLAST接收机所占用硬件资源的情况。从表2可以清楚地看出,D-BLAST译码端消耗的硬件资源要多于V-BLAST,即D-BLAST译码算法的复杂度要高于V-BLAST。这是因为V-BLAST编码只是对数据流进行了简单的串并变换,但D-BLAST不仅进行了串并变换还对数据流进行了交织和解交织,因此D-BLAST译码的复杂度要比V-BLAST的复杂度大。

5 结束语

通过Verilog硬件描述语言在Virtex4-VC4VSX55芯片上实现了带宽为33 MHz、速率为200 Mbps的3×3 D-BLAST基带FPGA硬件系统,对系统的性能进行了FPGA运行仿真评估,对系统占用的硬件资源进行了统计。设计中涉及QPSK调制解调、D-BLAST编码、MIMO检测和译码等主要功能模块的实现。其中,MIMO检测采用了ZF-SIC和MMSE-SIC两种不同的检测算法以提高系统的性能。对3×3 D-BLAST和V-BLAST基带FPGA运行仿真性能还进行了对比。这些工作对研发基于D-BLAST检测的MIMO原型系统具有重要的参考价值。

参考文献:

[1] Foschini G J, Gans M J. On limits of wireless communications in a fading environment using multiple antennas[J]. Wireless Personal Communications, 1998(3): 311-335.

[2] Foschini G J. Layered space-time architecture for wireless communications in a fading environment when using multi-element antennas[J]. Bell Labs Technique Journal, 2002(2): 41-49.

[3] 谢显中. 移动通信中的空时编码技术与接收机设计[D]. 西安: 西安电子科技大学, 2000.

[4] H E Gamal, A R J Hammons. A New Approach to Layered Space time Coding and Signal Processing[J]. IEEE Transactions on Information Theory, 2001(6): 2321-2334.

[5] H E Gamal, M O Damen. Universal Space-time Coding[J]. IEEE Transactions on Information Theory, 2003(5): 1097-1119.

[6] Narayan Prasad, Mahesh K, Varanasi. Analysis and Optimization of Diagonally Layered Lattice Schemes for MIMO Fading Channels[J]. IEEE Transactions on Information Theory, 2008(3): 1162-1185.

[7] Branka Vucetic, Jinhong Yuan. 空时编码技术[M]. 王晓梅,译. 北京: 机械工业出版社, 2004.

[8] 刘谦雷,杨绿溪,许道峰. 用于MIMO信号检测的降低复杂度V-BLAST算法[J]. 通信学报, 2007,28(9): 40-45.

[9] 黄虎. D-BLAST MIMO-OFDM基带系统的FPGA实现[D]. 北京: 北京交通大学, 2009.

[10] 王利勇. MIMO检测算法的研究与实现[D]. 西安: 西安电子科技大学, 2010.