基于高分子电压诱导变阻膜的全PCB抗脉冲防护

刘 辉 吴丰顺 武占成 龚德权 王 晶 胡元伟 马浩轩

(1.华中科技大学 材料科学与工程学院,湖北 武汉 430074;2.中国航天五院五一四所 院士专家工作站,北京 100086;3.武汉芯宝科技有限公司,湖北 武汉 430043)

0 引言

静电放电(electro static discharge,ESD)是一种常见的近场危害源,可形成高压强电场、瞬间大电流,并伴有强电磁辐射,形成静电放电电磁脉冲。随着电子器件封装集成度的不断提高,许多静电敏感元器件的耐压阈值并不高[1],容易受到ESD 影响而导致失效。因此,需要对电子器件进行ESD防护以减少损失。

对电子电路的 ESD 及电磁脉冲(electromagnetic pulse,EMP),目前普遍采用瞬态电压抑制器(transient voltage suppressor,TVS)、压敏电阻等分立器件对集成电路等敏感元件的引脚进行一对一的保护[2]。King等[3]采用并联电容和并联齐纳二极管的方法来实现ESD 的防护,发现1 μF 电容和14 V 齐纳二极管均可对半导体桥起到ESD防护的效果;Lü等[4]研究了压敏电阻、TVS对电爆装置在人体高压模型下的静电防护效果,发现只有瞬态二极管(transient voltage suppressor,TVS)可提供有效的ESD 保护,使电爆装置在50 kV 高压下不被击穿;De Conti 等[5]发现GDNMOS 薄膜和GDBIMOS 器件具有良好的电性能(触发电压、漏电流等),可用于高压ESD防护。

本文介绍的全电路板抗脉冲防护方案,是以“疏导”的方式将电磁脉冲产生的能量在还不足以对电路系统产生危害前引导至能量吸收点,并将其对地释放,从而使电子电路及其脉冲敏感元件得到保护。

1 电子电路全系统抗脉冲防护启动电压的设置

ESD 是在纳秒量级的时间内完成的,峰值电流可达几十安培,瞬间功率十分巨大,产生的强电磁辐射可以感应出几百伏乃至上千伏的电势。

电磁脉冲弹引爆时,其电磁场将以光速到达场源覆盖区域的电子装备上的各个线路及元器件,根据GJB 1571A-97-RS105 关于脉冲波形的定义,在各线段上可感应(50 000 V/100)×L(线段长度,cm)的高压电势。当感应电压高于元件的承受能力时,元件或线段就会被击毁。如果在电路中的每一条线段上加装一个适当的抗脉冲元件,形成保护网络,将高压信号通过抗脉冲元件对地释放,则电子电路就可以具备对电磁脉冲攻击的防护能力。

2 常用脉冲高压保护元件的电压抑制特性

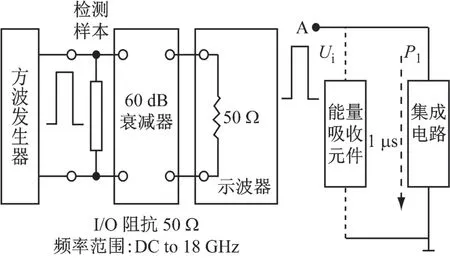

对集成电路而言,由于集成电路连接线及内部电路结构导致的信号延时在μs 数量级,在选择或制造保护元件时,其开关速度(响应时间)是最重要的因素,通常需要把启动响应时间控制在5 ns以下,把电压限幅响应时间控制在10 ns以内。为了获取保护元件对脉冲的响应信息,采用了传输线脉冲(transmission line pulse,TLP)测试技术[6]。TLP测试原理及测试电路如图1所示。

图1 传输线脉冲测试原理及集成电路

进行电路测试时,外加脉冲信号源的脉冲宽度50 ns,脉冲电压500 V;测试电路中集成电路引脚P1的连接线和内部电路结构导致的延时约为1 µs。对几种元件进行TLP 测试和性能对比,可以看出TVS 反应灵敏,开关响应时间在1 ns 内将高压脉冲吸收,放电速度也很快,从而保护集成电路等ESD、EMP敏感元件。

而测试电路中压敏电阻作为保护器件的电压响应曲线显示,压敏电阻对高压脉冲虽有钳位作用,但其响应速率较慢,钳位曲线平缓,限幅响应时间远大于10 ns,不太适用于集成电路抗高压脉冲的场合。

在测试电路中,从高分子材料PESD 放电元件(Littelfuse PGB10603)的电压响应曲线可以看出,其开关响应时间略大于TVS管,为5 ns左右,限幅响应时间小于10 ns,可在30 ns内将高压脉冲能量吸收释放完毕,使高电压迅速趋向于0,适合应用于抗脉冲防护的场合。

以上单体元件最大的不足是它们只能安装在电路板的表面,为电路中需要保护的元器件引脚进行一对一的保护。而如果PCB 中需要抗高压脉冲的点很多,采用单体元件来保护则会占用大量板面面积。

3 高分子复合纳米电压诱导变阻薄膜的制备和性能测试

上述采用多个分离器件进行ESD、EMP 防护的方法占用了大量的PCB 表面积,这已成为电子产品微型化和进一步发展的瓶颈问题。为达到电子电路高压脉冲全防护的目的,理想的方式是利用电子电路载体PCB,在PCB 内层制作基于电压诱导变阻膜的高压脉冲吸收网络。这种薄膜在通常情况下是绝缘体,当有一个异常高压脉冲出现时,它会变为导体;当这个电压过后,它又恢复至绝缘状态,即膜相当于是由电压控制的开关。

3.1 电压诱导变阻膜制备

电压诱导变阻膜需要双面覆铜,制作成芯板结构,然后经刻蚀、层压等PCB 制作工艺,成为PCB组成部分。电压诱导变阻膜的制作工艺如下。

(1)材料。聚胺脂、环氧树脂、聚酰胺树脂、石墨烯、纳米铜粉、铁氧体粉末、氧化锌等。

(2)导电粒子活化和纯化预制。选取不同粒径的铜粉或氧化铁粉及粒径8 µm 的球形铜粉,分别加入盛有纯净水的玻璃杯中,边搅拌边渗入浓度为90%的H2SO4,搅拌机调至120 r/min,60 min后滤出、洗净、烘干,得到活化的导电粒子;然后将已活化的导电粒子放入纯化液中浸润72 h 后滤出,获得被活化和纯化的粒径小于1 µm 的片状铜粉,或氧化铁粉及圆珠颗粒导电粒子。

(3)纯化液的制取。玻璃杯中加入200 mL 工业乙醇,然后投入50 g 生物虾黄粉末,玻璃杯置升温炉上,温度调至45 ℃,搅拌8 h 后,将混合液置离心机,收集甩出的液态物获得纯化液。

(4)球形铜粉改性。将已纯化的100 g 球形铜粉投入盛有300 g工业乙醇的反应釜中,滴入4 g环氧树脂,封闭反应釜,温度控制在65 ℃,搅拌调至120 r/min,3 h 后滤出洗净烘干,得到表面附着一层约80 nm厚度绝缘膜的改性非导电球形颗粒。

(5)组分制备。A 组分:缩水甘油胺类环氧树脂质量比40%,环氧族类环氧树脂质量比17%,粒径<2 nm 的氧化锌微粉质量比7%~25%,经改性处理的氧化铁粉质量比4%~13%和片状铜粉质量比4%~13%,片状石墨烯质量比0.3%~1.0%,配制后人工搅拌初步共混,然后将上述配料加入三辊混炼机充分分散均匀后获得电压诱导变阻膜基体材料浆料A 组分。B 组分:将正丁醇、缩水甘油脂类环氧树脂、聚酰胺树脂加入搅拌容器中,搅拌机开至500 r/min,搅拌2 min,然后将步骤(4)中预制的粒径8 μm 已改性处理的圆珠颗粒非导电粒子加入其中,继续搅拌10 min 获电压诱导变阻膜基体材料浆料B组分。

(6)芯板制备。取出双组分,按需量1∶1 配比,搅拌均匀后印刷成膜,双面覆铜固化后将一面刻蚀成能量吸收矩阵层。芯板再按其他生产步骤完成余下的加工,获得全抗电磁脉冲PCB。

3.2 高分子复合纳米电压诱导变阻膜的电性能实际指标

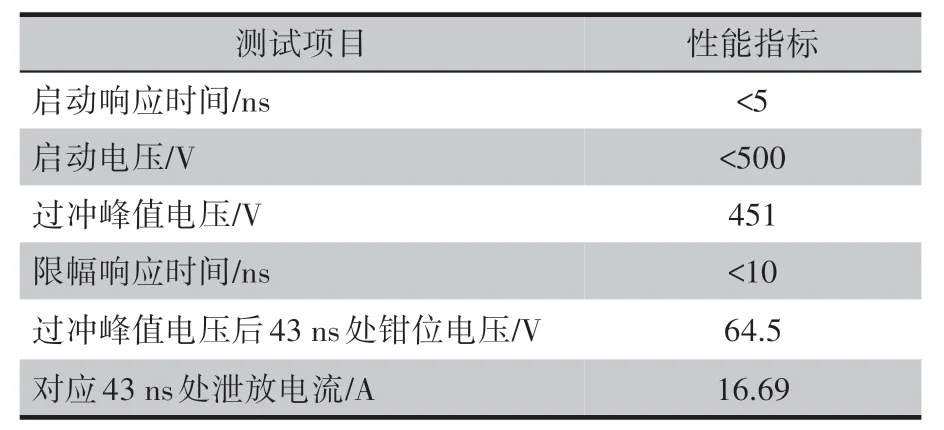

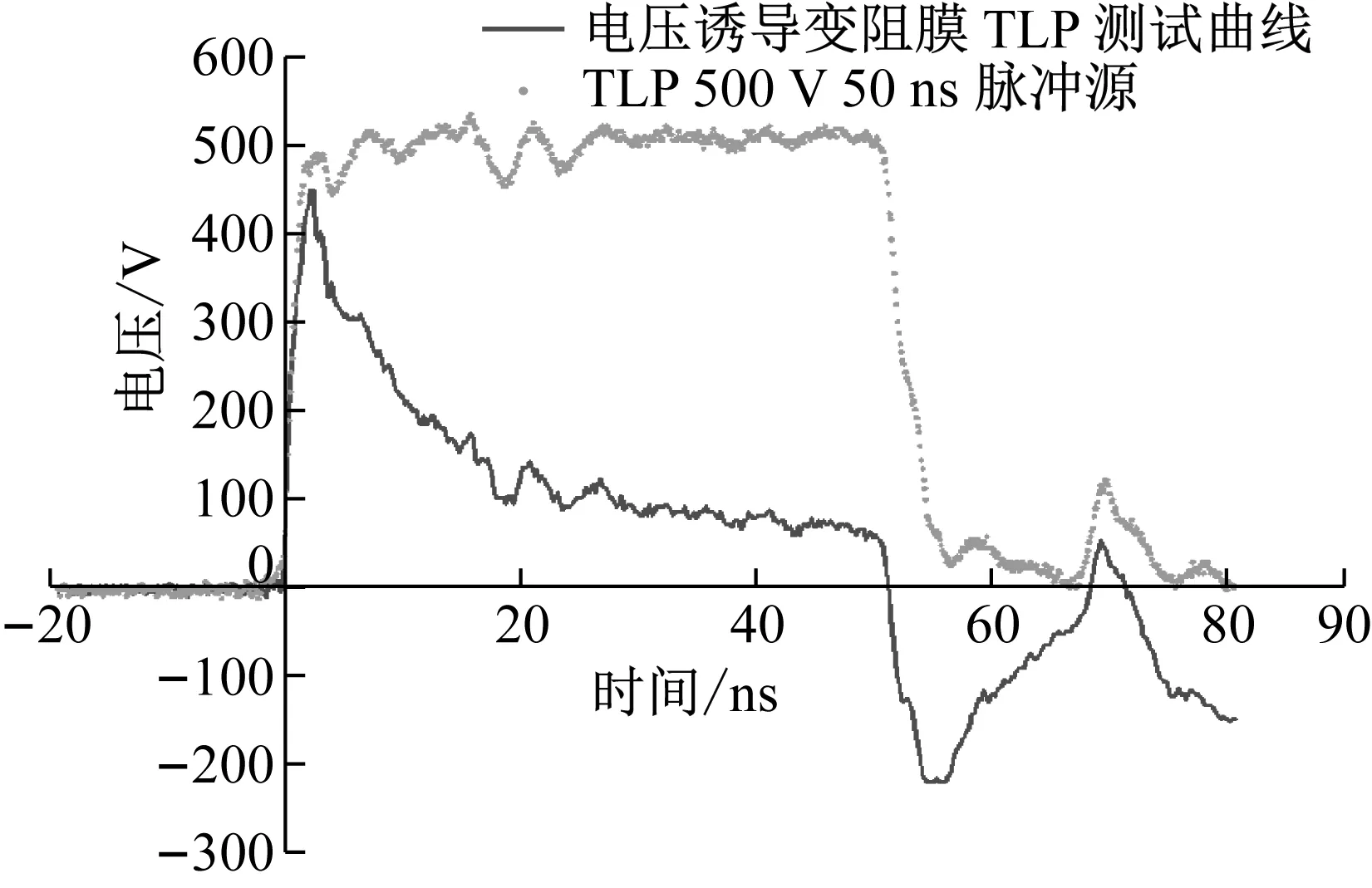

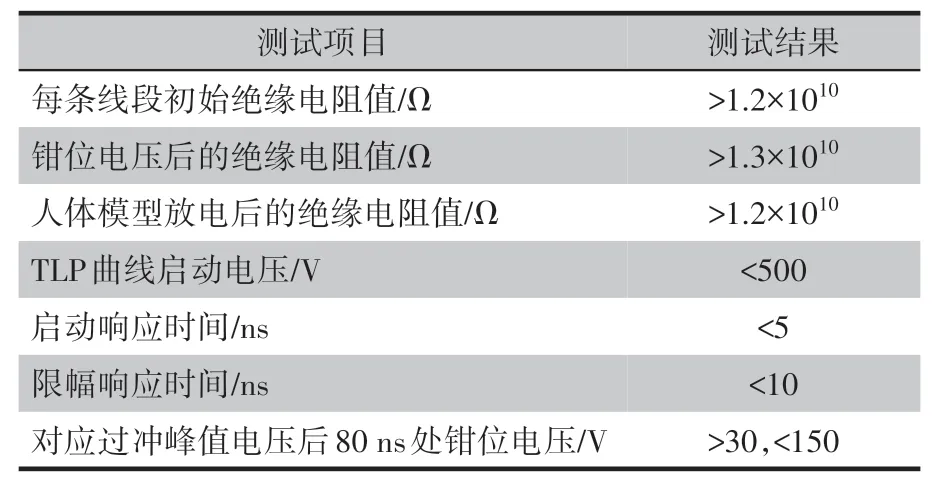

对制备的高分子复合纳米电压诱导变阻膜[7]进行TLP 测试,测试波形如图2 所示,测试结果见表1,电压诱导变阻膜TLP测试伏安特性曲线如图3所示。

表1 高分子复合纳米电压诱导变阻膜性能测试结果

图2 高分子复合纳米电压诱导变阻膜的传输线脉冲测试曲线

图3 电压诱导变阻膜传输线脉冲测试伏安特性曲线

从图2 可看出,该膜对脉冲电压能快速响应,限幅响应时间小于10 ns;从图3 可见,电压诱导变阻膜任意点的触发电压、钳位电压及电流泄放能力对比高分子材料PESD 放电元件都有比较明显的优势,这种高分子复合纳米电压诱导变阻膜具备制作脉冲高压全防护PCB理想的电性能。

4 抗高压脉冲电路板的保护原理及应用

4.1 保护原理

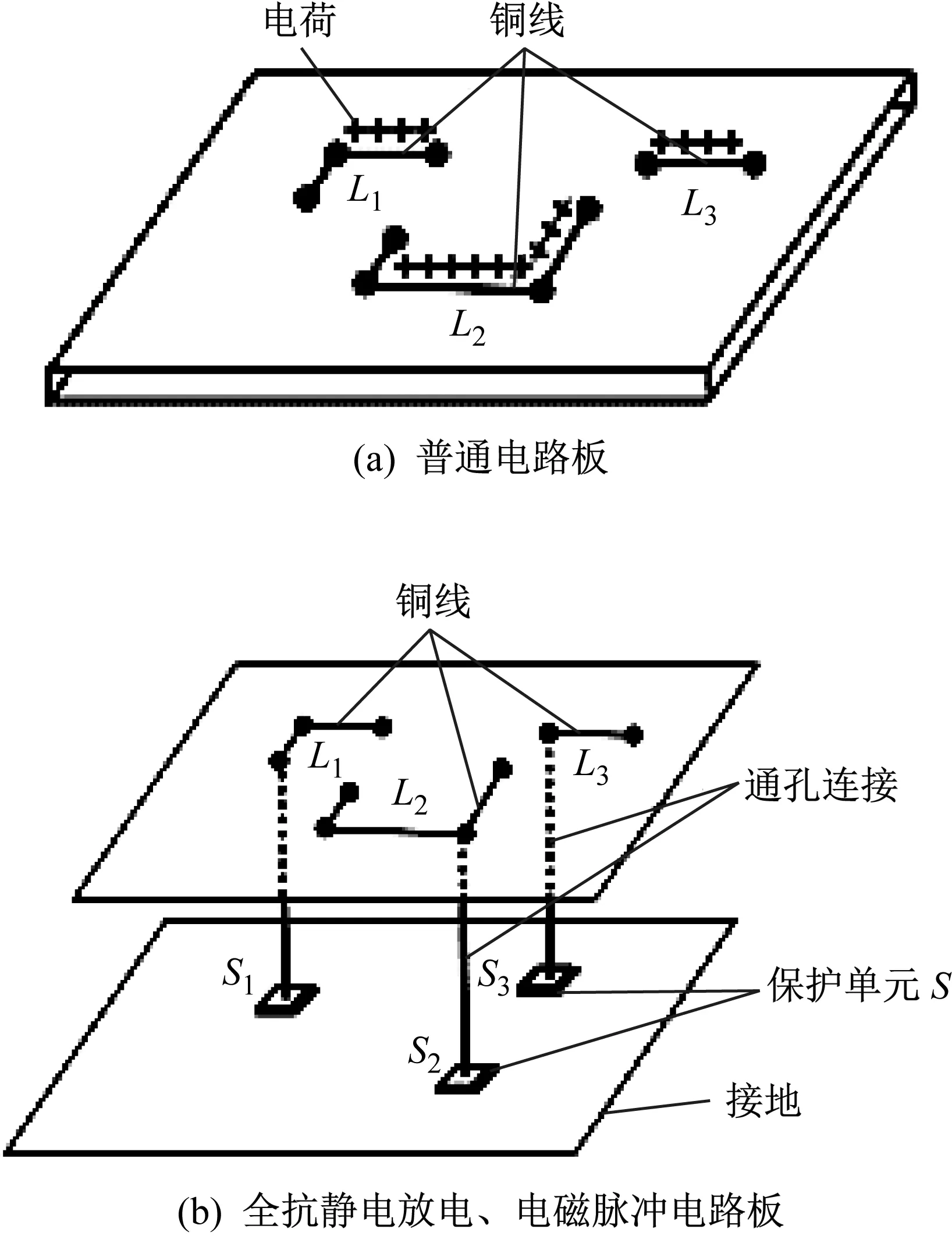

普通电路板和有内部保护单元的电路板如图4所示。

图4 普通电路板和有内部保护单元的电路板

图4(a)中,未加防护的普通电路板铜导线在强电磁脉冲(如电磁脉冲弹爆炸瞬间释放的强电磁暴)作用下,瞬时在每厘米覆铜线上可感应500 V 以上的高压[8],如果没有保护元件吸收,这个高压也将会直接作用在PCB 的元器件上,导致器件损坏。未加防护的PCB,其元器件除受EMP 的影响外,还受ESD 的作用。ESD 具有高电压、低电量、大电流和作用时间短的特点,静电荷产生方式有摩擦充电、离子充电、直接充电或电场感应充电等[9]。人体静电可达2~15 kV,在电子设备的运输、使用、维修全寿命过程中,可能通过接口电路触碰到设备内的线路,将人体高压静电传递给电路,如果没有防护,这将直接造成该线路的敏感元件损坏。

常用的EMP 防护措施主要有屏蔽、接地、滤波、加防护器件。而加防护器件是目前应用比较广泛、效果比较明显的一种防护措施,也是抗EMP 加固研究的主要手段[10]。图4(b)中加装了由电压诱导变阻膜制备的保护单元S,PCB上的每一条覆铜线都在电路板内部与一个保护单元S正面相连,保护单元S反面接地。

当电磁脉冲感应作用在图4(b)中的任意一条覆铜线时,每条线段两端会瞬间感应(50 000 V/100)×L的高压电势,若线长为3 cm,则瞬间电势U高达1 500 V;该电势U会在5 ns 时间内启动各线段对应的保护单元S。在这个脉冲持续过程中,保护单元S将一直保持开启状态,直至整个电磁脉冲过程结束,保护单元S才恢复关闭状态。由于保护单元S对高压脉冲的响应非常快(<5 ns),而敏感元器件引脚电压升高到损坏电压的时间相对较长(内部阻容延时),因此,在敏感元器件引脚电压升高到损坏电压前,保护元件S开通,使敏感元器件引脚电压得到钳位,从而保护敏感元件。

当人体触碰到图4(b)中的任何一条线段时,静电都会传导给该线段。而保护单元S(保护单元S为电压诱导变阻膜)的启动电压小于500 V,开关响应时间小于5 ns,限幅响应时间小于10 ns,钳位电压小于65 V,在PCB 上的集成电路等电压元器件尚未对高压脉冲产生反应时,保护单元S即可将这个有害脉冲吸收泄放掉。因此,图4(b)中任一条覆铜线无论是接触到静电电压还是感应到电磁脉冲高压,这个高压均会被保护单元S吸收掉,从而使线上的元件免受高压脉冲伤害。

4.2 实际应用

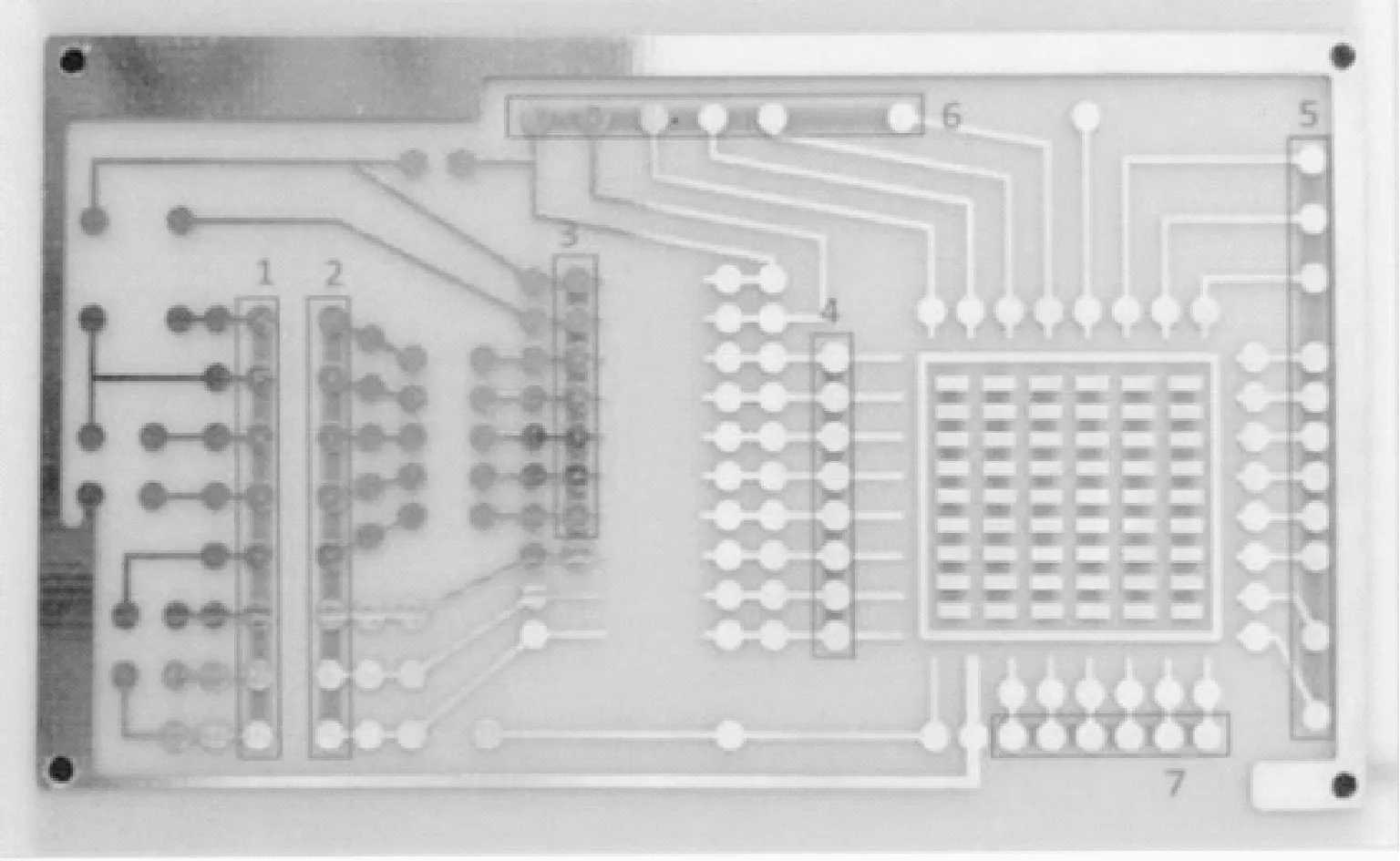

一种全抗高压脉冲电路板实物如图5 所示,该电路板上所有需要进行高压脉冲防护的线段有109 条,在这块电路板夹层中对109 条线段都设置有背景防护点S,构成S1~S109的高压脉冲泄放网络。该电路板的每个Cu 线段都有ESD 和EMP 防护能力。

图5 一种全抗高压脉冲保护电路板实物(4.0 cm×7.5 cm)

将该板的线段区分为7 大区域,然后对各区域线段分别进行了ESD 多项指标测量以及抗ESD能力测量,电性能见表2。从测试结果看,该PCB的每一条非接地覆铜线对ESD 脉冲都具有完全的防护能力。

表2 全抗脉冲电路板对ESD的防护实测结果

钳位电压测试:方波发生器试验电压设置为1 kV,脉冲宽度100 ns,示波器记录钳位电压波形。

人体模型(human body model,HBM)放电测试:放电电压设置为±4 kV,放电间隔1 s,正负电压各测试3次。

在抗EMP 能力方面,全抗脉冲电路板采用电压诱导变阻膜,其电流泄放能力超过50 A;二次击穿电流达53.9 A,等效计算的抗瞬变脉冲感应电压能力可达80 kV。

5 结语

本文介绍了一种利用高分子电压诱导变阻膜来实现全电路板抗脉冲防护的方法。所用高分子诱导变阻膜由高分子基体材料和分散在其中的纳米导电填料组成,由电压诱导变阻膜制成芯板,在PCB夹层中构建ESD和EMP防护背景网络,从而实现PCB 对瞬变脉冲的全电路防护。相较于普通PCB,全抗脉冲PCB 在受到高压脉冲时,保护单元能快速将这部分能量泄放掉,提升了其抗脉冲能力。利用高分子电压诱导变阻膜在夹层中构建防护网,在不占用PCB 表面积情况下可降低生产成本。