硅压敏电阻刻蚀形貌对高温压力传感器输出特性影响

冀鹏飞,赵妍琛,雷 程,梁 庭,刘润鹏,党伟刚

(1.中北大学,省部共建动态测试技术国家重点实验室,山西太原 030051;2.西安航天动力研究所,陕西西安 710199)

0 引言

近年来,汽车、船舶、航空航天等领域的大力发展,增加了高温下压力测试的需求[1]。作为压力传感器的分支,压阻式压力传感器具备体积小、易于集成、信号传导机制直接等特点,在压力测量市场中占据了主体地位,也是耐高温压力传感器研究的重要方向[2]。压阻式压力传感器是利用压阻效应作为检测原理,用4个压敏电阻连接构成惠斯登电桥,当压力施加在膜表面时,通过电阻变化将压力变化转化为输出电压[3-4]。压敏电阻既是感压部件也是压力和电信号转换部件,是关键结构之一。在制备过程中,压敏电阻的刻蚀是关键工艺,并且在实验测试中,发现制备的压阻式压力传感器在环境温度升高后会出现较大程度的温度漂移。对此现象进行分析,发现4个条状电阻结构分别位于感压膜的不同方位,当刻蚀的电阻条不均匀时,惠斯登电桥电路达不到平衡,使其零点电压增大,这会增加传感器在高温下的热漂移;刻蚀形貌的粗糙同样影响后续工艺,使传感器无法达到理论性能,甚至失效。本文分析制备压敏电阻出现刻蚀硅电阻条深度不均匀、刻蚀底面形貌差的原因,通过改变制备过程中的刻蚀时序参数,提高刻蚀精度,实现刻蚀均匀性的增加,形貌的改善,减小了压阻式压力传感器的热零点漂移。

1 深反应离子刻蚀工艺

深反应离子刻蚀(DRIE)是物理刻蚀和化学刻蚀的结合,既有很好的方向选择性、刻蚀速率高,也改善了刻蚀侧壁的垂直度[5-6]。DRIE工艺主要分为低温刻蚀工艺和博世(Bosch)工艺[7]。低温刻蚀技术能够实现各向异性高纵横比刻蚀,但对基板温度要求高,需要较长液氮处理时间[8]。Bosch工艺能在刻蚀硅时减弱横向刻蚀,该工艺能够提供接近90°的刻蚀度,以及很少的侧向腐蚀,是常见的DRIE刻蚀工艺,也是硅加工体系中的关键工艺[9]。

Bosch工艺由刻蚀和钝化交替循环组成,硅的各向异性刻蚀是以SF6作为刻蚀气体,具体反应过程如下:

SF6→SFn+(6-n)F*,n=0,1,2,3,4,5

(1)

Si+4F*→SiF4↑

(2)

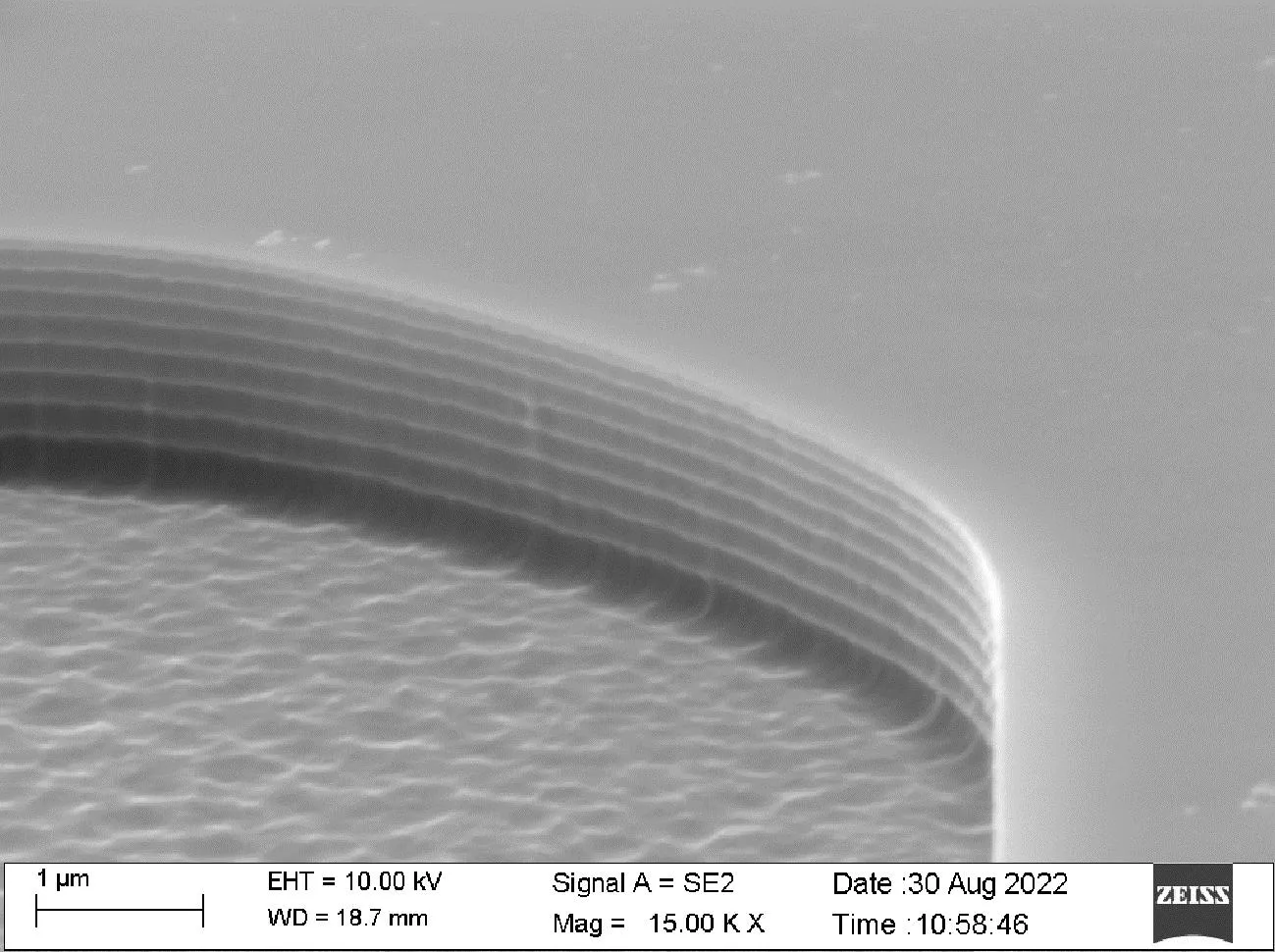

在钝化步骤期间,利用八氟环丁烷(C4F8)组成聚合物层钝化在衬底表面,循环下次刻蚀阶段,钝化的聚合物层和衬底的硅一同被刻蚀。在实际的刻蚀循环中,Bosch工艺可以分成3个部分,分别是钝化聚合物、刻蚀聚合物、刻蚀硅。钝化聚合物和刻蚀硅主要为化学反应,是各向同性的,化学反应取决于气体的扩散。刻蚀聚合物时,侧壁仅有化学反应,而底部除了气体刻蚀,还有在鞘区的作用下,F*离子被偏压加速轰击的物理作用。这实现了高垂直刻蚀速率,但由工艺特性所致,会在侧壁产生特有的扇贝图形,如图1所示。通常,当扇贝尺寸远小于刻蚀长宽尺寸时,其影响可以忽略不计。

(a)刻蚀前

(b)刻蚀后

2 实验材料及装置

2.1 掩膜选择

理想的DRIE掩膜应该是低成本,易于集成和移除,具有高刻蚀选择性和对DRIE设备的可忽略的污染[10-12]。常用的掩膜材料有氧化物、金属和光刻胶,主要是因为它们具有高的掩膜选择比,不需要厚的掩膜层,但是金属掩膜容易在设备刻蚀腔体和结构侧壁中残留污染物,钝化在沟槽中的非挥发性颗粒会导致沟槽变窄,并且影响刻蚀形貌。根据热膨胀系数匹配程度、氢氟酸与硅和氧化硅完全相反的化学特性,一般选用氧化硅作为硅的掩膜[13]。与此同时,由于总体刻蚀深度仅为1.5 ~2.0 μm,光刻胶与硅的刻蚀比足够满足掩膜需求;并且从工艺步骤角度出发,氧化硅掩膜需要多光刻和湿法腐蚀步骤,以及后续的去除掩膜操作。最终选择光刻胶作为刻蚀掩膜。唯一需要关注的点在于刻蚀过程等离子体源的高强度辐射和氟自由基(F*)与硅的放热反应产生的热量会导致光刻胶掩膜发生化学变形,影响后续工艺。

2.2 样品制备

实验使用4英寸硅晶圆,晶向为<100>,进行无机清洗,对3号液和1号液清洗。

确保晶圆表面无杂质后,在光刻间应用标准的光刻工艺处理晶圆。首先,使用烘箱在130 ℃氛围涂附六甲基二硅氮烷(HMDS),增加硅片表面粘附性;然后,在晶圆抛光面旋涂光刻胶AZ6130,其掩膜精度≤1 μm,满足刻蚀需求。经过前烘,使用EVG610光刻机进行光刻,曝光时间取决于光刻胶厚度和型号,厚度为2.5 μm的AZ6130需要100 mj/cm2的曝光剂量。

将400K显影液用1∶6的比例与去离子水进行稀释,稀释后能减缓显影速度,更好地控制显影效果。显影后使用显微镜观察显影结构,最后在120 ℃烘台蒸发多余水分可以使光刻胶有良好的掩膜作用。

2.3 实验装置

使用Omega系列深硅等离子刻蚀机对样品进行刻蚀,刻蚀系统主要针对硅的多维图形化、深槽刻蚀,可以实现侧壁高垂直度,该刻蚀系统如图2所示。

深硅刻蚀机刻蚀硅时,光刻胶和硅的选择比为1:100,能很好地保护非刻蚀区;使用氦气对衬底电极和晶片背面之间的空间进行冷却,维持晶圆表面低温,晶圆过热会导致刻蚀的各向异性变差。刻蚀后,使用紫外激光加工平台进行切割,并分别用共聚焦显微镜和电镜观察样品。

(a)深反应离子刻蚀系统

(b)刻蚀腔体示意图图2 实验刻蚀系统

2.4 实验方法

有研究人员通过添加工艺步骤或者高级时序控制来研究刻蚀过程的问题,这通常会增加工艺复杂性,并且需要昂贵的工具和复杂的研究过程[14-15]。本文使用控制变量法,能够得到单一参数对刻蚀形貌的影响趋势[16]。通过单独调整Bosch工艺的参数,实现多刻蚀循环下μm级刻蚀过程可控,该方法能用于大多数深硅刻蚀设备,提高了研究过程中设备的适应性。

3 实验过程及分析

Bosch工艺可分为3个单独的步骤,其中聚合物钝化、硅刻蚀主要是化学反应,依赖于气体的扩散;刻蚀聚合物为物理作用,与结构的纵横比有关。由于刻蚀单元内有不同面积的结构图形,并且有宽度较窄的沟道,引出了Bosch工艺中的2个限制条件:DRIE滞后和微负载效应。DRIE滞后即通道宽度小于100 μm时,受限特征内的气体供应有限,不同宽度的通道无法蚀刻到相同的深度;微负载效应是因MEMS器件中的不同特征尺寸通常是同一过程中制造的,同一刻蚀图案内刻蚀密度有区别导致刻蚀速率不同,在刻蚀密集的区域反应离子快速消耗,造成供给失衡,刻蚀速率降低,使单片晶圆整体刻蚀不均匀性增加。根据上述概念,由S.L.Lai等提出的改善方式为调整钝化时间和刻蚀工艺之间的比率[17]。现有的结构尺寸最小沟道为80 μm,同时在晶圆结构中有刻蚀面积比相差很大2种图形,相比较而言,刻蚀形貌更多受到刻蚀微负载效应的影响。

本文在刻蚀设备不更改的前提下,设计为多loop数刻蚀,增强刻蚀深度的精度控制,同时减少Bosch工艺中扇贝图形对结构的影响。通过控制单一变量法研究和优化Bosch工艺的时序参数,提高结构刻蚀精度和整体结构的均匀性,改善刻蚀形貌。

以设定刻蚀参数为基准,如表1所示,分别改变刻蚀和钝化聚合物时间(简称钝化时间),研究二者比率变化时,形貌的变化趋势,最后得到Bosch工艺刻蚀电阻条结构的最佳参数(表1中,1 mTorr=133.3 Pa;

1 sccm=0.000 6 m/s)。

表1 DRIE参数

3.1 改变刻蚀聚合物时间

刻蚀时间由刻蚀聚合物和刻蚀硅共同组成,在研究前期出现的问题是偶尔会发生刻蚀loop数增加,刻蚀深度不变的现象,推测为刻蚀面上钝化的聚合物在第二阶段未完全去掉,故刻蚀硅时间TE2不变,增加刻蚀聚合物时间TE1。实验期间钝化时间固定为3 s,刻蚀硅时间为2.3 s,刻蚀5片,进行五点法测量,计算平均刻蚀速率,结果如图3所示。

图3 刻蚀聚合物时间与刻蚀速率关系

从图3可知,在刻蚀时间逐渐增加时,刻蚀速率增加。在TE1阶段,刻蚀聚合物结束后,仍有刻蚀气体,并开始进行下一阶段的刻蚀任务,提高了刻蚀速度。然而过快的刻蚀速度会导致侧壁垂直度变差、刻蚀精度降低。Bosch工艺的侧壁在每个loop结束形成一个侧弧,当1个loop中刻蚀深度越大,侧弧对内侧硅的侵蚀越严重。侧壁扇贝图形无法避免,在极板电压不改变的前提下,可以通过减小1个loop刻蚀深度减小扇贝图形的半径,降低对侧壁内部的刻蚀,达到可以忽略的程度,同时降低刻蚀速率,提高刻蚀精度。

3.2 改变钝化聚合物时间

在钝化聚合物时间对刻蚀效果影响的实验中,刻蚀时间为5.3 s,其中刻蚀钝化聚合物时间为3 s,从原始时间1 s逐渐增加,使用台阶仪进行测量,绘制不同钝化时间下刻蚀速率的变化趋势,如图4所示。

图4 钝化时间与刻蚀速率关系

在1~3 s期间,随着钝化时间的增加,刻蚀速率迅速下降,是因为此阶段增加了C4F8与硅反应时间,形成的聚合物保护层更厚,刻蚀聚合物所需要的时间增加;3~5 s时,刻蚀聚合物所需时间进一步增加,但由于聚合物层厚度过大,刻蚀过程出现残留物,被刻蚀的硅底部粗糙度增加,刻蚀形貌变差,刻蚀形貌如图5所示。

(a)钝化时间3 s

(b)钝化时间5 s图5 不同钝化时间刻蚀面对比

3.3 刻蚀参数选择

从2个实验数据了解到过长的钝化时间会使刻蚀面粗糙度增加,刻蚀聚合物时间的增加会对侧壁有所影响,两者都不宜过长,并且钝化时间的变化对于刻蚀速率的影响更加明显。发现在刻蚀中存在刻蚀形貌异常的现象,如图6所示。

(a)刻蚀底部高粗糙度

(b)刻蚀表面颗粒残留图6 刻蚀后底部形貌异常

随着刻蚀参数变化,刻蚀形貌异常区域面积发生改变,具体见表2。

表2 钝化与刻蚀聚合物时间比例对形貌影响

由于在晶圆设计图中同时存在窄沟道和宽沟道,并且窄沟道和宽沟道分属不同区域,刻蚀过程中,不同宽度的沟道气体进入的量不同,特别是窄沟道与宽沟道宽度之比大于1∶10。钝化期间,C4F8在宽沟道中与硅反应形成的聚合物厚度大于窄沟道,当恰好刻蚀完窄沟道中的聚合物时,宽沟道中仍有部分残留需要等到刻蚀硅阶段继续刻蚀,集中体现在宽沟道区域附近的刻蚀粗糙度增加,使其在肉眼下呈现的颜色偏白。

从表2中分析可知,在钝化和刻蚀聚合物时间比例小于0.6时,刻蚀比例过大,存在刻蚀残留物;当比例处于0.6~0.8时,刻蚀残留现象消失,但存在刻蚀粗糙度问题;而比例达到1附近,刻蚀结果逐渐改善,基本达到预期效果。

根据具体设计调整了钝化和蚀刻时间,使得整体上更厚的聚合物层,同时仍然确保在微通道没有残留物。根据上述实验结果,选择在低刻蚀速率参数下研究刻蚀效果。确定TE2为2.5 s,电镜观察不同TE1刻蚀效果,如图7所示。因为1.5 s的钝化聚合物厚度小于其余两者,导致每次刻蚀会向内倾斜,最终刻蚀结果见图7(a),倾角比其余2个的小2个角度,垂直度降低。在图8中,TE1为2.0 s时,刻蚀面更平整,有利于后续工艺。刻蚀到底部时没有继续向下刻蚀,增加了侧壁与底部的支撑。

(a)钝化时间1.5 s

(b)钝化时间2.0 s

(c)钝化时间2.5 s

(a)钝化时间1.5 s

(b)钝化时间2.0 s

(c)钝化时间2.5 s

晶圆整体使用九点法进行测试,刻蚀深度在1.48~1.51 μm,不均匀度为1.9%,结构形貌如图9所示。

图9 压敏电阻结构形貌图

3.4 高温测试

综合上述实验,改进钝化和刻蚀聚合物时间,选择最佳的刻蚀参数,确定钝化时间为2 s,刻蚀聚合物时间为2.5 s,刻蚀硅时间为2.3 s。此时的刻蚀速率为0.173 μm/loop,刻蚀出侧壁垂直度为88.6°。使用更改后的刻蚀方案制备压敏电阻,最终得到的芯片经过切割、封装后进行了高温测试实验。图10为芯片在温度压力复合平台中的测试过程。测试温度为300 ℃。测试结果如图11所示,从图中对比看出,改进前芯片的最大零点漂移超过0.015 %,改进后芯片的最大零点漂移在0.008%左右,改进后的芯片零点稳定性优于改进前的芯片。

图10 温度压力复合平台测试

图11 电阻条改进前后芯片零点漂移变化率

4 结论

压阻式压力传感器压敏电阻制备过程出现的电阻条深度不均匀、底部形貌差的问题,致使压力传感器在测试过程中暴露出热零点漂移、非线性等影响精度的问题。本文分析了制备硅压敏电阻工艺过程中出现问题的原因,根据Bosch工艺的钝化-刻蚀循环原理,利用控制变量法设计实验对刻蚀工艺时序参数进行优化。通过场发射扫描电子显微镜观察对比不同参数下的刻蚀效果,得出了最佳刻蚀参数钝化时间2 s,刻蚀聚合物时间2.5 s,使得压力传感器在300 ℃环境下热零点漂移率降低了46.7%。

高温环境下传感器的性能测试结果表明:优化工艺后的压力传感器在高温环境下有更小的热零点漂移率,验证了该方案对于提高压力传感器静态性能参数的有效性。本文的工作可以为高精度的压力传感器的制备提供参考方案,有助于解决高温等特种环境下的压力测试需求。