基于DSP和FPGA的静电悬浮加速度计控制器设计

杨世佳,李云鹏

(兰州空间技术物理研究所,兰州 730000)

0 引言

静电悬浮加速度计主要用于卫星精密定轨需要,测量由太阳光压引起的卫星摄动加速度,为卫星定轨和轨道补偿提供数据支持[1]。静电悬浮加速度计是测量航天器受到的准稳态微小加速度的基本设备[2],属于差分电容式惯性加速度传感器,主要由传感器探头单元和测量控制单元两部分组成。测量控制单元的主要作用是对传感器单元的敏感结构进行伺服反馈控制,并采集传感器的电容位移数据和所受的微小加速度数据。测量控制单元主要包括信号采集模块、载波信号产生模块、基准电压产生模块以及主控模块等。

静电悬浮加速度计作为精密测量设备,主要用于测量空间扰动引起的微小加速度,目前关于该领域的研究文献,主要关注于对加速度测量分辨率和稳定性的提高以及传感器的精密加工和装配等,对于静电悬浮加速度计控制系统及控制器相关文献较少。硬件层面一般不会存在较大的差别,例如上海交通大学研制的静电悬浮加速度计中采用TI公司32位浮点型DSP作为六轴微加速度计的控制芯片,用于数据采集和控制算法的实现,其采用模糊PID控制算法,可以根据加速度计的运行情况,实时调整PID控制参数[3]。长春理工大学采用DSP+FPGA的架构来实现加速度计控制器,DSP作为主控芯片,主要用于实现控制算法等,FPGA作为辅助控制芯片,用于实现ADC芯片和DAC芯片的时序控制等[4]。法国的等效原理验证卫星-显微镜卫星(MICROSCOPE),主要载荷也是静电悬浮加速度计[5],其采用单独的接口控制单元用于实现加速度计的数据采集和接口控制,其接口控制单元同样采用的是DSP+FPGA的架构来实现的,主要也是硬件层面的介绍,关于软件算法以及控制策略等介绍较少。

对静电悬浮加速度计这样的高精密测量设备,如何实现加速度信号的采集处理、量程的切换、稳定的反馈控制等,对静电悬浮加速度计的在轨可靠工作至关重要。本文基于DSP+FPGA的架构设计了静电悬浮加速度计控制器,基于此架构,提出了一种工作模式切换控制策略,可以实现加速度计在轨捕获和大小量程切换控制,并设计了一种基于此架构的系统复位控制策略,可以实现双芯片控制器的在轨复位和同步协调工作。针对加速度计特殊应用,设计开发了PID控制算法和FIR数字滤波算法,用于实现对检验质量的在轨稳定控制和数据处理。

1 控制器总体架构设计

数字信号处理器[6]是专门为快速实现各种数字信号处理算法而设计的,具有特殊结构的微处理器芯片。DSP芯片根据数据处理格式的不同,分为定点型和浮点型两种[7]。浮点运算的动态范围较大,加速度计中采用TI公司生产的32位浮点处理器SMJ320VC33芯片。FPGA芯片是现场可编程门阵列的简称,根据FPGA架构的不同,FPGA芯片分为SRAM(static random-access memory,SRAM)型、FLASH型以及反熔丝型[8],SRAM型是一种应用范围较广的FPGA芯片。在加速度计控制器设计中,采用的是国产抗辐射300万门SRAM型FPGA芯片。

基于DSP和FPGA的静电悬浮加速度计控制器整体架构如图1所示。DSP作为主处理器,主要负责系统的初始化和任务调度、工作模式切换控制、数据采集交换、数据处理和组包功能以及1553B总线通信功能和在轨维护功能。FPGA作为辅助处理器,主要承担对时序要求严格的模数转换器(analog-digital converter,ADC)、数模转换器(digital-analog converter,DAC)接口控制、PID控制器、FIR数字滤波器、可调移相控制、1553B总线桥接与DSP数据交互以及DSP加载方式的设置等。

图1 静电悬浮加速度计控制器整体架构Fig.1 The overall architecture of the electrostatic levitation accelerometer controller

DSP芯片的外设包括片外SRAM芯片,主要用于缓存DSP程序和数据。PROM(programmable read-only memory,PROM)芯片作为一种高可靠非易失性存储器,主要用于存储经过反复验证的DSP软件程序,确保DSP能够在轨进行程序可靠加载。基于上述DSP工作特点及功能需求,在DSP外设中,增加一片FLASH芯片,一方面用于DSP软件地面测试,可以反复进行程序烧写。另外,也可以进行软件在轨上注和控制参数在轨重构,从而确保加速度计工作在最佳状态,执行特定的在轨测试任务。

FPGA芯片的外设包括片外FLASH芯片和PROM芯片。由于静电悬浮加速度计中采用的是SRAM型FPGA芯片,芯片掉电后,内部程序丢失,所以为了方便地面硬件调试和软件测试,为FPGA增加一片FLASH芯片,用于地面测试。FPGA软件最终测试完成后,在软件最后落焊前,拆掉FLASH芯片,将测试完成的FPGA软件烧录进PROM芯片。FPGA主要完成芯片时序控制、相敏解调控制以及PID算法和FIR数字滤波算法的实现,加速度计在轨应用时,并不需要对FPGA软件进行修改,所以对FPGA来说,仅仅采用一次可编程的PROM芯片,用于存放FPGA的配置数据,上电时,直接从PROM芯片加载。

DSP和FPGA之间通过地址和数据总线进行连接,进行数据交换,如图1所示。同时FPGA为DSP芯片提供两个硬件中断,分别为数据采集中断和通信中断,DSP为FPGA提供复位信号及外设控制接口。

2 控制器软、硬件设计

如前文所述,为了方便DSP进行程序的存储以及大量数据的存储和读取,在DSP主控芯片电路设计中,外扩了SRAM、FLASH以及PROM芯片,其中SRAM芯片采用法国3D-plus公司生产的宇航级芯片,该芯片内部共有8个基片,每个基片的容量为4Mbit(256K×16),总共32Mbit的存储容量,基地址为0xC00000h。原理如图2所示,包括A1~A17共17根地址线,HA0和LA0两根高位和低位地址线以及I/O0~I/O31共32根数据线。同时,该芯片共有CS0~CS7共8个片选信号。通过将高位地址线HA0和低位地址线LA0连接在一起以及将片选信号CS0和CS4、CS1和CS5、CS2和CS6、CS3和CS7连接在一起,将其拼接成4个容量分别为256K×32的存储空间,用于与DSP进行数据交换,存储加速度计位移检测数据和科学读出数据。

图2 DSP外扩SRAM芯片原理图Fig.2 Schematic diagram of DSP external expansion SRAM chip

FLASH芯片选用美国的Aeroflex公司生产的ACT-F512K8N,共有A0~A16共17根地址线,容量为4Mbit,另外由8根数据线以及1根片选信号和两根读写控制信号,片选信号与FPGA的I/O接口相连,读写控制信号与DSP芯片的读写控制端口连接。DSP的PROM芯片选择北京轩宇的XY28F256,该PROM芯片包括15根地址线,8根数据线,还包括编程使能、片选使能以及输出使能3个控制信号。另外在DSP外扩存储电路设计时,由于PROM芯片和FLASH芯片为5V供电的芯片,SRAM芯片为3.3V供电,所以对于PROM和FLASH,需要在数据接口增加电平转换芯片,使得PROM、FLASH芯片与数据总线接口之间的电平相匹配。

FPGA的外部扩展芯片包括一个用于地面测试时使用的FLASH芯片和一个用于在轨程序烧录的PROM芯片。其中FLASH芯片采用的是Xilinx公司生产的存储空间为16Mbit的工业级XCF16PV0G48C芯片,PROM采用的同样也是Xilinx公司生产的抗辐射高等级16Mbit的XQR17V16芯片。地面上使用时,通过JTAG接口,ISE软件将生成的.mcs文件烧录到FLASH芯片,用于地面上开展FPGA程序测试,包括PID控制算法、FIR数字滤波算法、静电悬浮加速度计高压悬浮测试以及装星电测等,产品正式交付出厂时,再将测试无误的FPGA程序落焊到PROM芯片。

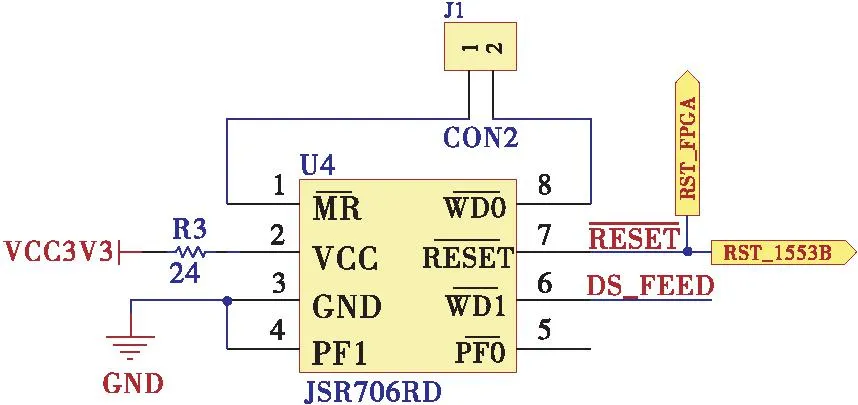

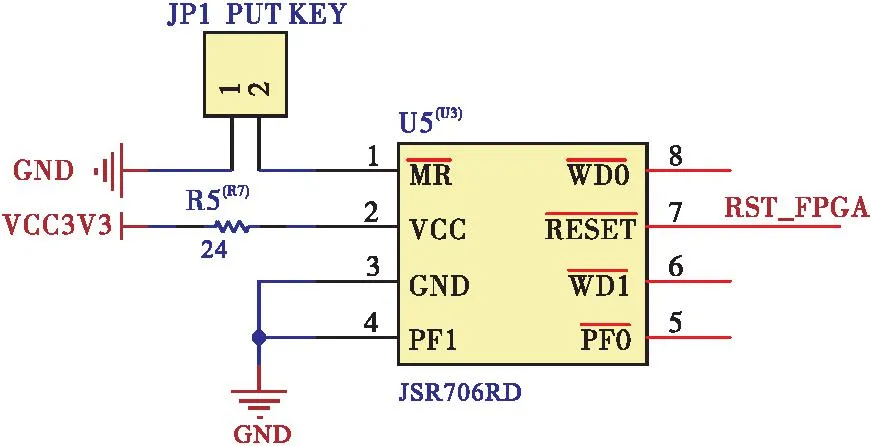

另外基于静电悬浮加速度计的工作特性以及空间环境的复杂性,在静电悬浮加速度计电路设计中,需要着重考虑加速度计控制器中DSP芯片和FPGA芯片的供电和软件监控以及相应的复位逻辑。在该加速度计控制器中,DSP和FPGA芯片均采用中电58所生产的看门狗芯片对两个芯片的上电、掉电进行监控,确保当芯片的电源电压达到一定阈值才进行复位,同时当电源电压下降到一定阈值时,同样也输出低电平复位信号。如图3和图4所示分别为DSP复位监控电路和FPGA复位监控电路原理图,在图3中J1为DSP复位断开接口,用于DSP软件地面分步调试,在图4中JP1为FPGA软件手动复位接口,用于对FPGA软件进行手动复位。

1) 试验时间及地点。试验于2016年4-9月在贵州省安顺市西秀区山京畜牧场烟草根结线虫病发病严重的连作烟地进行。土壤类型为黄砂壤,土壤肥力中等,烤烟种植品种为K326,2016年4月25日采用“井窖式”小苗移栽。

图3 DSP复位监控电路原理图Fig.3 Schematic diagram of DSP reset monitoring circuit

图4 FPGA复位监控电路原理图Fig.4 Schematic diagram of FPGA reset monitoring circuit

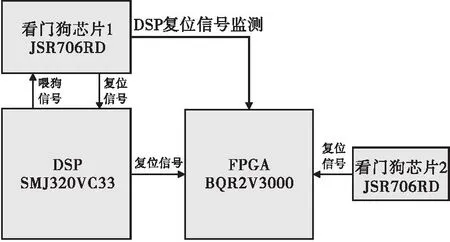

从图3和图4可以看出,整个系统中,不仅包括看门狗芯片1、看门狗芯片2对DSP芯片和FPGA芯片的电源的监控,同时DSP软件运行时,在大于0.3s,小于1s的时间间隔内,向看门狗芯片1周期性的发送喂狗信号,若超过1.6s,看门狗芯片1未收到DSP发送的喂狗信号,则输出低电平复位信号。同时FPGA芯片对看门狗芯片1的复位信号进行监测,当一定周期内检测到看门狗芯片1持续对DSP进行复位(5s内连续复位3次)时,则认为DSP的软件存在一定的BUG,需要配置DSP芯片的加载方式从FLASH切换到PROM启动。DSP还可以通过对FPGA中启动方式寄存器的设置,配置DSP在复位之后,从FLASH或PROM启动,配置DSP从FLASH或者PROM启动,其中看门狗复位信号的检测优先级高于启动方式寄存器的检测。

为了使DSP和FPGA两者运行同步,当DSP软件在上电或者复位完成后,DSP软件在XF1接口置为低电平并保持超过6s时间,等待FPGA配置信息加载完成后,在XF1接口上输出一个脉冲宽度大于1us的高电平脉冲,对FPGA内部逻辑进行复位,脉冲输出后,XF1接口应该保持低电平。如图5所示为加速度计控制器复位逻辑框图。

图5 加速度计控制器复位逻辑框图Fig.5 Accecerometer controller reset Logic Block Diagram

在复位操作期间,一方面需要对系统的1553B通信进行复位操作,还需要对DSP的中断进行操作,防止DSP启动期间,中断有效导致DSP启动失败。

静电悬浮加速度计控制器的软件设计主要包括DSP软件和FPGA软件,根据前文DSP功能和FPGA功能描述,对DSP软件来说,除工作模式切换控制以外,其余的功能均为通用的控制功能,对FPGA软件来说,除基本的ADC、DAC时序控制以及其它的逻辑控制功能外,还需要承担静电悬浮加速度计控制器中PID控制算法和FIR数字滤波算法的实现。下面对DSP工作模式切换控制逻辑以及FPGA的PID控制算法和FIR数字滤波算法的实现进行描述。

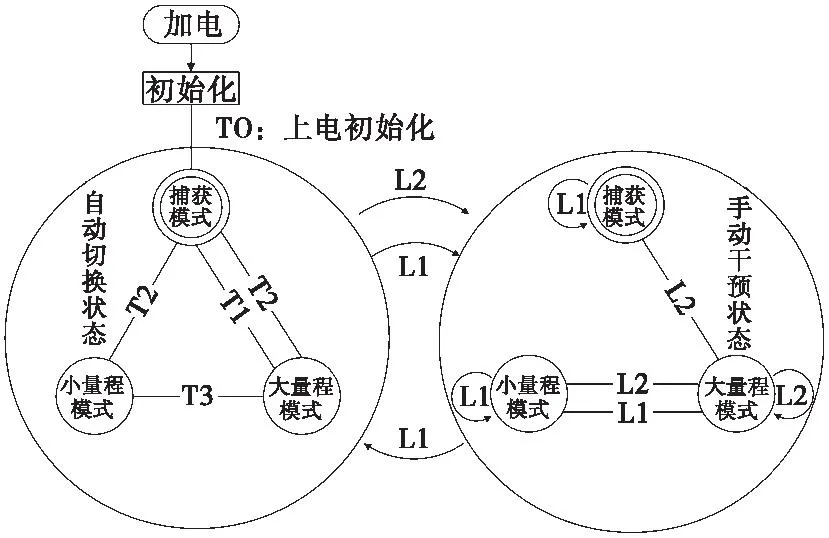

在静电悬浮加速度计中,根据工作环境以及测量状态的不同,将其工作模式分为捕获模式、大量程模式以及小量程模式,其中捕获模式主要用于实现检验质量的在轨捕获控制,其位移检测范围和加速度测量范围较大,但分辨率较低,所以主要应用于加速度计上电初始状态时的检验质量捕获控制和较大扰动情况下的检验质量捕获控制。大量程模式和小量程模式则为测量模式,两种测量模式的加速度测量范围不同,因此测量分辨率也不同。上述三种工作模式的软硬件工作流程和时序是完全一致的,但正弦检测电压、驱动增益以及PID控制参数则存在区别,所以加速度计控制器需要根据工作模式切换逻辑,对正弦检测电压的幅值、驱动放大电路的增益以及PID参数进行切换,从而实现加速度计正常工作和科学测量。三种工作模式之间的转换逻辑如图6所示,根据任务需求的不同,分为手动干预状态和自动切换状态,其中T1~T3为自动切换时需要满足的条件,主要包括持续时间、位移检测输出电压阈值以及PID控制输出电压阈值,若其中一个通道的位移检测电压大于2.4V时,则自动进入到捕获模式,若6个通道的位移检测电压均小于2V时,则进入到大量程测量模式,若6个通道PID控制电压均小于0.5V时,则表明此时检验质量所受的扰动加速度较小,则自动切换到小量程测量模式,进行高分辨率测量。L1、L2为手动干预三种工作模式的进入和退出条件,其中L1为捕获模式和小量程模式的进入条件,L2为大量程模式的进入条件。在图6中工作模式的切换只是适用于某卫星平台的切换逻辑,根据卫星平台、所处轨道以及任务需求的不同,需要专门制定加速度计工作模式切换逻辑,主要原则就是在加速度计正常工作的同时满足卫星测控需求。

图6 工作模式切换逻辑框图Fig.6 Operation mode switching logic block diagram

静电悬浮加速度计PID控制算法主要是确保在不同的工作状态时,控制检验质量位于加速度计电极笼的中心位置,通过调整比例、微分、积分三个方面的参数来达到最佳的系统响应和控制效果,PID控制的基本方程如式(1)所列:

(1)

(2)

u(k)=u(k-1)+kp[e(k)-e(k-1)]+kie(k)+

kd[e(k)-2e(k-1)+e(k-2)]

(3)

整理后:

u(k)=u(k-1)+k0e(k)…+

k1e(k-1)+k2e(k-2)

(4)

其中:k0=kp+ki+kd,k1=kp-2kd,k2=2kd。

根据公式(1-3),得到PID控制算法的FPGA实现逻辑如图7所示:

图7 PID控制算法FPGA实现逻辑框图Fig.7 PID control algorithm FPGA implementation logic block diagram

图7为本文采用的PID控制算法结构相同,该结构为并行结构,在FPGA设计中,相当于以面积换取速度,拥有较快的运算速度,非常适合于加速度计这种对响应速度要求较高的系统。从图7的控制算法框图,可以得到公式(5),其主要是由四个加法器和三个乘法器组成,可以重复利用IP核进行实现,降低了设计的难度。

(5)

式(5)中:r(k)标识设定值,y(k)标识实际值,p0~p2、s1~s2为暂存变量。

FIR数字滤波算法的实现如式(6)所列,FIR数字滤波主要是对科学读出数据进行数字滤波处理,其中x(n)为输入信号,h(n)为FIR数字滤波系数,y(n)为经过滤波后的信号;N表示FIR滤波器的抽头个数,滤波阶数为N-1[12]。

(6)

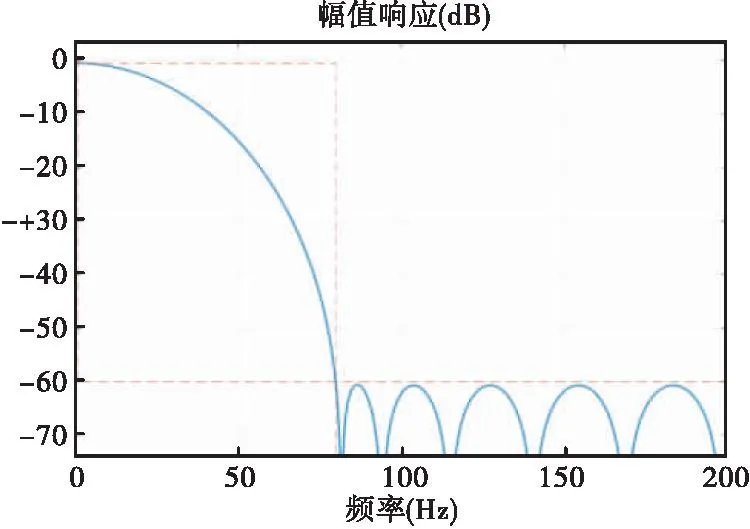

根据静电悬浮加速度计加速度测量频带的范围,采样率为1kHz,滤波器的通带设置为0Hz~1Hz,过渡带为1Hz~80Hz,通带衰减为0.01dB,阻带衰减为60dB。由上述参数,应用MATLAB中的数字滤波器设计工具箱,采用等波纹的设计方法,得到一个最小阶数为43阶(N=44)的FIR滤波器[13-14],数字滤波器的幅值响应曲线如图8所示。

图8 FIR数字滤波器幅值响应Fig.8 FIR digital filter magnitude response

FIR数字滤波器在FPGA中的实现结果如下,主要包括延迟单元Z-1、乘法器和累加器组成,此结构为直接型FIR数字滤波器结构,也称作横向结构[15-16]。如图9所示。

图9 FIR数字滤波器结构Fig.9 FIR digital filter structure

以上对静电悬浮加速度计控制器中几项关键的控制算法进行了描述,工作模式切换由DSP负责实现,采用C语言编程设计,PID控制算法和FIR数字滤波算法则由FPGA实现,采用Verilog语言设计,具体的实现代码不再赘述。

3 实验结果

基于上述对静电悬浮加速度计控制器的设计,整个控制器的设计包括硬件设计以及软件设计,在硬件设计中主要是主控芯片电路的设计、各个存储外设电路的设计以及系统硬件复位电路设计。软件设计则主要是基本控制接口的实现以及加速度计工作模式切换逻辑、PID控制算法以及FIR数字滤波器的实现。其中存储外设的访问、系统复位以及加速度计工作模式的切换逻辑,在本文的实验结果中,不再赘述,其主要是时序逻辑和组合逻辑的实现,在加速度计地面软件测试和在轨工作中,均可以有效实现系统的复位以及工作模式的切换,其中工作模式的切换是由DSP软件实现,再由FPGA的I/O接口控制开关三极管,驱动继电器的切换,进而完成对偏置电压以及驱动增益的切换。

PID控制算法的验证需要通过加速度计地面高压悬浮实验进行验证。加速度计地面高压悬浮实验是通过在检验质量的竖直方向上施加近千伏的高压,抵消检验质量所受的地面重力,采用微位移台,进行地面重力倾角标定。竖直方向的高压会将检验质量一直控制在电极笼的中心位置,水平方向的PID计算结果则可以用来表征此时水平方向上检验质量所受的加速度。如图10所示为加速度计中PID控制算法实验测试结果,图中黑色曲线为Z1通道的位移检测曲线,红色曲线为Z1通道加速度读出曲线(即加速度计驱动电压),蓝色曲线则为Z1通道实际PID控制器的输出曲线,从实验结果可以看出,施加在检验质量上的驱动电压,即放大以及滤波后的PID控制器输出电压,会随着检验质量上某一个方向重力分量的变化而变化,而此时检验质量则始终位于电极笼的中心位置,说明当检验质量的姿态或者受力情况发生变化时,PID控制算法可以实时调整加载在电极板上的驱动电压,进而将检验质量控制在电极笼的中心。如图10所示红色曲线和蓝色曲线的阶梯是由于阶梯调整水平方向的重力分量而产生的。本文采用的数字PID具有参数易更新,算法易迭代,可以满足多种工况下加速度计测控需求,可以通过地面测控站对6个通道的PID控制参数进行更新,相比于滤波算法的验证是将FIR数字滤波器的系数导入到Origin9.0软件里面,在Origin9.0软件里面对上位机采集的数据进行数字滤波,从而得到经过数字滤波的数据。

图10 PID控制算法实际测试结果Fig.10 PID control algorithm actual test results

如图11所示为FIR数字滤波算法实验验证结果,是基于加速度计Y通道的位移检测数据进行验证的,其中黑色曲线为Y通道未经数字滤波的数据,红色曲线为滤波后的曲线,数字滤波器的通频带为0Hz~1Hz,从图11中可以看出,该数字滤波器会大幅衰减频率高于1Hz的信号和噪声,从而减小高频噪声对低频信号的影响,进一步提高加速度测量的分辨率和动态范围。

图11 FIR数字滤波算法测试结果Fig.11 FIR digital filtering algorithm test results

4 结论

本文设计了一种基于DSP和FPGA的静电悬浮加速度计控制器,可用于对空间用静电悬浮加速度计的控制,实现卫星在轨测控任务的需求,包括采用静电悬浮加速度计进行太阳光压的测量、卫星轨道转移以及微推力器标定测试等精密测控任务。基于DSP和FPGA架构设计的系统复位逻辑,可以实现双芯片架构的系统复位,使二者同步工作。另外根据任务需求以及加速度计作为测量设备的工作特性,设计开发的工作模式切换(或量程切换)可以确保加速度计在轨正常工作,且实现不同应用场景下分辨率可调。在该控制器中,为DSP和FPGA主控芯片设计了丰富了外设资源,可以满足静电悬浮加速度计地面高压悬浮标定测试以及开展程序在轨重构和控制参数的在轨上注。开展静电悬浮加速度计控制器的研究和设计,一方面可以为未来开展空间引力波探测等任务积累重要的工程经验,同时也可以为类似科学探测任务提供设计参考。