基于FPGA的千兆以太网端口通信设计

兰 唯,韩延喆,扈 啸

(1.国防科技大学 计算机学院,湖南 长沙 410073;2.长沙人才集团有限公司,湖南 长沙 410073)

千兆以太网广泛应用于视频、音频等实时通信领域,在端对端通信中,数据传输速率以及实时性是通信的核心指标[1]。千兆以太网接口的设计方案通常采用“逻辑控制电路+以太网接口控制芯片”方法[2-5],其中逻辑控制电路基于单片机、FPGA、ARM(Advanced RISC Machines)或DSP(Digital Signal Processing)的逻辑实现。文献[6]物理层使用PHY(Physical)芯片,以太网物理接口使用RJ-45,数据链路层用ARM中的硬核(Gigabit Ethemet MAC,GEM)实现,协议层采用Linux驱动,该方法大量占用ARM运行资源,ARM工作负载重,其相比FPGA可编程方法延时较大。文献[7~8]中的GMII(Gigabit Media Independent Interface)接口在千兆模式下完成发送、接收数据工作。文献[9]自行研发UDP(User Datagram Protocol)网络IP核,兼容GMII、RGMII以及SGMII模式,占用FPGA资源少。文献[10~11]采用“FPGA+PHY芯片+变压器”实现千兆以太网数据传输。文献[12]采用DSP+FPGA架构实现多路串口和以太网通信。文献[13]采用基于FPGA+ARM架构实现千兆以太网接口通信。文献[14~16]通过千兆以太网实现图像、水声和飞行器传感数据的实时采集与传输。文献[17]介绍了基于FPGA采用CRC(Cyclic Redundancy Check)算法进行差错检验。上述文献均未提及标签转发实现多个千兆网口连接设备互通。

本文研究了一种基于FPGA的千兆以太网端口通信,采用基于标签转发的策略,板级采用FPGA逻辑设计实现了高效协议处理,实现端对端数据通信,传输速率达到1 Gbit·s-1,报文转发延时小于100 μs,报文丢包率为0%,数据传输稳定性较高,满足现有项目的实际需求。

1 FPGA实现千兆网口数据通路逻辑

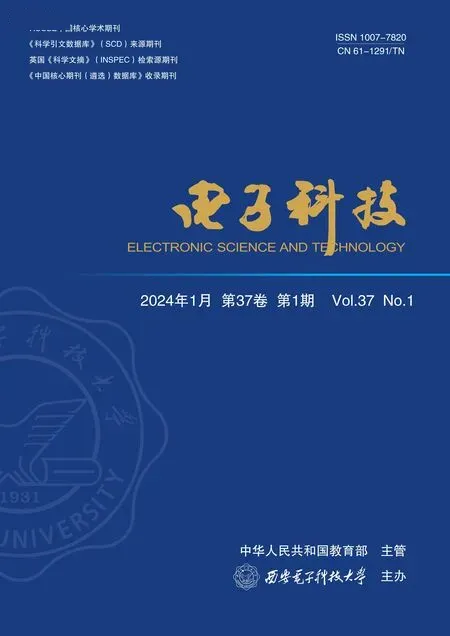

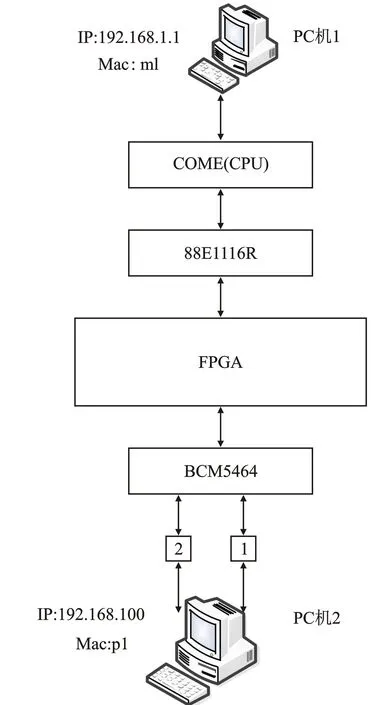

基于FPGA实现千兆网口数据通路的架构主要由COMe(COM Express)卡、PHY芯片、FPGA芯片和RJ45双网口组成。COMe卡集成核心CPU和内存功能,型号为SOM-5894,COMe卡与FPGA之间的PHY芯片型号为88E1116R,FPGA与RJ45双网口之间的PHY芯片型号为BCM5464。FPGA采用Xilinx公司7系列XC7VX690T-2FFG1761C,是系统控制的核心。本文采用了Xilinx FPGA内部的MAC核加外部PHY芯片,在FPGA内部编写逻辑,基于标签转发实现了以太网交换机的转发功能,完成了物理层和数据链路层的通信,实现了端对端数据通信,即COMe卡通过千兆网口与多个千兆网口的连接设备互通。本文基于标签转发的实现过程为:外设通过gmiito139模块的输入端口标记Port0或Port1发送过来的报文,Turncheck模块识别到输入端口后添加标签, 合并为一路后轮询输出给CPU。CPU发出带有标签的数据报文,axito139模块的输入端口标记Port0或Port1发送过来的报文,Portcheck模块139格式报文判断输出端口号,去掉标签,从相应的千兆网口输出数据报文。基于标签转发的工作原理是根据逻辑区分,从相应的千兆端口输出报文。FPGA实现千兆网口数据通路逻辑如图1所示。

图1 FPGA实现千兆网口数据通路逻辑Figure 1.Gigabit Ethernet data path implemented by FPGA logic

由图1可以看出,外设经过多个千兆网口,本文指从Port0、Port1输入报文,经过PHY芯片BCM5464处理后输出SGMII格式的数据,通过FPGA的SGMII IP核转换为GMII格式的报文,将GMII格式的报文转换为139格式的报文。然后内部逻辑添加标签,轮询输出数据,将数据存储到FIFO(First Input First Output ),以AXI4S(AXI4-Stream)接口输出,通过RGMII IP核转为RGMII格式,经过 PHY芯片88e1116R芯片输出给CPU。CPU发出带有标签的以太网报文,通过PHY芯片88E1116R处理后输出RGMII格式的数据。FPGA采用RGMII IP核将RGMII格式的数据转换为AXI格式的数据,将AXI数据转换为139格式的数据,经过内部逻辑判断标签中的输出端口号域并去除标签,然后将139格式转换为GMII格式通过FPGA的SGMII IP核转换为SGMII格式,从相应的千兆网口输出报文,将数据恢复成正常的以太网报文。

1.1 FPGA与外部PHY芯片接口

外部PHY芯片分别指BCM5464芯片和88E1116R芯片,如图1所示。

1.1.1 FPGA与BCM5464芯片接口

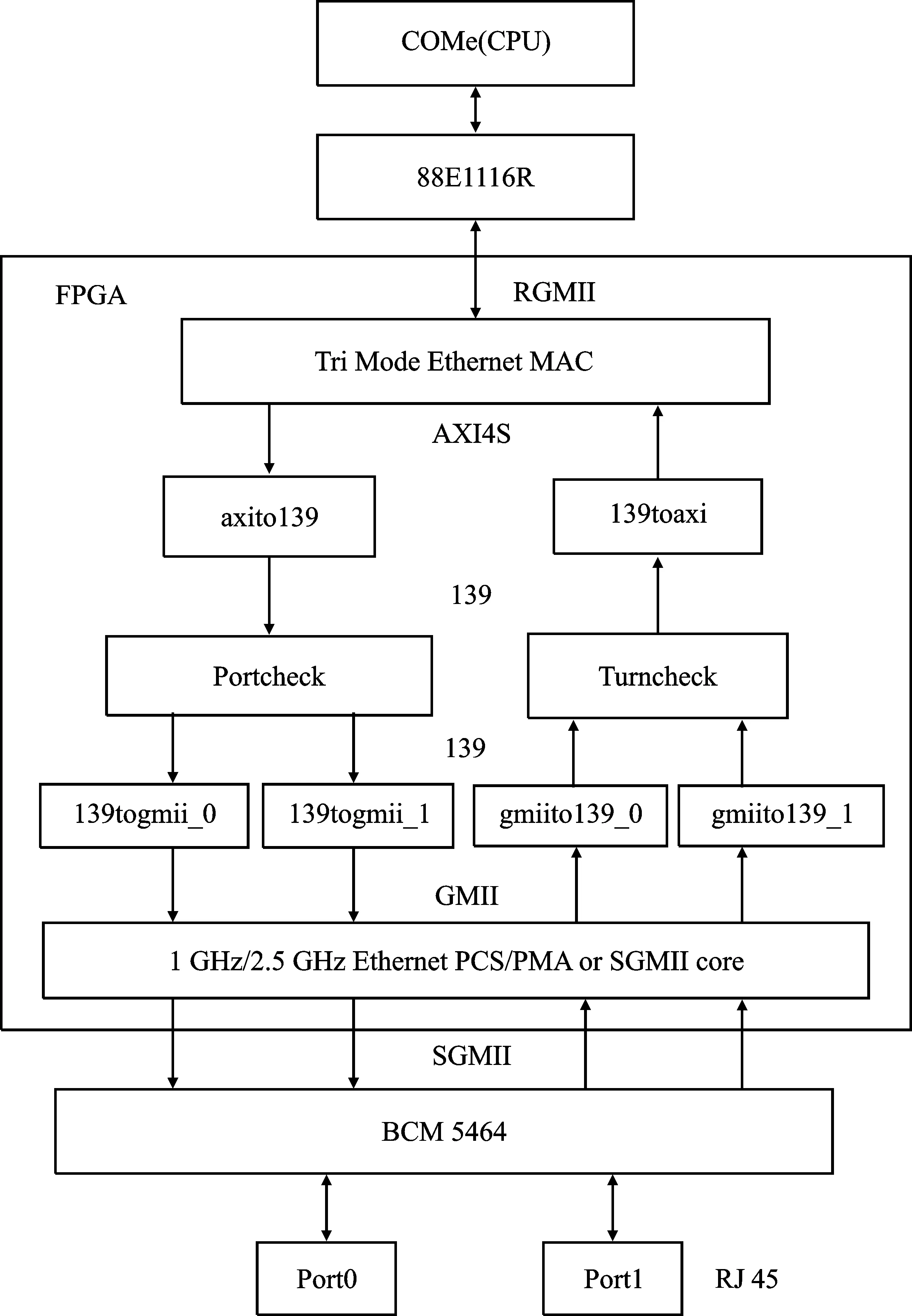

FPGA芯片与PHY芯片BCM5464之间采用的SGMII IP核是1 GHz/2.5 GHz Ethernet PCS/PMA or SGMII Core IP核。FPGA与BCM5464的接口关系如图2所示。

图2 FPGA与BCM5464的接口关系Figure 2. Interface relationship between FPGA and BCM5464

由图2可以看出,SGMII IP核一端利用GTX/GTP/MGT收发器提供串行接口,连接到支持SGMII的以太网PHY设备BCM5464实现,另一端连接到嵌入式以太网介质访问控制器(MAC),从而实现GMII信号与SGMII信号相互转换。也就是将从外设Port0或Port1发送的,经外部PHY芯片BCM5464传输过来的SGMII信号转换成GMII信号或者将从内部逻辑139togmii模块发送的GMII信号转换成SGMII信号。

1.1.2 FPGA芯片与88E1116R芯片接口

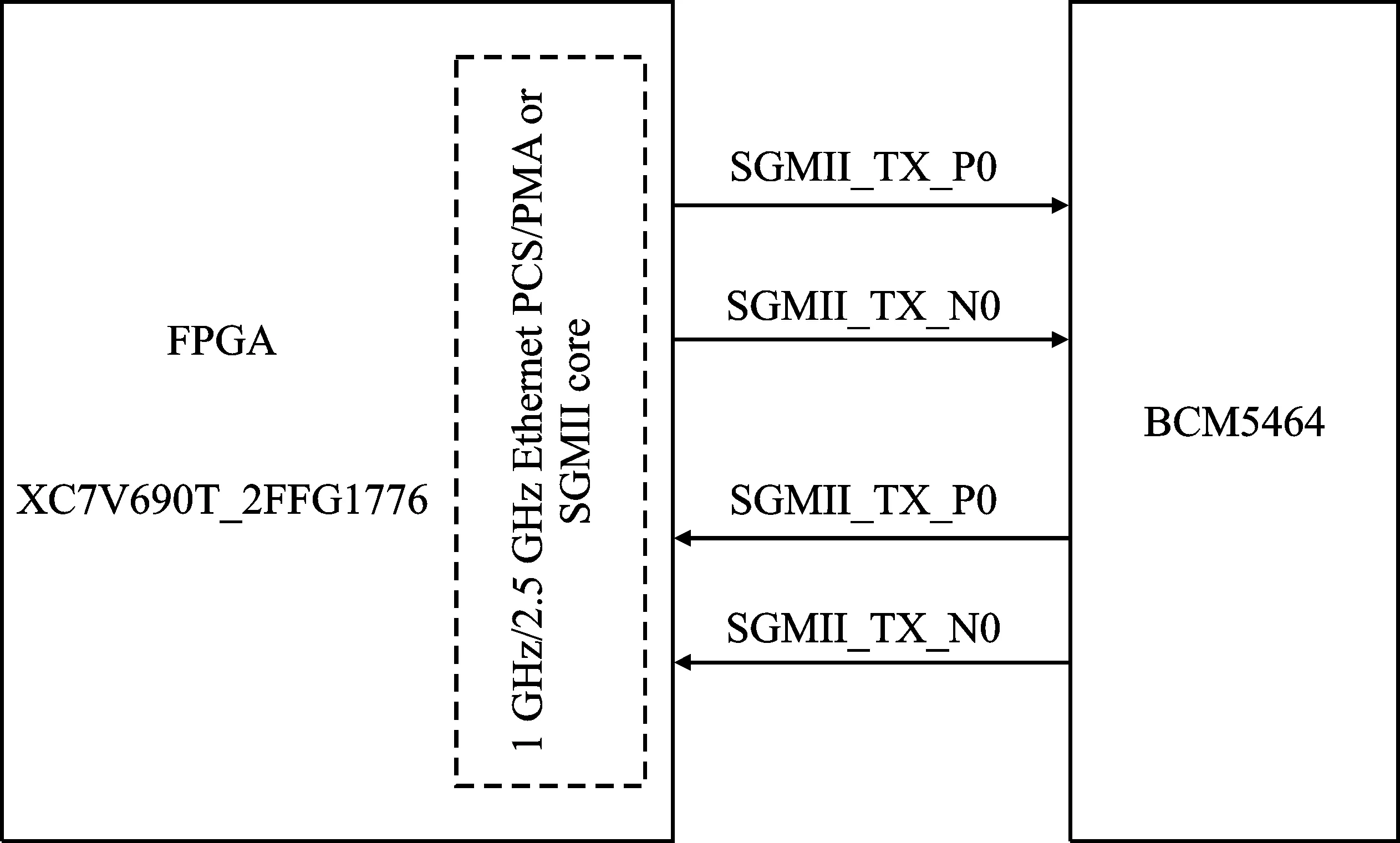

FPGA芯片与PHY芯片88E1116R之间采用的RGMII IP核是Tri Mode Ethernet MAC IP核。FPGA芯片与88E1116R的接口关系如图3所示。

图3 FPGA与88E1116R的接口关系Figure 3. Interface relationship between FPGA and 88E1116R

由图3可以看出,RGMII IP核支持以太网PHY设备 88E1116R,将RGMII信号与AXI信号相互转换,即将从CPU下发并经外部PHY芯片88E1116R传输的RGMII信号转换成AXI接口信号或者将从内部逻辑139toaxi模块接收的AXI接口信号转换成RGMII信号。

1.2 gmiito139模块

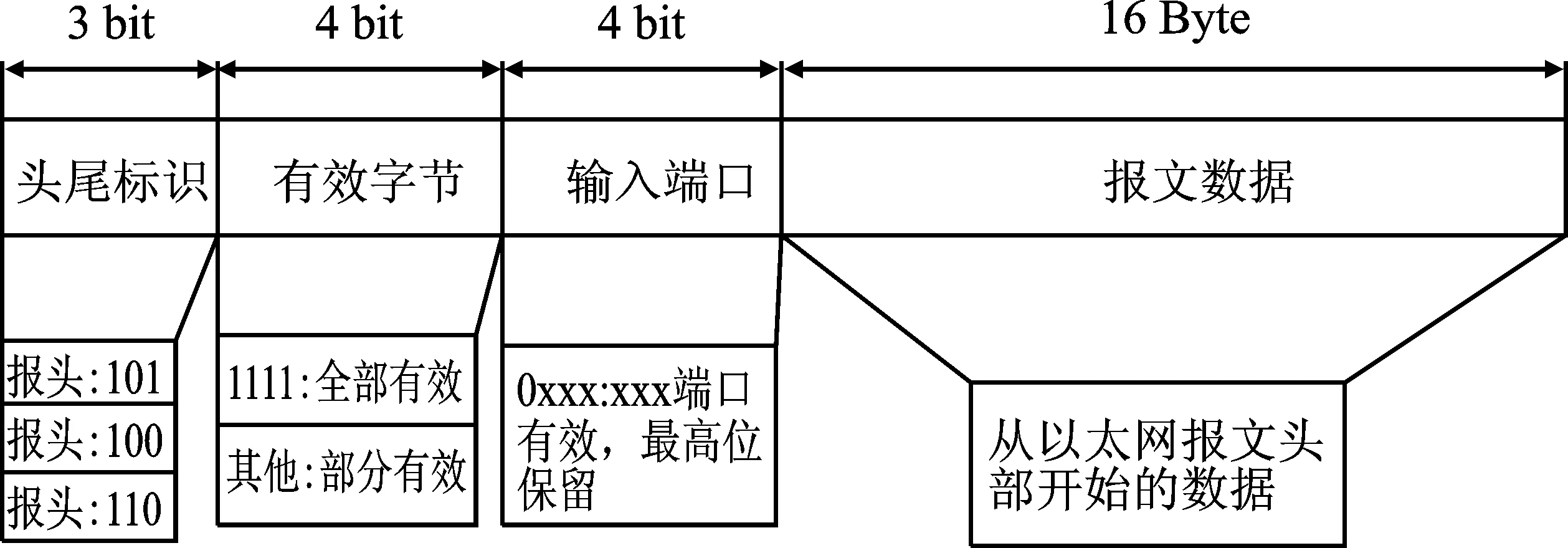

gmiito139模块从SGMII IP核接收GMII信号,然后将GMII信号转换成139位报文格式的数据。139位报文格式如图4所示。

图4 139报文格式Figure 4. 139 bit datagram format

由图4可以看出,139位报文[18]由头尾标记、有效字节、输入端口和报文数据组成。头尾标记为3位,包括101报头数据、100报文中间数据、110报文尾部数据3类。有效字节为4位,1111标记全部有效,其它表示部分有效。输入端口为4位,最高位保留。报文数据为16 Byte,即从以太网头部开始的数据,由以太网MAC帧首部、以太网MAC帧构成。

1.3 Turncheck模块

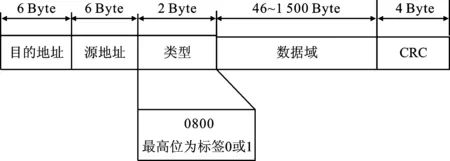

Turncheck模块将外设Port0或Port1发来的经gmiito139模块转换的139格式报文数据进行添加标签,合并为一路后,经139toaxi模块、RGMII IP核送至CPU。标签格式如图5所示。

图5 标签格式Figure 5. Label format

由图5可以看出,标签为4位,以太网类型字段0800的高4位取标签0或标签1,标签0表示 Port0,标签1表示Port1。加标签的目的是根据逻辑区分,从相应的千兆端口输出报文。

1.4 139toaxi模块

139toaxi模块将139格式信号转换成AXI格式信号,即将从Turncheck模块接收139格式的数据,将该数据存储到FIFO,FIFO输出AXI格式的报文数据,将数据发送到RGMII IP核。

1.5 axito139模块

axito139模块将AXI报文数据转换成139格式信号,即从RGMII IP核中取出AXI格式的报文数据,以AXI格式的数据将存储到FIFO,然后以139格式从FIFO中取出数据发送到Portcheck模块。

1.6 Portcheck模块

Portcheck模块将CPU发下的139格式报文判断输出端口号,去掉标签,通过139togmii模块、SGMII IP核输出到相应的输出端口。

2 实验验证

2.1 仿真验证

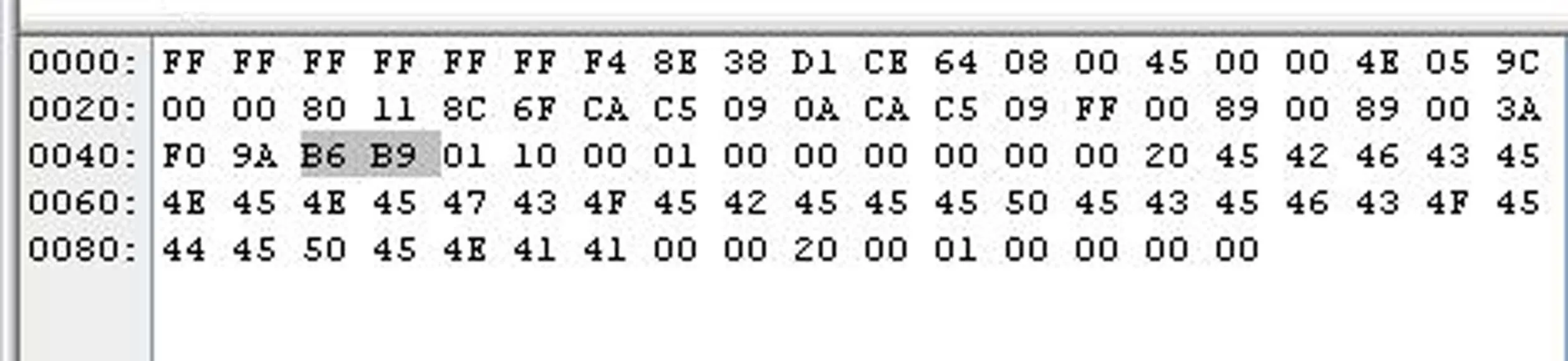

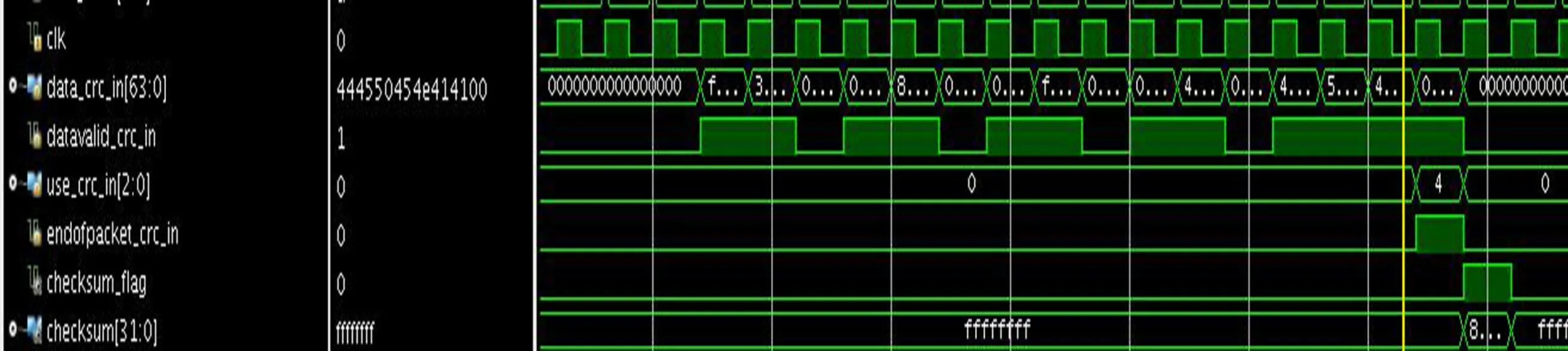

从CPU端发送不同字节的RGMII格式报文,输出端口分别为Port0、Port1,通过逻辑内部在SGMII IP核输出端进行回环,从Tri Mode Ethernet MAC IP核输出的RGMII端口观察RGMII格式报文,报文比对均正确。本文进行了大量仿真实验,报文比对均正确。以其中一个算例进行说明,软件下发的报文如图6所示,仿真结果报文如图7所示。

图6 软件下发的报文Figure 6. Packet sent by software

图7 仿真结果报文Figure 7. Simulation result packet

由图6和图7可以看出,软件下发的报文与仿真结果报文的datavalid_crc_in为1时的data_crc_in[63∶0]数据一致,且软件下发的校验值444550454E414100与仿真结果报文的校验值444550454E414100报文比对一致。

2.2 交换机标签转发功能测试

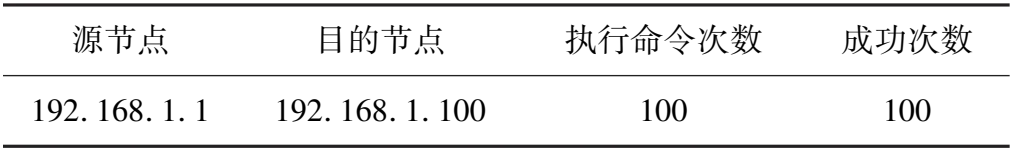

板级调试验证方法1的过程,即交换机标签转发功能测试过程如图8所示。

图8 交换机标签转发功能测试Figure 8. Switch label forwarding function test

由图8可以看出,将逻辑综合实现生成比特流文件下载配置到原型验证平台QPC板的FPGA芯片,FPGA采用Xilinx公司7系列XC7VX690T-2FFG1761C。在 PC 机1上开启 DOS 界面,执行命令操作,即CPU发出的带标签的数据报文,在PC机2使用wireshark软件抓包分析,请求request报文由 PC 机1向PC机2发出,应答reply报文把请求报文的数据返回给PC机1。交换机标签转发功能测试结果如表1所示。

表1 交换机标签转发功能测试记录

由表1可以看出,测试结果丢包率为0%,且报文通过FPGA设计的以太网交换机正常转发,多个千兆网口连接设备互通。

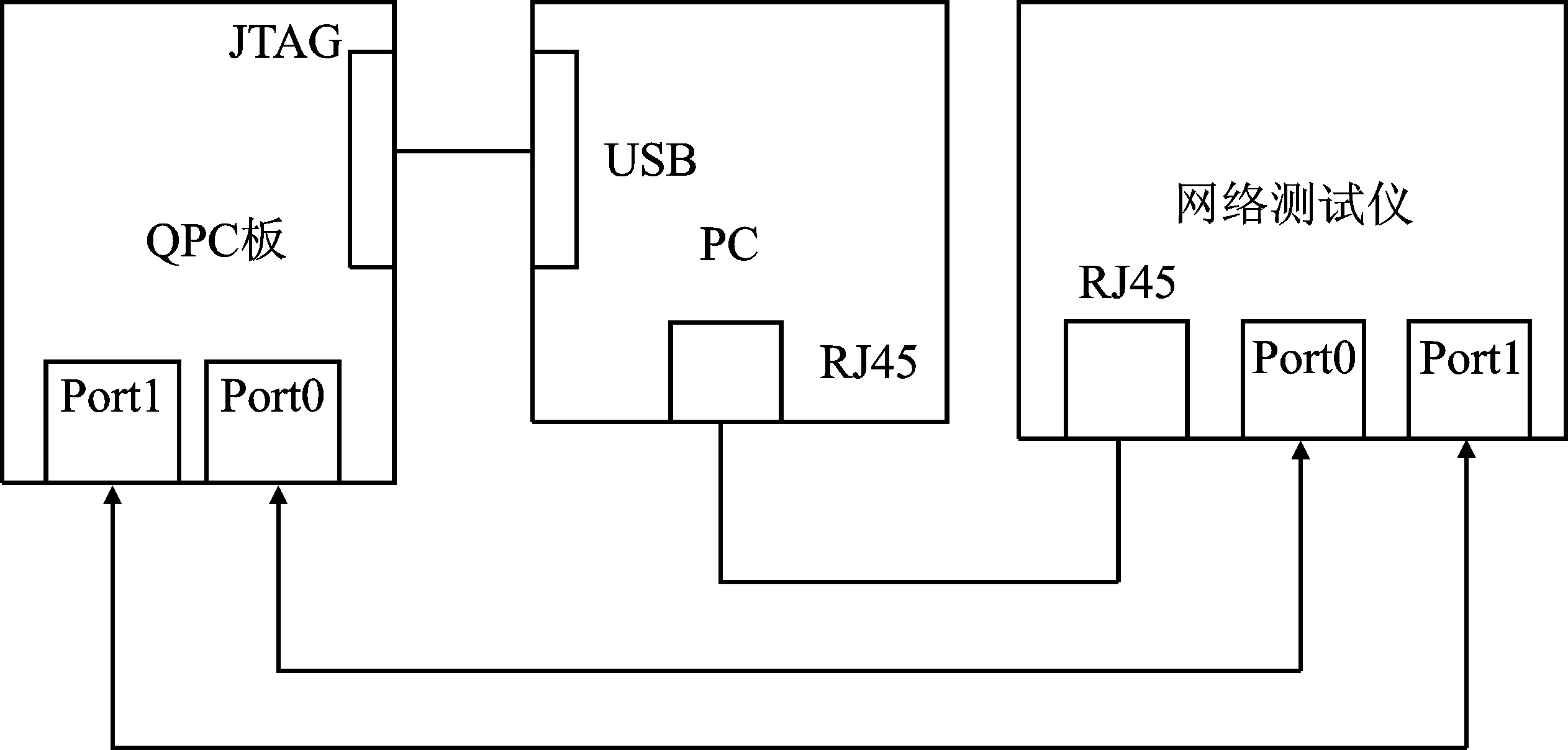

2.3 3项性能测试

板级调试验证方法2的过程,即使用网络测试仪进行3项性能测试过程如图9所示。

图9 3项性能测试Figure 9. Three performance tests

由图9可以看出,QPC板作为FPGA验证平台,PC机通过Xilinx公司JTAG接口下载到QPC板的FPGA芯片XC7VX690T-2FFG1761C内,PC机启动网络测试仪,分别从网络测试仪的输出端口Port0、Port1配置相关参数,通过逻辑内部在RGMII IP核输出端进行回环测试。

2.3.1 接口最高链路速率测试

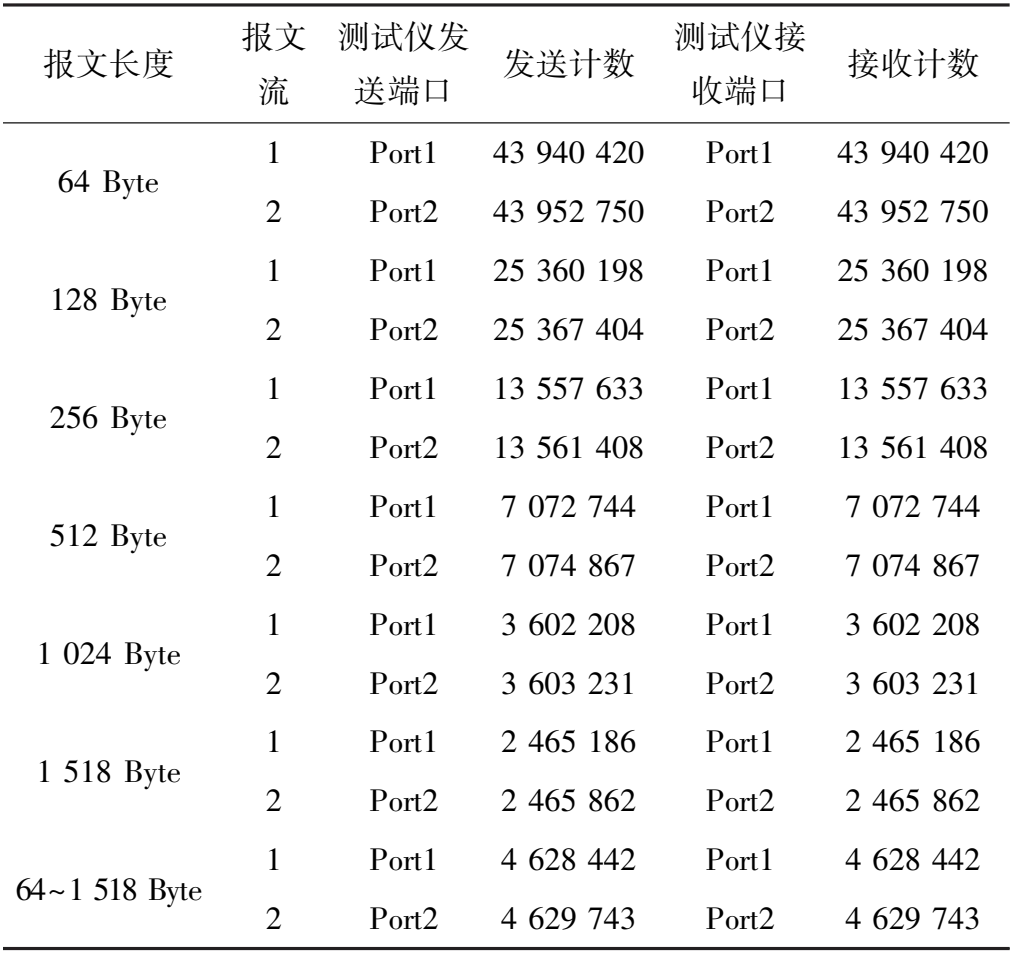

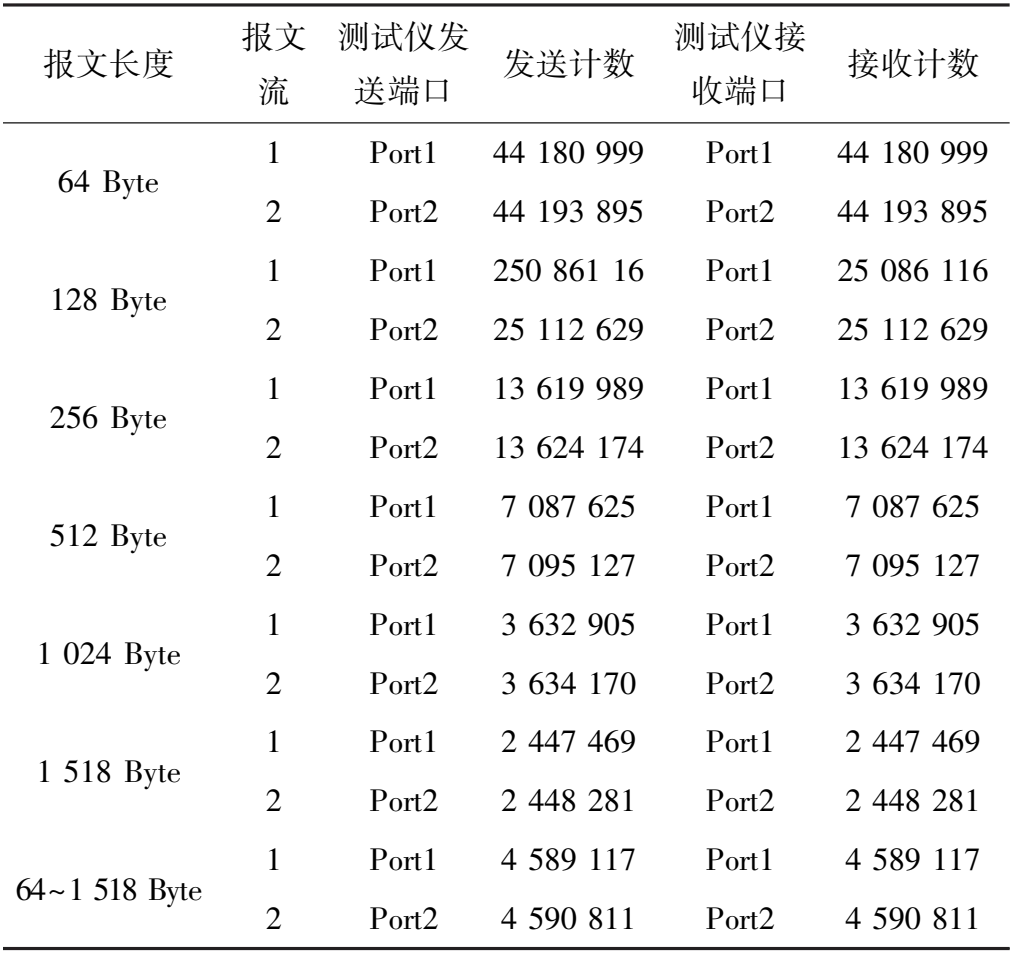

网络测试仪设置链路速率为1 Gbit·s-1的80%,时间设置为30 s,分别对64 Byte、128 Byte、256 Byte、512 Byte、1 024 Byte、1 518 Byte、64~1 518 Byte报文进行测试,链路速率测试结果如表2所示。

表2 800 Mbit·s-1链路速率测试记录

由表2可以看出,当链路速率为800 Mbit·s-1时,从网络测试仪Port0、Port1发出不同帧长度的报文均能返回到网络测试仪端口Port0、Port1,且未丢包,丢包率为0%。当链路速率分别设为100 Mbit·s-1、200 Mbit·s-1、400 Mbit·s-1、600 Mbit·s-1时,丢包率也为0%,本文不再列表详述。

网络测试仪设置链路速率为1 Gbit·s-1的90%,时间设置为30 s,分别对64 Byte、128 Byte、256 Byte、512 Byte、1 024 Byte、1 518 Byte、64~1 518 Byte报文进行测试,链路速率测试结果如表3所示。

表3 900 Mbit·s-1链路速率测试记录

由表3可以看出,当链路速率为900 Mbit·s-1时,从网络测试仪端口Port0、Port1发出不同帧长度的报文,报文均能返回网络测试仪端口Port0、Port1,丢包率为0%。

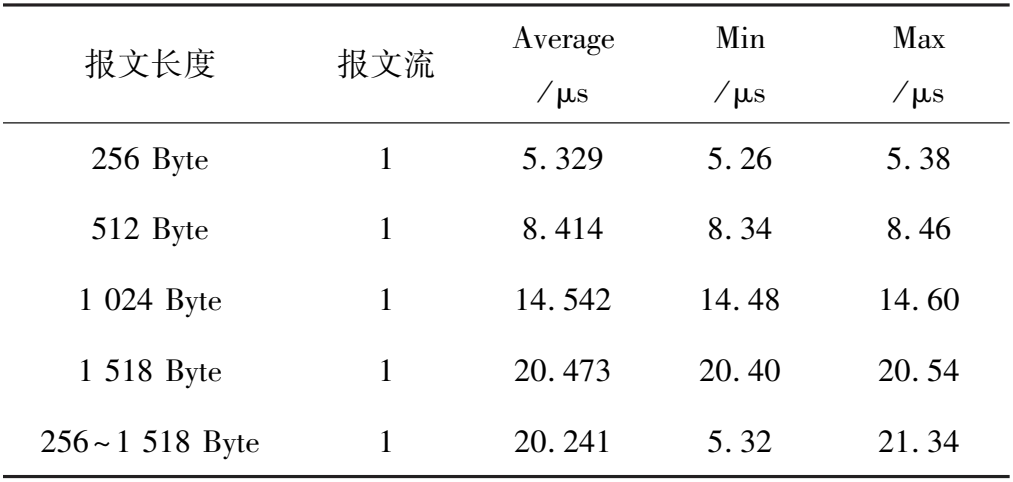

2.3.2 报文转发时延测试

网络测试仪设置链路速率为1 Gbit·s-1,时间设置为30 s,分别对256 Byte、512 Byte、1 024 Byte、1 518 Byte、256~1 518 Byte的报文进行测试,报文转发时延测试结果如表4所示。

表4 报文转发时延测试记录

由表4可以看出,当链路速率为1 Gbit·s-1时,报文转发时延小于100 μs。

2.3.3 报文丢包率测试

网络测试仪设置链路速率为1 Gbit·s-1,时间设置为30 s,分别对256 Byte、512 Byte、1 024 Byte、1 518 Byte、256~1 518 Byte的报文进行测试,报文丢包率测试结果如表5所示。

表5 报文丢包率测试记录

由表5可以看出,当链路速率为1 Gbit·s-1时,从网络测试仪端口Port0、Port1发出不同帧长度的报文,均能返回到网络测试仪端口Port0、Port1,未丢包。

3 结束语

本文采用Xinlinx FPGA内部的MAC核加外部PHY芯片,基于FPGA内部逻辑编写实现了物理层与数据链路层的通信,实现了COMe卡的千兆网口与QPC板多个千兆网口的连接设备互通,实验测试结果验证了FPGA逻辑的可行性和有效性。根据实验验证可以得出,当传输速率达到1 Gbit·s-1时,报文转发延时小,丢包率为0%,数据传输稳定性高,满足现有项目的实际需求。