异构双核处理器失速告警系统设计

魏璐达,宣晓刚,杨 飞,张美仙,贾少龙

(航空工业太原航空仪表有限公司,山西 太原 030006)

0 引言

飞机失速是飞机迎角(angle of attack,AOA)超过临界AOA,机翼升力面出现严重的气流分离,导致飞机阻力急剧增大、升力骤然下降的现象。飞机失速会导致飞机失控,引发飞行事故。为保证飞行安全,民航局适航司规定,要在民用飞机上加装失速告警系统(stall warning system,SWS)[1-2]。飞行员通过SWS获得飞机运行时的失速告警、保护信息,以及相应的控制指令,从而执行相应的操作,以确保飞机不进入失速危险状态。

目前,欧美、俄罗斯等国家和地区的军用和民用飞机加装的SWS大多是基于单核处理器,或者采用多处理器同步时钟的方法构建余度告警计算机,并采用双余度失速告警计算机(stall warning computer,SWC)的方法来满足适航法规对安全性的要求。随着技术的发展,失速判断已经从根据飞机AOA和空速等参数来判断飞机是否进入失速状态,发展到利用AOA、侧滑角、法向过载、空速、突风影响到地效应影响等多种飞行参数进行综合分析和处理。采用单核处理器的双余度SWS,在同一处理器上对解算数据进行数据一致性检查将产生可信度的问题,使输出指令的误判率增加。采用多处理器同步时钟的方法明显增加了计算机系统的复杂度和成本,且设备的基本可靠性平均无故障工作时间(mean time between failure,MTBF)显著降低,难以满足适航安全性要求。

针对以上问题,本文提出了一种基于异构双核处理器的SWS设计方案。该方案在SWS功能的基础上,采用异构双核处理器对解算数据进行监测比对,仅在双核解算的数据一致时才会输出失速告警指令等信息。这样的设计提高了输出指令的准确性,可防止因单核处理器无法在同一处理器上进行数据比对而产生的误操作。这提高了SWS的可靠性和安全性,同时降低了设备的复杂度和成本。

1 SWS功能及架构

1.1 SWS功能

SWS通过在飞机接近失速时向飞行员发送告警和控制信息,确保飞行员及时操纵飞机,使飞机迅速恢复到正常状态来保证飞行安全[2]。SWS一般由AOA传感器、SWC、告警装置等组成[1]。

典型的SWS架构如图1所示。

图1 典型的SWS架构

为了避免飞机侧滑时AOA传感器进入气流遮蔽区,造成AOA传感器测量AOA失真,AOA传感器一般安装于机头两侧的飞机蒙皮表面。AOA传感器采集飞机的AOA信号,在SWC中将修正后的AOA信号与失速告警AOA预设值进行比较。当AOA大于失速告警AOA时,SWC接通告警装置,即振杆器(stick shaker actuator,SSA)。SSA会令驾驶杆抖动,并伴有灯光告警和语音告警来提醒飞行员采取措施,以免飞机进入失速状态。当AOA大于发动机点火预设值时,SWC向发动机控制系统发出点火指令[1,3]。

1.2 SWS架构

为满足SWS的功能,本文设计的SWS由2只AOA传感器、2台SWC和2只SSA组成。其中,AOA传感器用于采集飞机AOA信号并发送给SWC。SWC作为系统核心设备,对采集的AOA信号数据作修正处理,并将机上其他设备(如航电系统、结冰探测系统等)发送的数据进行逻辑运算和分析,以判断飞机是否接近失速。在接近失速时,SWC对外发出告警和保护指令。SSA作为告警装置,根据失速告警指令进行抖振以提醒驾驶员进行操作,避免飞机进入失速状态。本文设计的SWS架构如图2所示。

2 SWC功能与设计

2.1 SWC功能

SWS中的核心控制部件为SWC。SWC通过AOA传感器采集飞机AOA信息,并将采集的信息进行修正从而得到真实AOA。SWC除了接收飞机AOA信息,还需接收飞机上其他系统发送的信息,如马赫数、高度、姿态、襟缝翼构型、结冰等。SWC对接收到的数据进行解算,并根据解算结果判断飞机真实AOA是否接近气动失速。当解算结果得出飞机处于接近气动失速状态时,SWC会发出失速告警、自动点火和失速保护指令,向飞行员提供告警指示,从而保护飞机不进入失速危险状态。

本文设计的SWC具有以下功能。

①SWC向AOA传感器提供激励信号,并接收AOA传感器输出的2路AOA信号。采集到的2路AOA信号作为原始数据用于计算飞机局部AOA。此外,AOA传感器具有加热功能。SWC会监控AOA传感器的加热状态。

②SWC通过数据总线接收外部输入数据;根据接收的数据信息解算AOA、临界AOA和失速速度。

③当真实AOA接近临界AOA或空速接近失速速度时,SWC输出告警驱动信号给同侧SSA和灯光告警、语音告警系统,以提醒飞行员采取措施;同时,向机组告警系统输出告警状态。

④当真实AOA继续增大到失速保护控制AOA,SWC发出保护指令给SSA,同时发出保护状态给机组告警系统。当真实AOA小于失速保护控制AOA一定数值时,SWC停止发出保护指令。

⑤当真实AOA继续增大至点火AOA,SWC持续发出点火指令给左、右发动机;同时发出点火状态给机组告警系统。若真实AOA小于点火AOA一定数值时,SWC停止发出点火指令。

此外,本文设计的SWC还需遵循适航规章、标准和指南。针对运输类飞机,与失速相关的专用条款有《运输类飞机适航标准》(CCAR25-R4)中第25.207条款和《Safety Assessment of Transport Airplanes in Commercial Service》(SAE ARP5150A-2019)附录A表A2等。基于以上描述,提高SWC设计的安全性、降低失速告警指令的误导/无告警的错误率尤为重要。为提高设计的可靠性和安全性,SWC会对解算结果进行监控并对数据一致性进行判断,将AOA信号等关键信息和输出的失速告警指令等信息数据作一致性比较,以输出告警指令、保护指令和点火指令等信息。因此,本文设计的关键是处理器的选择。本文设计采用2个单核处理器或1个双核处理器,以满足对运算结果监测的需求。

2.2 SWC的设计

2.2.1 处理器选择

传统SWS的设计采用2个单核中央处理器(entral processing unit,CPU)构建双余度SWC,以满足系统对于安全性的要求。假设的双CPU机载计算机设备如图3所示。

上述设计对系统的复杂度和成本要求较高,且2个单核CPU的使用给数据一致性的比对带来了困难。此外,在CPU的选择上,单核处理器有其局限性。

这些局限性在于:单核CPU主频的提升已达到工艺加工的极限;在单核CPU中,单一线程不能提高系统的并行性,处理速度相较于双核CPU慢很多;CPU主频的提升带来了功耗的增加,使散热量加大,且目前没有保证CPU正常稳定工作较好匹配的散热系统来更好地处理散热;对于大型功能需求的处理,单核CPU表现出了缺陷和不足[4]。

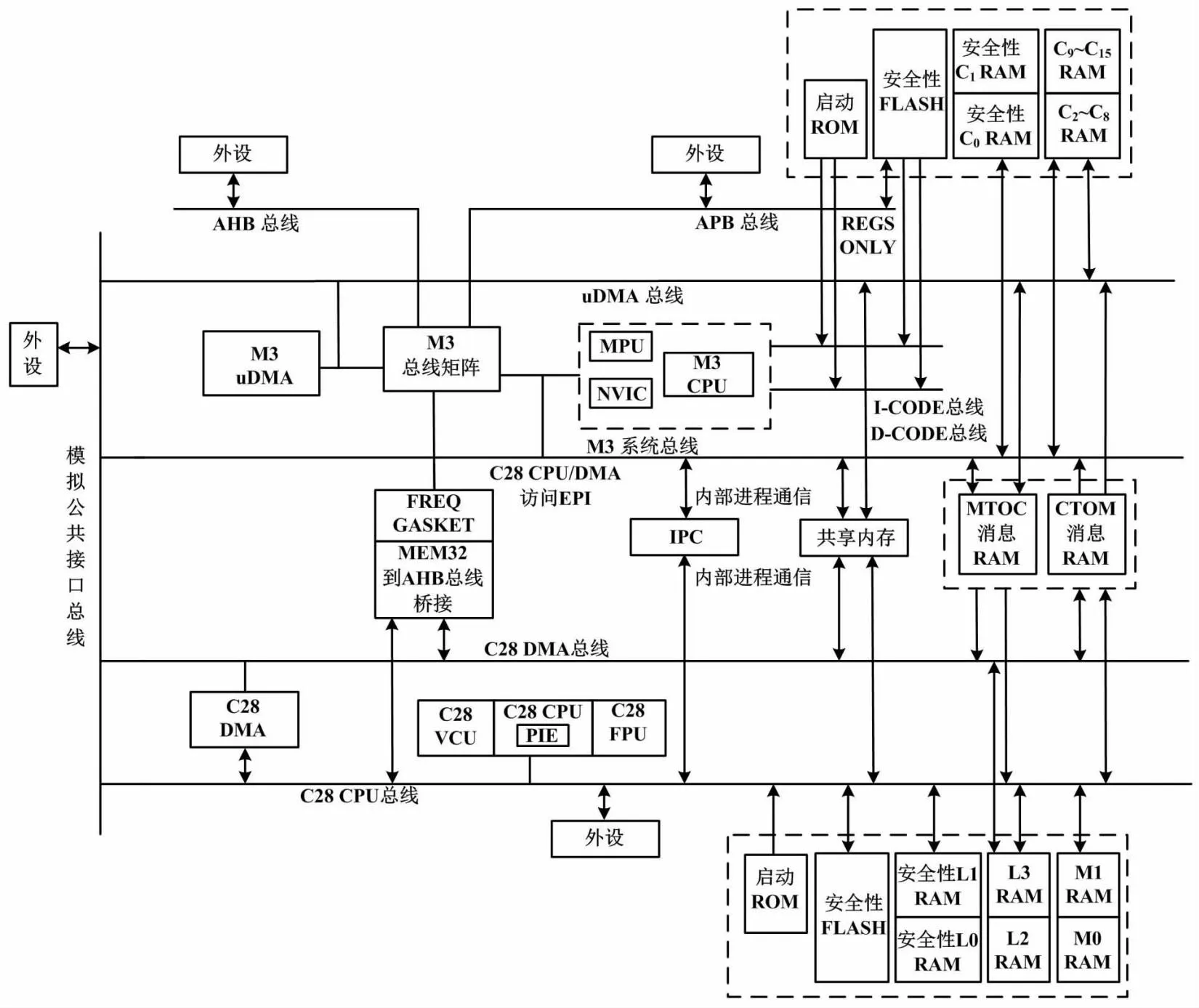

异构双核CPU将2个不同的CPU内核集成在1个CPU芯片中。典型的异构双核CPU架构如图4所示。

图4 典型的异构双核CPU架构

异构双核CPU具有不同结构的CPU内核。2个内核有独自的内存和外设,且拥有各自的系统时钟。双核间通常使用CPU通信接口和共享内存进行数据交互。比较常见的异构双核CPU架构有进阶精简指令集计算机机器(advanced reduced instruction set computer machine,ARM)+数字信息处理器(digital signal processing,DSP)相结合的非对称双核架构[5-6]。异构双核CPU可以大幅提升计算能力,改善性能。将所要执行的任务划分到2个内核中,可在较短的时间内完成任务。这样就能在特定时间内处理更多的任务[4]。同时,异构双核CPU所带来的余度设计提高了系统的可靠性,适用于复杂度高的可靠性系统[7]。

将上述单核CPU局限性和双核CPU优势进行比较,结合SWC对解算结果需要监测和比较的需求,本文选择采用异构双核CPU。其能更高效地实现SWC的功能。相较于采用2片单核CPU,使用1片双核CPU的成本更低。

2.2.2 双核CPU核间通信机制选择

CPU核间通信(inter-processor communication,IPC)用于在2个CPU子系统间进行通信。其原理是2个CPU核之间通过全局共享内存、消息内存、IPC标志和中断,对各内核工作状态和信息进行传递[8]。

常见的双核CPU核间通信机制有信号量、共享内存和消息队列。

信号量是用于解决进程间同步和互斥问题的1种通信机制[4]。而基于共享内存的通信机制则为数据传递提供了1种更为有效的方式,是常用的核间通信机制。

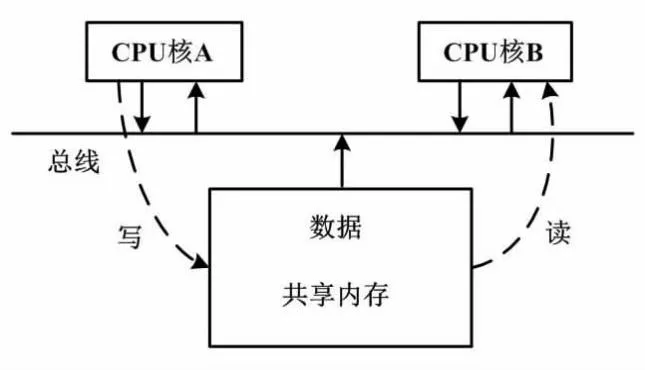

共享内存通信机制的原理是CPU核间共享1块内存。2个内核都可以申请使用这块共享内存进行读写操作。共享内存是数据传递媒介。共享内存通信机制如图5所示。

图5 共享内存通信机制

图5中:CPU核A向共享内存写入数据;CPU核B从共享内存中读取这些数据。这样便可完成核A到核B的核间通信[9]。

核间通信机制为消息队列。它的实质是消息列表。用户可以从消息队列中添加和读取消息,实现2个进程间的数据交换,且发送和接收进程均独立进行。核间通信机制的不足是消息队列中所含数据块总长度有上限[4,10]。

3种核间通信机制中,共享内存是较高效的核间通信方式。共享内存无需对数据进行拷贝,而是直接读写。这在很大程度上提高了通信效率。对比3种双核CPU核间通信机制可知:共享内存方式更为高效、便捷,能提高双核间数据传输速率。因此,本文采用共享内存方式实现SWC中异构双核间的数据交互。

2.2.3 异构双核设计任务分配与实现

SWC中,异构双核CPU执行的所有任务为数据采集和接收。其包含AOA信号采集、ARINC429总线数据接收、离散量信号接收等;接收的数据解析、整理和解算;将接收的原始数据传输给CPU的另一个核;监测数据解算结果的一致性;数据和指令的输出。

通过对CPU所执行的任务进行合理分配,可以在保证满足双核设计需求的前提下最大程度提升双核间通信速率。在任务的分配上,令CPU核A为主CPU、CPU核B为数据监测CPU。双核之间采用共享内存方式进行核间通信,以实现数据传输和监测。核A负责数据的采集和接收;对接收到的数据进行解析、整理和解算;将接收的原始数据写入共享内存中供核B读取,并相应地从共享内存中读取核B解算后的数据。在核A中对核A和核B解算的数据进行一致性判断,如果所比较的解算结果一致,则对外输出解算后的数据和指令。核B负责从共享内存读取核A写入的原始数据并对数据解算,将解算后的数据写入共享内存供核A读取。将任务进行上述分配,并通过使用共享内存进行数据读写操作,从而尽可能实现对程序执行过程的优化。异构双核设计任务分配如图6所示。

图6 异构双核设计任务分配

另外,设计时还需注意保持核A和核B的数据来自同一周期。对于输出的失速保护指令,只有2个内核间解算结果一致且有效时,才可对外输出。整个共享内存机制数据传输过程如图7所示。

图7 共享内存机制数据传输过程

3 其他设计

SWC对航电系统、航资系统等采用ARINC429总线数据的接收方式,对其他系统(如轮载系统)采用离散量总线的接收方式,并根据SWC数据接收方式的不同选择合适的芯片进行外围电路和程序的设计。此外,SWC需要对AOA传感器输出激励信号,在选择好的旋变传感器芯片基础上设计外围电路,通过CPU控制来输出传感器所需的激励信号。

4 结论

本文基于异构双核CPU,设计了具有共享内存通信机制的SWC。SWC作为整个系统的核心设备,在设计时充分考虑安全性能等方面,实现了在同一CPU上对解算结果监控和数据一致性判断的功能。经测试,共享内存通信机制使得数据间交互更加方便、快捷。结合系统设计要求,SWS宜采用共享内存通信机制进行双核间数据监测和数据传输。在其他系统对于余度设计有要求时,可采用异构双核CPU进行双余度设计,以满足系统可靠性、安全性、低成本的设计需求。