基于SystemVerilog 的SoC 系统控制单元的验证

戴兆麟,赵启林,李 超,刘 璐

(1.上海电力大学电子与信息工程学院,上海 201306;2.上海爱思尔教育科技有限公司,上海 200120)

近年来,我国集成电路行业发展迅速,随着工艺制程水平和芯片需求的提高,为了提高设计效率,缩短产品设计周期,同时增强设计模块的可移植性,片上系统(System-on-chip,SoC)成为芯片的主流形式。SoC通常集成有微处理器CPU、存储单元(包括RAM、ROM、FLASH 等)以及各种I/O 接口(包括UART、SD 等),以完成命令处理、数据存储、安全保护等功能。各个功能IP 通过系统总线连接,进行数据交互、功能控制响应。为了高效地协调不同IP 间的互联交互关系,对整个SoC 系统进行控制,以达到硬件资源、芯片面积、能源功耗的统一。在SoC 系统内部总线端设有系统控制单元,通过该控制单元对集成在系统的各个IP 时钟、复位以及特定的功能进行管理。文中介绍了SoC 芯片中系统控制单元的架构与功能,同时构建了基于SystemVerilog 的分层次验证平台,对该控制单元采用以覆盖率为驱动的随机化验证策略进行功能验证,在保证验证准确性、完备性的同时,显著提高验证效率。

1 系统控制单元简介

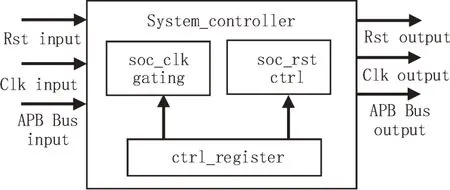

图1 所示为系统控制单元架构,系统控制单元主要由两大模块组成:时钟控制模块(soc_clk_gating)和复位控制模块(soc_rst_ctrl)。时钟控制模块和复位控制模块主要向系统中各个IP 模块输出或停止不同频率的时钟信号以及复位信号。同时可以通过系统总线访问其内置的控制寄存器(ctrl_register),通过读写控制寄存器内容,可以实现CPU 的复位、重映射,使能JTAG,Pflash 写保护控制以及与系统挂载的模拟模块如PLL、OSC 模块进行调配与控制。

图1 系统控制单元架构图

2 基于SystemVerilog的验证平台

SystemVerilog 作为验证语言,提高了代码的生成率、可读性及可重用性。以其面向对象的编程、以覆盖率驱动的验证、受约束的随机激励、断言验证等特性,相比于其他编程语言,更容易实现高效率的以覆盖率为驱动的分层次验证平台。

基于上述优点,文中采用SystemVerilog 完成验证平台的搭建,实现了验证平台层次化、控制功能自动化验证以及各个IP 时钟、复位信号的自动化监测等功能。

2.1 验证平台架构

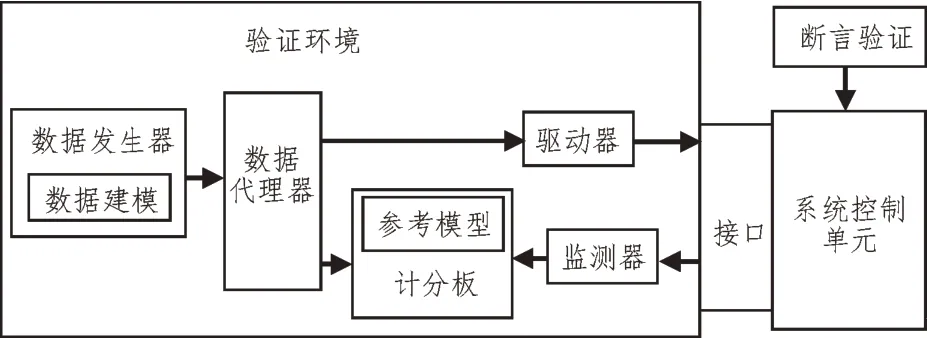

验证平台的架构共有五个基类,分别是驱动类(Driver class)、数据发生类(Generater class)、计分板类(Scoreboard class)、监控器类(Monitor class)、环境类(Environment class),并且提供了断言、覆盖率收集功能,可以更好地使测试用例覆盖代码边角(Code corner),各个组件的数据信息通过邮箱(Mailbox)互通,如图2 所示。

图2 验证平台架构

验证平台可实现产生随机激励、对待测设计施加激励、收集待测设计的响应、比对期望响应与实际响应结果,同时参考代码覆盖率、断言覆盖率等数据,对待测设计的各个功能点进行详尽的验证测试,消除待测设计中可能存在的逻辑错误。

2.2 验证平台的验证方法与实现

在SoC 系统中,系统控制单元的功能可以分为两个主体部分,其一是对系统中部分IP 模块进行控制与数据交互,这依托于系统控制单元的APB 总线端口与其内部的控制寄存器;另一部分则是为挂载于总线的各个IP 模块提供时钟与复位信号。故而对于系统控制单元的功能验证点也主要分为两方面,一方面是验证系统控制单元能否通过APB 总线对内部的控制寄存器进行正确的读、写操作,从而对挂载于总线上的各个IP 模块进行配置与控制;另一方面则是验证系统控制单元是否能准确地将时钟与复位信号输出到各个IP 模块上。

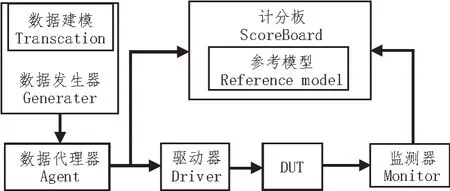

控制寄存器功能的验证流程如图3 所示,数据发生器(Generater)依托于数据建模(Transcation),可以产生特定或随机的数据,数据产生后首先传送到数据代理器(Agent)中,数据代理器再将所得数据分别发送给驱动器(Driver)和计分板(ScoreBoard)中的参考模型(Reference model),采用数据代理器可以避免因发送时序等因素造成数据混乱或错误。数据传给驱动器后,驱动器以符合APB 传输协议的方式将数据传输给系统控制单元。同时计分板将数据代理器发送与监测器(Monitor)接收的数据储存在计分板内部控制寄存器参考模型中,计分板将完成“写入数据”与“读出数据”的自动化比对,打印比对错误的数据内容,并完成错误数据数量的统计,以此来验证控制寄存器写入、读出数据的准确性。

图3 控制寄存器功能的验证流程

时钟以及复位信号的验证方法如图4 所示。通过在验证平台插入断言以及监测器对接口信号进行监测可以快速准确地定位系统控制单元时钟、复位信号的错误。对于复位信号,断言首先监测输入进系统控制单元的复位信号,随后在IP 模块使能复位后监测该复位信号是否如预期变化,最后统计断言失败的数量,以此来验证复位信号的正确性。而对于时钟信号,监测器保持对输出时钟信号的端口进行采样,验证平台通过对仿真时间内采样到的时钟信号边沿数量和系统仿真时间进行计算,得出该输出时钟的频率,并与计分板中预设的标准时钟进行自动化比对并打印对比结果,由此来验证时钟信号的准确性。

2.3 验证结果与分析

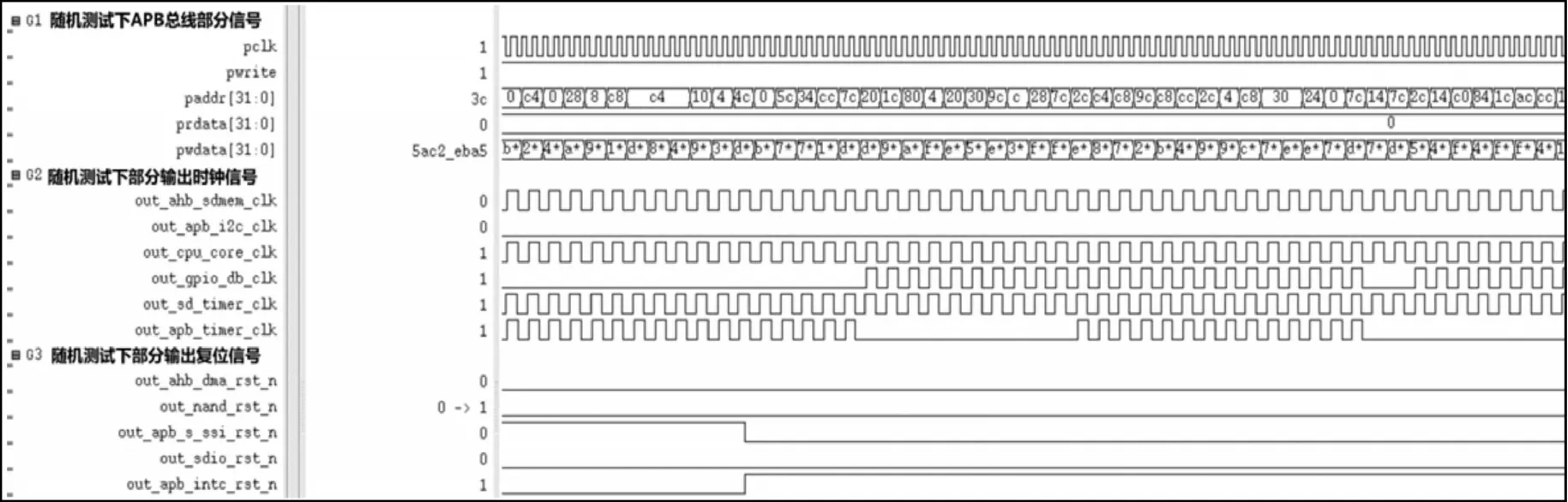

在验证平台中,APB 总线数据通过驱动器发送给待测设计,时钟以及复位信号也是由验证平台输入到系统控制单元,图5 所示为在一随机测试用例的驱动下系统控制单元的部分信号波形。

图5 随机测试下部分信号波形

图5 所示波形为随机数据测试用例,在APB 总线接口上采用地址随机、数据随机、读写随机的测试方法,验证平台将随机数据输入到系统控制单元,同时不断比对控制寄存器输入与输出的“写数据”、“读数据”。对于输入时钟采用同一频率,对应的输出时钟信号受内部控制寄存器控制,决定输出时钟信号或输出低电平,复位信号也是受不断被读写的控制寄存器决定拉高或者拉低。通过这样的随机测试对直接测试未涉及的代码部分或功能进行测试验证,可以提高验证的完备性,加快了验证项目的进度。

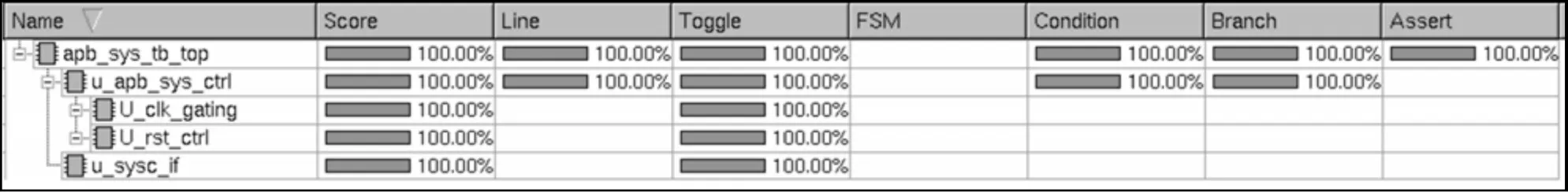

代码覆盖率是衡量验证平台测试进度的一个重要指标,包括分支覆盖率、语句覆盖率、翻转覆盖率、条件覆盖率以及状态机覆盖率,通过代码覆盖率这一指标可以直观地衡量模块验证的进度。系统控制单元的验证以覆盖率为驱动,保证了验证的完备性。经过各种直接测试与上述的随机测试,同时去除掉涉及DFT 验证和一些不影响设计、验证结果的部分后,该系统控制单元的代码覆盖率达到100%,监测复位信号的断言覆盖率也达到了100%,如图6所示。

图6 系统控制单元覆盖率

在保证自动化打印的时钟功能验证、控制寄存器功能验证结果正确以及断言全部成功执行的前提下,该验证平台完成了对系统控制单元充分的验证,确定了该系统控制单元功能完备且准确,设计符合预期。

3 结论

以系统控制单元模块的验证为核心,介绍了SoC 系统控制单元的架构与功能,同时建立了层次化的验证平台,采用基于覆盖率驱动和断言的随机化验证方法完成对该系统控制单元功能点的分类分层次验证。相较于传统验证平台,凭借验证组件的高度模组化和以覆盖率驱动、随机化验证的策略,该验证平台不仅可以移植应用于同一数据传输协议的不同类模块验证,提高了验证平台的复用性,还保证了待测设计的验证完备性和较高的验证效率,为SoC 系统模块的验证提供参考。