一种支持高清晰度多媒体接口固定速率链路训练的装置设计

林巧珊

(作者单位:深圳国实检测技术有限公司)

1 研究概述

高清晰度多媒体接口(High Definition Multimedia Interface, HDMI)作为消费性电子产品中领先的影音传输接口标准,整合了数字化影像和声音传输,用一根线材即可同时传输音频、视频信号,在各类接口应用中占据领先地位。随着电子产品影音消费市场对于高画质影音应用需求的日益增加,4K/8K超高清电视机越发普及。尤其随着8K超高清电视机拥有的7 680×4 320分辨率、高动态范围成像(High Dynamic Range Imaging, HDR)、BT.2020标准的色域范围、12 bit的量化深度、120 fps的频率以及22.2声道的环绕立体声技术的融入,8K超高清电视在视听呈现能力上较普通高清电视有了巨大飞跃,画面的清晰度、真实感和表现力均有了极大提升,8K超高清已成为现行电视行业技术的最高标准。为了承载海量超高清的音视频数据,国际协会标准化组织新发布的HDMI2.1标准[1],加入了全新的固定速率链路(Fixed Rate Link,FRL)传输模式功能,扩展了其信道带宽,可实现更高的分辨率、更宽的色域、更高的帧率、更强的对比度,满足消费者对极致视听效果的追求。

在HDMI2.1标准[1]发布前,影音传输领域多使用传统的最小化传输差分信号(Transition Minimized Differential Signaling, TMDS)架构来进行信号的传输,最高带宽可达18 Gbps,可用来传送每帧像素为3 840×2 160分辨率的4K高画质图像。而新的FRL传输模式可将带宽提升到48 Gbps,在非压缩模式下可以传输每帧像素为7 680×4 320分辨率的高画质图像,在压缩模式下可以传输每帧像素为10 240×4 320分辨率的高画质图像,更适合超高清多媒体技术的快速发展需求。

2 FRL链路训练介绍

2.1 HDMI FRL信道传输模式

在传统的TMDS架构下,HDMI传输方式是利用一个独立的通道来传送时钟信号;但在FRL的架构中,则是将时钟信号嵌入数据信号中,再通过时钟恢复的处理方式恢复出时钟信号,因此就多一条信道来传送数据,带宽便获得大大提升。

此外,在FRL架构下引入新的物理层传送方式,TMDS使用的是8 b/10 b编码方式,而FRL使用的是16 b/18 b编码方式,改善了9%的编码效率,这进一步提升了信道带宽的使用率,可以让通道传输更高的分辨率图像或更高刷新率的图像,为用户提供更好的影音质量体验。

HDMI2.1 FRL除了在高速信号传输架构上作了改变,在低速信号显示器数据通道上传输的扩展显示器识别数据(Extended Display Identification Data, EDID)以及状态和控制数据通道(Status and Control Data Channel, SCDC)也重新定义了原本的保留字段,用于标识FRL模式的功能属性,而这些低速信号的交换在FRL的链路训练过程中承担着极其重要的作用。

2.2 FRL链路训练过程

在FRL架构下,需要通过链路训练的方式来决定接收端与发送端设备之间的传输数据速率。以下是FRL链路训练过程的简化描述。

首先,发送端读取解析接收端的EDID,确认接收端是否支持FRL模式,如不支持FRL传输模式则回到传统的TMDS传输模式。

其次,支持FRL传输特性的接收端,通过写入SCDC状态标志中的固定速率链路训练准备,来通知发送端可以进行链路训练。当发送端查询到固定速率链路训练准备值被设定后,即可设定要输出的FRL数据速率和支持的通道数,以及前向反馈均衡的参数值。

再次,支持FRL传输特性的接收端会要求发送端输出相对应的链路训练模板,双方确认无误之后才可进入正式的FRL信号传输。HDMI设备在支持FRL模式下,接收端与发送端在首次建立链接时需要进行链路训练;HDMI设备更新FRL速率也是需要进行链路训练。

最后,如果FRL链路训练失败,则会开启TMDS传输模式。

2.3 FRL链路训练测试过程中存在的问题

在当前的FRL架构下,具备HDMI2.1 FRL功能的产品(如电视机、机顶盒)在用户使用过程中,不涉及物理层信号完整性的测试,用户更聚焦在产品功能是否正常。例如,传输一个8K的视频,用户只关心这个8K视频在电视上能否正常显示,或者显示效果是否满意,而不关心产品的物理性能,这导致了物理层信号完整性测试手段的缺失。

FRL的电气特性测试和TMDS的程序不同,过往执行TMDS的电气特性测试时,发送端设备只要可以正确读到EDID,就可以输出TMDS信号,因此在测试过程中可以用显示器来取代EDID仿真器。但是发送端在FRL测试除了要读到EDID,还需通过链路训练程序,因此无法透过显示器来仿真这道程序,电气测试也会较复杂。

另外,HDMI2.1 FRL功能产品在进行设备测试时,需要在链路训练过程中或者完成后才能完成相关的测试,这种测试机制是HDMI2.1规范[2]定义的。例如,支持HDMI2.1 FRL功能的发送端产品,需要在链路训练阶段进行相关的信号完整性测试;支持HDMI2.1 FRL功能的接收端产品,需要在链路完成后才能进行相关的信号抖动容限测试。然而,通用的测试仪器,如任意波形发生器、高速示波器只具备信号采集及分析、码型产生的功能,而不具备HDMI2.1 FRL的链路训练功能,无法诱导被测产品发出相关的测试码型或使被测产品进入误码测试状态。因此,在当前的技术下,链路训练过程需要依赖第三方设备协助才能完成,这也降低了设备的测试效率。

3 支持HDMI2.1 FRL链路训练的测试方法的目标模拟装置设计

为了解决FRL链路训练存在的问题,本文着重设计一种支持FRL链路训练的测试方法的目标模拟装置[3]。该链路训练的设备测试方法应用于HDMI2.1 FRL的场景下,用于在物理层测试中实现HDMI FRL的状态控制及实现链路训练,并配合任意波形发生器或者高速示波器,完成HDMI2.1 FRL的接收端设备、发送端设备或中继器设备的目标测试。

3.1 目标模拟装置介绍

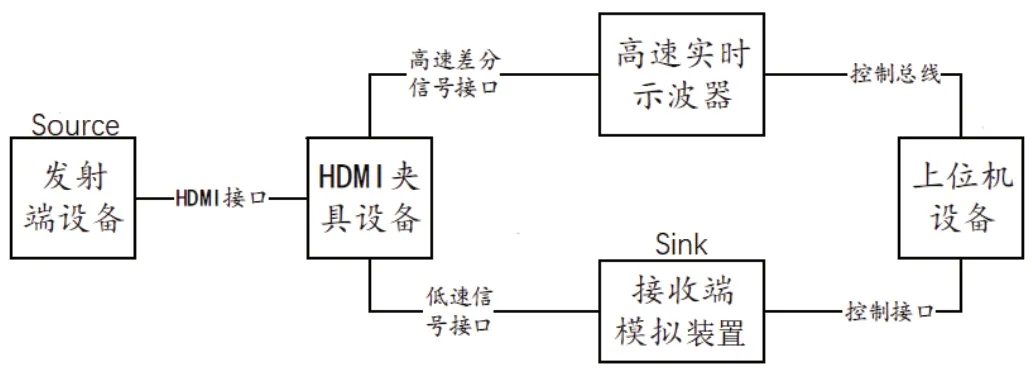

本文提出的一种目标模拟装置设计框架如图1所示,主要包括:

图1 目标模拟装置设计框架

第一,微控制器:包括但不限于嵌入式处理器,微控制器还包括存储单元,存储单元中保存有上位机控制程序和应用程序编程接口函数。

第二,HDMI低速接口设备:HDMI低速接口设备与微控制器连接,它用于与外界的HDMI夹具设备进行连接,从而利用应用程序编程接口函数来建立与目标设备的连接,进而实现对目标设备的测试。

第三,通用串行总线(Universal Serial Bus,USB)接口设备:USB接口设备与微控制器连接,它用于与上位机设备、任意波形发生器或高速示波器连接,上报数据信道数据、电压数据、热插拔检测状态数据,或接收上位机等发送的控制命令给微控制器。

第四,工作状态指示设备:工作状态指示设备与微控制器连接,它用于向用户指示目前该目标模拟装置的工作状态信息,包括主机状态、从机状态。若目标设备为接收端设备,则目标模拟装置为发送端模拟设备,此时目标模拟装置的工作状态信息为主机状态;若目标设备为发送端设备,则目标模拟装置为接收端设备,此时目标模拟装置的工作状态信息为从机状态。

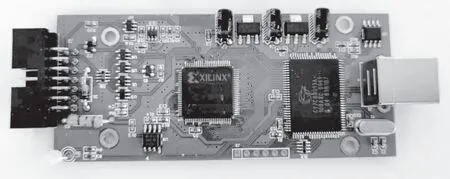

最终开发出来的HDMI目标模拟装置样图如图2所示,样机采用了CY7C68013A-128AXC芯片,该芯片是一款由英飞凌科技生产的USB接口芯片,它被广泛应用于各种USB接口设备中,具有高性能和低功耗的特点,它采用了8位8051内核,主频为48 MHz。该芯片还配备了16 kB的内存,以满足各种应用需求。此外,为了满足后续接口、功能的扩展,样机内置了一颗赛灵思的可编程逻辑器件芯片。

图2 目标模拟装置

3.2 基于HDMI2.1 FRL链路训练的测试方法介绍

下面分别以不同目标设备类型,详细介绍具备HDMI2.1 FRL功能的设备链路训练测试方法:

3.2.1 HDMI2.1 FRL的接收端设备链路训练测试方法

当目标设备为接收端设备,那么设定的目标模拟装置则为发送端模拟装置,目标模拟装置功能应包括电压输出功能、热插拔检测状态检测功能、显示器数据通道总线主机功能、EDID信息解析功能、SCDC信息解析功能[4]。测试方法连接如图3所示。

图3 接收端设备链路训练测试方法连接图

首先,根据目标模拟装置对目标设备进行链路训练,得到训练结果信息,包括发送端模拟装置启用EDID信息解析功能,以读取接收端设备的EDID数据;EDID数据用于判断接收端设备是否支持FRL功能,若接收端设备支持FRL功能,则发送端模拟装置启用SCDC信息解析功能,以读取接收端设备的SCDC数据的状态标志位中的准备状态数据;准备状态数据用于表征接收端设备是否准备好进入训练状态。若检测到固定速率链路训练准备状态数据等于1,则发送端模拟装置将预设的训练数据写入接收端设备的SCDC数据的接收端配置寄存器中;训练数据包括FRL功能的数据速率值、通道数量、前向反馈均衡的参数值,发送端模拟装置读取接收端设备的SCDC数据中的训练测试码型请求数据,发送端模拟装置根据训练测试码型请求数据控制高速任意波形发生器生成训练测试码型数据。若检测到训练超时或训练测试码型请求数据不符时,则停止链路训练并生成训练结果信息。

其次,根据训练结果信息对目标设备进行目标测试。若训练结果信息为训练已完成,则发送端模拟装置控制高速任意波形发生器生成目标测试码型数据,接收端设备的SCDC数据的状态标志位中的通道锁定数据为1,则上位机通过发送端模拟装置读取接收端设备的SCDC数据的字符错误检测寄存器,以得到误码率数据;根据误码率数据和预设的误码率阈值得到抖动容限测试的结果。

以上即为通过对接收端设备进行抖动容限测试的应用来阐述基于HDMI2.1 FRL功能的链路训练和目标测试的过程。目标模拟装置模拟为一个发送端模拟装置的设置下,配合任意波形发生器产生的测试码型,可以对支持FRL特性的HDMI2.1 接收端设备完成链路训练与相关的码型接收容限测试。

3.2.2 HDMI2.1 FRL的发送端设备链路训练测试方法

当目标设备为发送端设备,那么设定的目标模拟装置则为接收端模拟装置,目标模拟装置功能应包括电压检测功能、热插拔检测信号输出功能、显示器数据通道总线从机功能、EDID信息预置及编辑功能、SCDC信息预置及编辑功能。测试方法连接如图4所示。

图4 发送端设备链路训练测试方法连接图

首先,根据目标模拟装置对目标设备进行链路训练,得到训练结果信息,包括接收端模拟装置启用电压检测功能,以得到电压检测结果;根据电压检测结果控制接收端模拟装置启用热插拔检测信号输出功能,以将热插拔检测信号设置为高电平;接收端模拟装置写入发送端设备SCDC数据的发送端测试配置寄存器;发送端设备根据写入的配置信息关闭前馈均衡器、链路训练的计时器;发送端设备读取接收端模拟装置的SCDC数据的状态标志位中的准备状态数据;若检测到固定速率链路训练准备状态数据等于1,则发送端设备将预设的训练数据写入接收端模拟装置的SCDC数据的接收端配置寄存器中;训练数据包括FRL功能的数据速率值、通道数量;发送端设备读取接收端模拟装置的SCDC数据中的训练测试码型请求数据;发送端设备根据训练测试码型请求数据发送测试模板数据给接收端模拟装置,若检测到测试模板发送成功,则生成训练结果信息。

其次,根据训练结果信息对目标设备进行目标测试。若训练结果信息为训练已完成,则接收端模拟装置控制高速示波器进行码型捕获与分析,以得到链路训练测试数据;高速示波器根据链路训练测试数据得到物理层信号完整性测试结果。

以上即为通过对发送端设备进行物理层信号完整性测试的应用来阐述基于HDMI2.1 FRL功能的链路训练和目标测试的过程。目标模拟装置在模拟为一个接收端模拟装置的设置下,配合高速示波器及其差分探棒,可以完成对发送端设备输出的FRL信号的物理层信号完整性测试。

在实际应用中,目标设备还可以是HDMI中继器设备。针对中继器产品兼具接收端与发送端功能的特性,需要根据训练结果信息对目标设备分别进行如上述实施例的针对接收端设备和针对发射端设备的测试,即分别进行物理层信号完整性测试和抖动容限测试。

通用的测试设备如任意波形发生器、高速示波器,广泛应用于通用的物理层信号的测试,然而这些测试设备本身是不具备任何与被测产品进行交互的通道。例如,当采用高速示波器对HDMI FRL发送端发送的信号进行信号质量分析时,就需要通过外部装置或设备诱导HDMI FRL发送端设备发出相应的测试码型,本文提出的目标模拟装置就是这种外部诱导装置的一种实现形式。

4 结语

本文提出的基于HDMI2.1 FRL链路训练的测试方法的目标模拟装置设计,是对现有测试方法的改进,并能够产生积极效果,该技术方案能有效提高设备的测试效率。随着技术的演变和新应用场景的出现,本文提供的技术方案对于类似的技术问题同样适用。期盼未来整体技术更加完整,以提升高清晰度多媒体影像产业的蓬勃发展[5]。