基于FPGA的便携式高速测试工装设计

任敏 魏骁 黄毅龙

摘 要:针对某型高速嵌入式信息安全设备的测试需求,设计一种基于FPGA的便携式高速测试工装。该测试工装包括上位机控制台和下位机测试平台两部分,上位机控制台采用软件形式实现,完成测试样本下发和测试数据储存,并提供人机交互界面;下位机测试平台采用FPGA作为核心处理单元,完成与上位机控制台及被测设备的接口转换和数据转发。测试结果表明:基于FPGA的便携式高速测试工装能够搭建稳定可靠的模拟测试环境,满足某型高速嵌入式信息安全设备的能力测试需求。

关键词:测试工装;FPGA;高速;便携式

中图分类号:TP206+.1 文献标识码:A 文章编号:2096-4706(2023)19-0037-05

Design of Portable High-speed Testing Fixture Based on FPGA

REN Min, WEI Xiao, HUANG Yilong

(National Computer System Engineering Research Institute of China, Beijing 100083, China)

Abstract: A portable high-speed testing fixture based on FPGA is designed to meet the testing requirements of a high-speed embedded information security device. The testing fixture includes two parts: the upper computer console and the lower computer testing platform. The upper computer console is implemented by software, which distributes testing samples, saves testing data, and provides the man-machine interaction interface. FPGA is used as the core processing unit in the lower computer testing platform, which completes interface conversion and data forwarding with the upper computer console and the tested device. Testing results show that the portable high-speed testing fixture based on FPGA can build a stable and reliable simulation testing environment to meet the capability testing requirements of the high-speed embedded information security device.

Keywords: testing fixture; FPGA; high-speed; portable

0 引 言

嵌入式信息安全设备主要应用于卫星通信领域的信息安全加密保护,通常采用独立的板卡或者模块形式实现[1],使用时通过专用接口嵌入通信宿主设备内部,随通信宿主设备一起开机启动,并由通信宿主设备提供电源和数据。嵌入式信息安全设备和通信宿主设备通常由不同厂家负责研制,通信宿主设备不能配合嵌入式信息安全设备开展全周期测试。测试工装作为一种常用的陪测设备[2],可以模拟通信宿主设备的硬件接口和软件功能[3],配合嵌入式信息安全设备搭建模拟测试环境,验证被测设备的各项能力指标。

测试工装通常包括上位机控制台和下位机测试平台两部分[4,5],传统的测试工装核心处理单元多采用CPU+FPGA架构实现[6,7],CPU连接上位机,实现下位机测试平台与上位机控制台的接口通信和指令解析功能,FPGA连接被测设备,实现下位机测试平台与被测设备的接口转换和数据转发功能,这种设计方案功能划分比较清晰,设计相对容易实现,但是在高速测试应用方面具有一定的局限性。比如:低性能CPU处理能力差、接口速率慢,不能满足被测设备的高速处理能力的测试需求,而高性能CPU一般體积大、功耗高,平台设计多为大型独立式设备[8],外出测试携带不方便,并且需要同时开发维护CPU和FPGA两个处理单元,人员成本相对较高。本文针对某型高速嵌入式信息安全设备的能力测试需求,同时考虑降低设计成本、提高设备便携性,提出一种基于FPGA的便携式高速测试工装设计。

1 方案设计

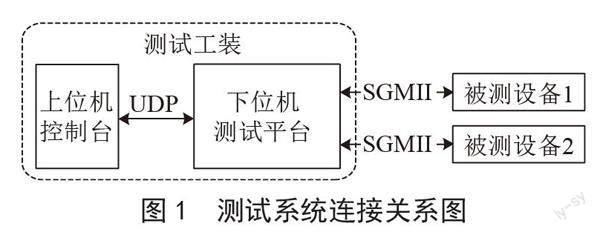

基于FPGA的便携式高速测试工装包括上位机控制台和下位机测试平台两部分,上位机控制台以软件形式实现,主要完成测试样本生成和指令下发、测试数据实时存储、测试结果统计和显示等功能,并提供人机交互界面,上位机控制台软件安装运行在通用测试计算机中。下位机测试平台用于模拟通信宿主设备,测试平台提供的物理接口与通信宿主设备完全一致,可以为嵌入式被测设备提供安装位置、供电电源以及数据通路。某型高速嵌入式信息安全设备的业务加解密处理速率不低于300 Mbit/s,对外数据通信采用高速SGMII接口实现,为了满足其测试应用需求,下位机测试平台对上采用UDP协议的千兆网口实现与上位机控制台的接口通信和数据交互,对下采用SGMII高速接口实现与被测设备的接口转换和数据转发。测试平台可以同时安装两块嵌入式信息安全设备,模拟两个通信终端之间的传输信息的加密和解密过程,整个测试系统连接关系如图1所示。

1.1 硬件设计

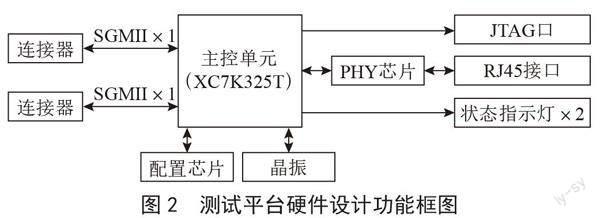

下位机测试平台的核心处理单元采用1片高性能FPGA实现,FPGA选用XILINX公司目前市场广泛应用的XC7K325T芯片,XC7K325T内部集成了丰富的逻辑单元和块RAM存储资源,并且具有8个GTX高速序列化接口,是一款性价比性相对较高的FPGA芯片,满足便携式高速测试工装的接口通信和数据处理需求。测试平台硬件功能原理如图2所示,FPGA对外输出2路独立的SGMII接口分别连接两块嵌入式被测设备,输出1路千兆网口连接上位机控制台,输出2路指示灯分别显示两块被测设备的运行状态。测试平台的SGMII接口在物理形态上与被测的某型高速嵌入式信息安全设备配对设计,采用航空插头连接器实现;千兆网口在物理形态上采用标准RJ45形式实现,标准网线可以直接接入连接。测试平台硬件设计遵循小型化原则,配套的结构机壳便携小巧,两块嵌入式被测设备通过测试平台上方的对应接口进行插接安装,操作过程方便容易。

1.2 软件设计

测试工装软件包括上位机控制台软件和下位机测试平台FPGA软件两部分。

1.2.1 上位机控制台软件

上位机控制台软件在Qt Creator 5.5环境下开发,该软件提供了大量的API和实用工具,界面形式友好,开发效率较高。上位机控制台主要实现测试需要的测试数据生成、控制指令下发、实时数据存储、数据收发统计、自检状态监控、重要日志上报等功能。通过上位机控制台软件可以便捷地的执行各项测试指令,同时直观地显示测试结果,便于测试人员统计分析,上位机控制台软件界面如图3所示,整个软件界面可划分为设备连接管理、日志显示、发送控制、接收数据显示、自检状态上报、帧计数统计等几个重要功能。

1)设备连接管理:主要用于管理和配置下位机控制台的网络通信参数,包括IP地址、端口号、设备标识、通信协议等,实现上位机控制台与下位机测试平台的千兆網络连接和数据通信。

2)日志显示:主要用于完成测试过程中重要信息的实时上报显示,辅助测试人员分析解决问题。

3)发送控制:主要用于管理和设置明文样本数据的发送指令参数,包括:测试帧类型、加密方设备和解密方设备、明密方式、发送帧的数量、发送速率控制、发送帧的长度等。

4)接收数据显示:主要用于读取显示本地存储的测试数据,包括加密后密文测试数据和解密后明文测试数据。

5)自检状态上报:主要用于显示被测设备的自检状态信息,监控被测设备的自身运行状态。

6)帧计数统计:主要用于统计显示本次测试的发送帧、接收帧和错误帧的具体数量,通过相关数据分析验证被测设备的加解密处理能力。

1.2.2 下位机测试平台FPGA软件设计

下位机测试平台FPGA软件在XILINX公司的Vivado 18.3环境下开发,编程采用Verilog语言,FPGA软件主要实现测试平台与上位机控制台之间、测试平台与被测设备之间的通信接口转换和测试数据转发功能。FPGA内部功能模块设计如图4所示,主要包括UDP接口控制模块、协议处理模块、通道切换控制模块、2路独立的SGMII接口控制模块、FIFO存储模块。

1)UDP接口控制模块:主要用于实现标准UDP通信协议的数据收发处理,完成下位机测试平台与上位机控制台的千兆网通信。

2)协议处理模块:主要用于实现下行测试数据的协议解析和上行测试数据的协议封装。

3)通道切换控制模块:主要用于控制下行测试数据分流输出至两路独立的SGMII接口,同时控制两路独立SGMII接口发送的上行数据分时输出至UDP通信接口。

4)SGMII接口控制模块:主要用于实现与被测设备的SGMII接口收发通信,两路SGMII接口功能独立,该模块通过调用FPGA内部IP核形式实现。

5)FIFO存储模块:主要用于实现模块之间的数据缓冲和速率匹配,该模块通过调用FPGA内部IP核形式实现。

1.3 工作流程

测试工装主要用于测试某型高速嵌入式信息安全设备的加解密处理能力,整个测试系统的工作流程如图5所示。

1)通过上位机控制台生成明文测试样本,设置明文测试样本帧的发送数量和发送速率。

2)上位机控制台按照设置的指令参数将明文测试样本下发至测试平台,并实时统计发送帧计数,测试平台将明文样本数据转发至加密方被测设备进行加密处理。

3)加密方被测设备将处理后的加密测试数据发送回测试平台,并通过测试平台转发至上位机控制台。

4)上位机控制台接收加密测试数据,并将加密测试数据按顺序写入本地文件,同时将加密测试数据下发至测试平台,通过测试平台将加密测试数据转发至解密方被测设备进行解密处理。

5)解密方被测设备将处理后的解密测试数据发送回测试平台,并通过测试平台转发至上位机控制台。

6)上位机控制台接收解密测试数据,实时统计接收帧计数,同时将接收的解密测试数据写入本地文件。

7)测试数据发送完成,通过上位机控制台读取本地存储解密测试数据,将解密测试数据与明文测试样本逐帧进行比对,实时统计错误帧计数,并将错误帧信息通过日志实时上报。

8)比对完成后,统计上位机控制台界面显示的发送帧计数、接收帧计数、错误帧计数、实时日志等信息,并对测试结果进行记录和分析。

2 测试验证

采用测试工装对某型高速嵌入式信息安全设备进行测试验证。按照图6所示连接关系搭建模拟测试环境,参试设备包括测试平台、测试计算机(运行上位机控制台软件)、两块嵌入式被测设备。

某型高速嵌入式信息安全设备的测试项目较多,这里以业务加解密性能测试为例,介绍模拟测试环境的测试流程和结果分析。

2.1 测试目的

验证被测设备在高速业务数据持续输入条件下加密和解密处理性能的可靠性。

2.2 测试步骤

1)测试计算机、测试平台上电启动,打开上位机控制台界面。

2)通过上位机控制台界面配置测试工装IP地址为192.168.1.211,端口号配置为3211,通信协议设置为UDP。

3)点击上位机控制台“发送复位指令”按钮,向两块嵌入式被测设备发送复位指令,观察上位机界面被测设备上报的自检状态;如果显示“通过”表示被测设备状态正常,进入下一步操作。否则被测设备状态异常,需排查故障。

4)在上位机控制台的发送控制区选择“业务帧”,选择加密方为被测设备1,解密方为被测设备2,设置发送帧数量为100 000帧,设置发送速率为300 Mbit/s,设置帧长度为1 024 Byte,明密设置为加密。点击选择发送样本栏的“浏览”按钮,在本地文件中选择相应的明文测试样本,然后点击“发送帧”按钮,观察日志栏上报的打印信息,直至显示“数据帧发送完成”,记录统计区“发送帧计数”“接收帧计数”的显示数据。

5)点击上位机控制台“明文比对指令”按钮,观察日志栏上报的打印信息,直至显示“数据帧比对完成”,记录“错误帧计数”显示数据。

6)保持发送控制区的指令参数不变,按照步骤4)、步骤5)重复操作2次。

7)在上位机控制台的发送控制区选择加密方为被测设备2,选择解密方为被测设备1,其他指令参数不变,按照步骤4)、步骤5)重复操作3次。

8)记录测试结果信息,整理并保存明文和密文测试数据,测试平台断电。

2.3 测试结果及数据分析

表1中测试数据统计显示6次测试的发送帧计数与接收帧计数全部一致,均为100 000帧,错误帧计数均为0帧,测试过程没有出现丢帧和错帧现象,两块被测设备的业务加解密处理性能稳定可靠,测试达到了预期目标,同时证明了测试工装的可行性和测试能力。

3 结 论

本文提出了一种基于FPGA的便攜式高速测试工装设计,测试工装包括上位机控制台软件和下位机测试平台两部分,上位机控制台软件完成测试样本下发和测试数据储存,并提供人机交互界面;下位机测试平台以FPGA为核心处理单元,用以完成与上位机控制台及被测设备的接口转换和数据转发。通过测试验证发现:基于FPGA的便携式高速测试工装能够搭建稳定可靠的模拟测试环境,满足某型高速嵌入式信息安全设备的测试应用需求,测试工装开发维护成本低,携带方便,具有很高的实用性。

参考文献:

[1] 吴召平,侯云江,苏航.基于嵌入式平台的某型模块测试工装设计 [J].信息技术与信息化,2021(8):113-115.

[2] 李强,黎小军,吴召平.基于嵌入式平台的某型网络设备测试工装的研究与设计 [J].电子世界,2022(2):144-146.

[3] 唐良伟.多通道综合化控制台通用测试工装的设计与实现 [J].电子质量,2020(3):14-17+23.

[4] 张德智,曾星星,刘建妥,等.基于VPX架构的测控通信综合测试系统设计 [J].计算机测量与控制,2016,24(5):53-54+70.

[5] 胡荣芳.一种通用自动化测试设备的设计与实现 [J].流体测量与控制,2023,4(2):20-24.

[6] 刘宗瑞.高速嵌入式检测技术研究 [D].北京:北京理工大学,2018.

[7] 韩林涛.卫星数据通信地面检测设备的设计与实现 [D].西安:西北大学,2022.

[8] 秦友伦,袁强,刘峰,等.一种全国产化多接口便携式测试设备 [J].兵工自动化,2023,42(2):42-45.

作者简介:任敏(1989—),男,汉族,山西大同人,工程师,硕士研究生,主要研究方向:电子通信、信息安全等。

收稿日期:2023-05-06