兼容音频播放的多通道有源噪声控制系统设计

张芳杰,王一凡,桑晋秋,郑成诗,李晓东

(1.中国科学院声学研究所,北京 100190;2.中国科学院噪声与振动重点实验室,北京 100190;3.中国科学院大学,北京 100049)

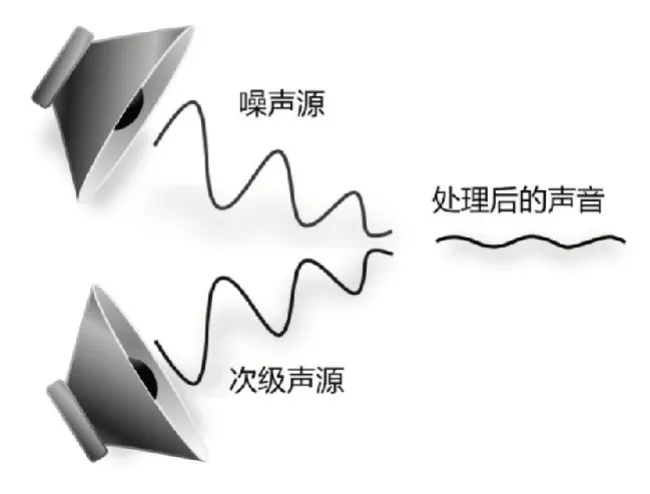

随着科技和社会的不断发展,噪声污染和治理受到越来越多的重视。传统噪声控制方法主要采用隔声、吸声等无源方式,该方式对中高频降噪效果明显,但针对低频噪声要求材料的体积和质量大,在多数场景中往往难以实现。有源噪声控制技术利用控制系统产生反向声波来抵消目标位置的噪声,从而实现消除噪声的目的[1-7]。

文中旨在设计出一套能够满足多通道局部有源噪声控制技术需求的系统。该系统具有支持通道数多、系统延时低、实时处理能力强等特点,并且兼容音频播放、回声抵消功能。

1 系统整体设计

有源噪声控制技术原理图如图1 所示。

图1 有源噪声控制原理

作为有源噪声控制中的一类,局部有源噪声控制的研究和应用是近期热点[8-11]。同时,如何实现音频播放与有源噪声控制功能的并发,并消除音频播放对有源噪声控制过程的干扰,具有较大的市场需求。然而,有别于耳机等有源噪声控制场景,局部有源噪声控制技术的高性能实现对系统平台的要求极高,研制相应的实时信号采集、处理系统是顺利开展相关工作的重要一环。

局部有源噪声控制系统目标区域的噪声源来波方向复杂、时变性高,在局部空间有源噪声控制的应用中,往往需要由多个传声器捡拾参考信号和误差信号作为输入,并且需要生成多路控制信号馈给扬声器,以更好地消除噪声和扩大静音区范围。当输入和输出通道数增多时,系统的数据采集和播放模块变得复杂。同时,通道数的增加导致计算复杂度急剧上升,如采用时域自适应控制算法,为了实现实时控制,系统的计算性能要求极高。

随着各类音频通信协议的不断发展,音频通信接口不断增加,常见的音频来源包括Micro SD 卡、网络数据流、蓝牙通信接口、音频模拟信号线等。为了在高性能有源噪声控制平台的基础上实现音频播放并且支持回声抵消功能,文中采用易扩展、可升级的独立音频播放管理模块。在设计多通道、高性能有源噪声控制系统时预留出排针,并以子板形式设计与接口匹配的相应音频及其他对外接口管理模块。文中系统整体设计框图如图2 所示。

图2 系统整体设计框图

除了电源、时钟等配套模块外,系统包括三个部分:①以XC7K325T 型号FPGA 为核心处理器的信号采集、输出及逻辑管理模块[12-14];②以TMS320C6678型号DSP 为核心的信号处理模块;③以XC7Z020 型号ZYNQ 为核心处理器的音频、视频及其他对外接口管理模块。

TMS320C6678是TI公司开发的高性能八核C66x定点和浮点DSP,可以支持高达1.4 GHz主频[15-16]。单核的定点数据处理能力为44.8 GMAC,浮点数据处理能力为22.4 GFLOP,能够满足多通道实时计算的需求。

XC7Z020 是Xilinx 公司开发的一款小型SOC,内置了双核Cortex-A9 内核的ARM 处理器和较低资源的FPGA,适合进行音频以及其他对外数字接口的逻辑管理[17-19]。

ARM 具有外围标准接口丰富、驱动资源充足并且可搭载Linux 操作系统进行各类规范处理的优点,但是对非标准接口兼容性较差且计算能力受限。FPGA 具有极高的并行计算能力,接口丰富,方便实现各类非标准接口和数据流管理,但是复杂算法的开发难度大且程序综合时间长。DSP 以特定的架构实现流水线计算,能够以较低主频实现高速计算,相对于FPGA 算法开发周期短,但是其接口资源较少,较难实现各类非标准通信。

文中结合三类处理器的优势,利用FPGA 实现传声器信号的实时采集、控制信号的实时输出和数据预处理,并且实现该模块与ZYNQ 和DSP 之间的高速通信;接着利用DSP 的EMIF16 接口逐点接收FPGA 的各类数据,之后实现有源噪声控制算法的计算,并将控制系统回传至FPGA;最后利用ZYNQ 实现SD 卡中音频数据的读取、用户控制命令的获取,并通过特定协议将数据传输至FPGA。

2 系统硬件设计

2.1 信号采集、输出及逻辑管理模块

该模块最主要的功能包括两方面:一方面,通过控制ADC 芯片实现传声器信号采集,并根据EMIF16接口协议上传采集数据;另一方面,根据EMIF16 接口协议接收控制信号,并由DAC 芯片转换成模拟信号输出。

在实现数据采集过程中,硬件电路设计示意图如图3 所示。

图3 数据采集过程示意图

在调理电路的干净直流偏置下,传声器产生的微弱交流信号叠加在直流信号上,输出到模拟信号处理电路。模拟信号处理电路包括隔直电路、一级交流增益电路、带通滤波电路、二级交流增益电路以及低通滤波电路。隔直电流的功能是隔离输入的直流成分,保证后级的信号增益过程中信号不会出现饱和问题;两级交流增益电路的设计是为了在中间插入带通滤波器,进而降低模拟信号中的噪声分量;最后一级低通滤波电路为抗混叠滤波电路,用于滤除ADC 电路的带外信号。模拟信号经过ADC 电路后产生数字信号,在FPGA 的逻辑控制下,数字信号快速发送到FPGA 内部相应的寄存器。

脑科学,正成为生命科学中最活跃的一个分支,21世纪的脑科学最终将解开大脑的终极秘密,并攻克若干大脑疾病,让我们拥有更健康的大脑。

该系统中,使用的ADC 器件为ADI 公司生产的AD7606B 型号芯片,该芯片为8 通道DAS、内置16位、800 kSPS 双极性输入的同步采样ADC,输入的双极差分范围支持±10 V、±5 V 和±2.5 V 三档,满足多通道、高速采样和高精度转换的要求。

在实现控制信号输出的过程中,硬件部分示意图如图4 所示。

图4 控制信号输出过程示意图

FPGA 在接收到DSP 发送的数字控制信号后,首先通过控制DAC 芯片产生对应的模拟信号。模拟信号经过模拟信号处理电路和功放电路输出到扬声器。模拟信号处理电路包含了重构滤波电路、增益匹配电路、带通滤波电路以及阻抗匹配电路。重构滤波电路用以消除DAC 转换过程产生的高频噪声,增益匹配电路用以实现DAC 输出模拟信号范围与功放输入信号范围之间的匹配带通,滤波电路用以降低非关注频段的信号,阻抗匹配电路用以确保输入到功放电路的信号与模拟信号处理电路的开环输出信号一致。功放电路将输入的信号放大后输出到扬声器,即实现控制声信号的播放。

该系统中使用的DAC 器件为ADI 公司生产的LTC2755-16 芯片,该芯片是具有并行I/O 的四通道电流输出型16 位SoftSpan DAC。在双极输出模式下支持±5 V、±10 V、±2.5 V 以及-2.5~7.5 V 四种设置,且具有2 μs 稳定时间及±1 LSB 的优异性能,能够满足系统对高速转换、低噪声和多通道的需求。

2.2 音频及其他对外接口管理模块

该模块的功能是实现SD 卡中音频文件的读取、网络接口视频信号的接收、远程服务器控制信号的传递等功能。模块硬件框图如图5 所示。

图5 模块硬件框图

音乐信号存储在SD 卡中,视频信号通过RJ45接口并经过PHY 芯片后传输到ZYNQ 芯片中,外部控制命令可通过Mini USB 口传递到模块内。ZYNQ芯片内部包含PS 端和PL 端两部分,PS 部分由ARM处理器主导,负责SD 卡管理、网络接口通信、串口命令处理等功能;PL 部分主要为小型FPGA,可通过并行总线与主FPGA 芯片XC7K325T 之间进行数据交互。ZYNQ 芯片内部的PS 部分与PL 部分通过axi4总线互联。axi4 总线是ARM 公司开发的AMBA 总线中的一部分,包括axi4-lite、axi4-full 和axi4-stream三种类型,能够实现两部分不同数据类型的高速通信。

2.3 核心信号处理模块

核心信号处理模块由TMS320C6678 处理器主导,在该系统中除最小系统外,完成的主要功能为通过EMIF16 接口收发数据以及实现高速计算。

为了实现大量数据的缓存,该模块中配置了四片MT41J128M16HA 缓存芯片以支持1 GB 缓存。同时,利用NAND512R3A2DZA6 型号的Flash 实现程序和数据的存储。

TMS320C6678 芯片对各路电源和时钟的上电顺序有严格要求,系统支持I/O 先上电和内核先上电两种模式。该系统采用内核先上电模式(Core-before-IO),所有相关的电源芯片、时钟芯片的使能信号和PowerGood 信号均由XC7K325T 芯片进行控制。

3 系统软件设计

3.1 多通道有源噪声控制

在不需要音频播放的工作场景中,为了实现有源噪声控制功能,文中采用FPGA+DSP 的整体方案设计。所设计的系统数据流示意图如图6 所示。在FPGA 的硬线逻辑的管理下,ADC 芯片根据采样时钟进行数据采集,并将数据通过16 位并行总线传输到FPGA。FPGA 接收到采样数据后,首先对信号进行必要的预处理,而后通过EMIF16 接口将输出传输到DSP 芯片内。当DSP 接收到采样数据后,通过有源噪声控制算法计算出每个输出通道相应的控制信号,并通过EMIF16 接口反馈给FPGA。FPGA 在接收到输出控制信号后,控制DAC 芯片产生多通道模拟输出信号,最终实现有源噪声控制功能。

图6 有源噪声控制系统数据流图

以读取采样数据过程为例介绍EMIF16 接口:DSP 端利用EMIF16 异步读取FPGA 数据的时序如图7 所示,除了EMIFD[15:0]之外,其他信号全部由DSP 驱动。EMIFCE[3:0]表示DSP 的片选信号,低电平有效,文中FPGA 使用的片选地址为EMIFCE2;EMIFR/W 表示读写操作,高电平表示DSP 读操作;EMIFOE 表示是否支持扩展等待模式,取0 表示关闭;EMIFBE 表示字节使能信号;EMIFA[21:0]总线表示DSP 对FPGA 的读或写地址。FPGA 在图中EMIFD为白色的时间段驱动数据总线,并将相关地址的信号发送给DSP。

图7 EMIF16异步存储器读取时序

3.2 音频播放及回声抵消功能

ZYNQ 芯片包含ARM,其是系统与外部交互的第一个环节,也是FPGA 与DSP 芯片获取用户控制命令、音频数据的来源。ZYNQ 与FPGA 之间的音频数据交互流程如图8 所示。ZYNQ 与FPGA 芯片之间启动音频播放的命令通过一根专用I/O 线实现。

图8 ZYNQ与FPGA音频数据交互

当ZYNQ 检测到外部音频播放命令后,进行首次DMA 设置,用以读取SD 卡中的音频文件并放置到RAM 中。当DMA 读取完成后,CPU 将收到对应中断信号,并在中断函数中设置标志位。CPU 检测到标志位且发现当前仍处于启动音频播放模式下,则立即发起下一次DMA 文件读取,否则停止读取音频文件。在DMA进行文件读取时,CPU不需要参与相关工作,可将RAM 中的数据实时发送给FPGA。

在实际应用中,根据音频来源的不同,音频数据的读取方式可以多种多样,下面对播放SD 卡中音频文件的方式进行说明,其他方式的差异仅是数据到音频管理模块中RAM 的方式不同。在添加音乐播放功能并实现回声抵消算法的多通道有源噪声控制系统数据流示意图如图9 所示。

图9 增加音频播放的数据流示意图

3.3 系统工作模式管理

系统上电后,ZYNQ 会执行上电初始化操作,经过初始化后,ZYNQ 内部PS 部分相关的MIO 接口、串口或者网口处于打开状态,用于用户设定工作模式。CPU 每500 ms 查询一次当前工作模式,同时对FPGA 和DSP 进行模式同步。

系统工作模式包括休眠模式、仅有源噪声控制模式、仅音频播放模式以及有源噪声控制模式叠加音频播放模式。每个模块根据同步后的模式确定是否开启音频播放和回声抵消功能,以及是否启动有源噪声控制功能。系统工作模式管理如图10 所示。

图10 系统工作模式管理

4 系统功能测试

为了验证所设计系统的可行性,文中搭建了图11 所示的实验系统,并采用经典多通道有源噪声控制算法和回声抵消算法来验证所设计系统的可行性。

图11 多通道局部有源噪声控制示意图

实验系统中采用四个传声器拾取参考信号,采用两个传声器作为误差传声器,设置了两个扬声器作为用于播放次级声源的扬声器。设置了四个初级声源,噪声类型为粉红噪声。实验过程中采用的有源噪声控制算法为FxNLMS 算法,有源噪声控制的次级路径传递函数以及回声抵消利用的传递函数均采用离线辨识获得。通过实验,在100 Hz 到500 Hz的目标降噪频带内,在头部半径20 cm 内获得了大于8 dB 的平均降噪效果。测试结果表明,音频播放正常,且音频播放过程对有源降噪效果几乎没有负面影响。

5 结论

文中设计了一种兼容音频播放功能的多通道局部有源噪声控制系统。利用FPGA、DSP 和ARM 处理器各自的特点,实现了系统不同功能的分解,满足了整个系统的各项任务需求。通过合理的硬件和软件设计与实现,该系统能够实现在进行多通道有源噪声自适应控制的同时,实现音频播放以及回声抵消功能。在经过全系统的研制后,文中搭建了相应的测试环境,进行了系统功能测试,测试结果验证了所设计系统的实际性能。