基于eFPGA 的可重构片上系统研究

康礼煜,贾一平,高丽江,杨海钢,,4

(1.中国科学院空天信息创新研究院,北京 100190;2.中国科学院大学,北京 100049;3.北京中科胜芯科技有限公司,北京 100044;4.山东产研集成电路产业研究院,山东济南 250001)

随着集成电路的设计复杂度以及设计要求大幅增长,为了提升片上系统(System-on-Chip,SOC)的灵活性以应对各类计算任务,可重构片上系统这一概念被提出。其中基于嵌入式现场可编程门阵列(embedded Field Programmable Gate Array,eFPGA)的可重构系统被广泛应用于人工智能、自动驾驶、物联网终端以及航空航天等相关领域[1-4]。

目前,基于eFPGA的可重构系统主要是将eFPGA挂载在总线上作为协处理器,以提升系统性能;或者将eFPGA 模块与处理器内部结构耦合,以支持自定义指令集的扩展[5-7]。该文所讨论的是如何在原有架构基础上,通过架构调整以及使用码流压缩传输的方法优化系统性能。

1 可重构系统硬件架构

1.1 系统架构设计

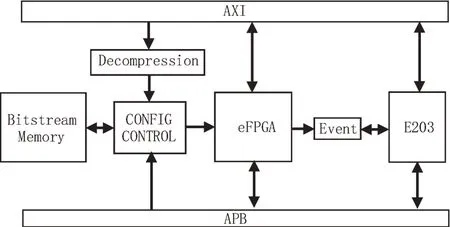

该文提出的可重构系统由开源的RISCV 处理器E203[8]与eFPGA 子系统组成。eFPGA 子系统由利用开源平台OpenFPGA[9]设计生成的eFPGA 模块及相关的重构逻辑电路和交互逻辑电路组成。电路架构如图1 所示。

图1 电路架构图

整个系统的工作模式可以分为重构模式和交互模式。在重构模式中,由于APB 总线的传输速率比AXI 总线慢[10],且码流数据量较大,为了加快码流写入速度,故选择AXI 总线用于码流传输;而由于APB总线传输数据的功耗比AXI 总线低[10],且一般应用场景不需要太快的数据交互速度,所以在数据交互时选择使用APB 总线。

在配码过程中还面临着另一问题,即如果码流数据是处理器通过AXI 总线直接配置到eFPGA 中,由于AXI 总线传输数据需要握手等相关步骤,这会使重构时间加长,所以在该系统中添加了码流存储器,使配码阶段可进行连续配码;同时为了使整个系统更加灵活,将码流存储器的存储空间设计为三个常用电路大小,使重构更加便捷。

若需要重构存储器中不包含的电路,则需要更新存储器中的码流,由于码流数据庞大,所以在处理器通过总线频繁写入的过程中就会产生较大的能耗。为了解决这一问题,提出了码流压缩传输的方法,即在码流传输前先将其压缩,传输后在电路中先通过解压缩(Decompression)模块对其进行解压再写入存储器中,由于传输码流数据需要经历较长的数据传输链路,所以完整的码流传输过程中消耗的能耗相较于该文所提出的增加解压缩模块所增长的能耗要大得多,相关的实验数据在后文中展示。

在eFPGA、总线与码流存储器之间,还有一个至关重要的配置控制(CONFIG-CONTROL)模块。该模块主要分为控制和配置两部分,配置部分主要用于在配码阶段将码流从存储器中读出并写入eFPGA的配置端口;而控制部分主要分为三个功能模块:

1)控制eFPGA 进行反复重构的控制模块。

2)解译配置寄存器参数的译码模块。

3)由于每次解压的码流数量不一致,所以还需要设计码流的写控制模块。

码流映射成功之后,处理器通过APB 总线与eFPGA 模块进行交互,同时在AXI 总线地址上预留好相关寄存器地址,以便在APB 总线传输速率不符合需求时,可以通过AXI 总线进行数据传输。此外,eFPGA 还引出了四个中断交互端口,以便应用电路可以触发中断以避免轮询造成的空转消耗。

1.2 eFPGA模块设计

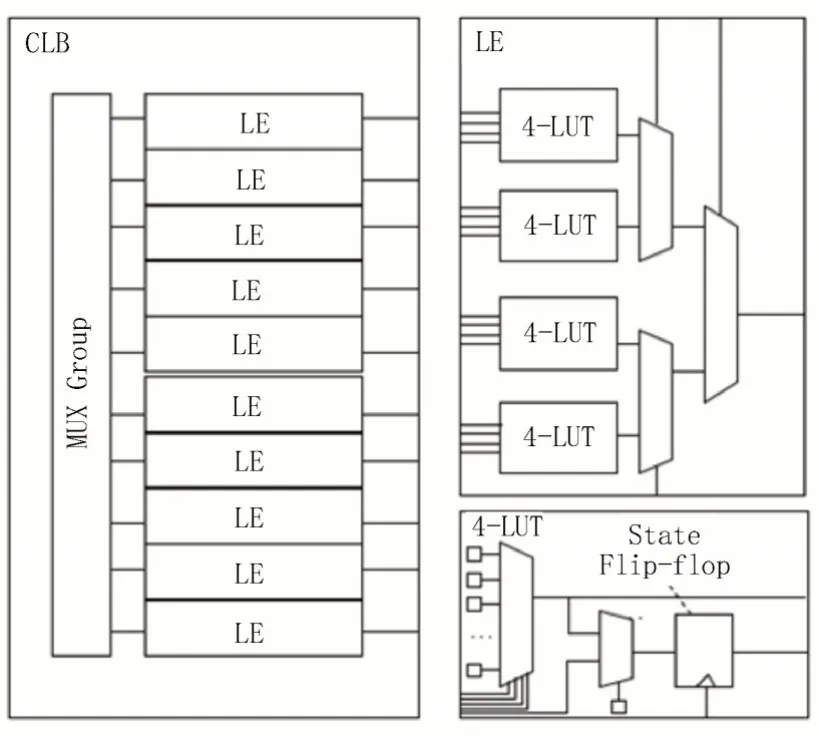

eFPGA 指可以作为IP 嵌入到片上系统的现场可编程门阵列核[7],其既具有FPGA 的可编程特性,又规避了FPGA 的功耗高与面积大等缺点,所以将其嵌入SOC 中可以将ASIC(Application Specific Integrated Circuit)的高性能与FPGA 的可编程特性结合起来,使整个系统更加灵活可靠[1]。该文所设计的eFPGA模块是基于OpenFPGA 的K6N10 结构[11]设计产生的由重复逻辑块构成的岛型阵列,架构如图2 所示。

图2 eFPGA模块架构图

重复逻辑块是由可编程逻辑块(Configurable-Logic-Blocks,CLB)、连接盒(Connection-Box,CB)、开关盒(Switch-Box,SB)以及互连线(Interconnect)构成。其中,每个CLB 模块由十个逻辑单元(Logic-Element,LE)及相关配置电路构成,用以实现可编程功能;CB 和SB 模块都是由多路开关(Multiplexer,MUX)和配置存储器(CRAM)构成,以连接模块之间的布线通道,具体电路如图3、图4 所示。其中,CB模块用于CLB 和通道之间的连接,SB 模块用于不同通道之间的连接;最终构成一个20×20 阵列规模的eFPGA 模块,其可以映射4 000 LE 规模以下的电路。

图3 CLB模块电路图

图4 CB、SB模块电路图

文中的eFPGA 模块是利用开源的OpenFPGA 平台通过设计相关的架构描述文件以及Versatile-Place-and-Route(VPR)描述文件生成相应的软核[11],同时也可以利用该平台生成相应eFPGA 模块的码流。码流的产生过程如图5 所示,主要步骤是先设计好应用电路的HDL 代码,仿真验证通过后利用Yosys 对其进行综合,再将其输入到VPR 进行装箱、布局和布线,最后利用OpenFPGA 平台产生相应的码流[9]。

图5 OpenFPGA流程图

1.3 码流压缩算法及解压缩电路设计

eFPGA 配码过程中传输的码流数据的每一比特位都有其独特含义,所以使用的压缩算法必须是无损算法。在1977 年由Abraham 和Jacob 所提出的LZ77 算法具有压缩率较好和复杂度适中的优点,同时是基于字典编码的无损压缩算法[12],所以该算法的解压缩过程适合用电路实现,故在该文中选择了LZ77 算法作为码流压缩算法。

该算法的主要原理是利用滑窗进行相关的字符匹配,利用指针来表示压缩的字符串。滑窗组成如图6 所示,滑窗由字典窗口和编码缓冲区组成,字典窗口用于保存等待匹配的序列,编码缓冲区则保存等待编码的序列[12];指针由偏移量和匹配长度组成,偏移量是当前序列到字典窗口中匹配序列的距离,匹配长度则是重复序列的个数[12-14]。

图6 压缩和解压缩过程

压缩步骤是先读取编码缓冲区的序列并在字典窗口中查找能匹配到的最长序列,并输出指针。如图6所示,字典窗口中能找到编码缓冲区最长的重复序列为1011,且偏移量为5,故输出的指针为(5,4)。

解压缩是压缩的逆过程。如图6 所示,左侧滑窗中的数字是10110,且此时指针中偏移量为4,匹配长度为3,由此可得解压出的数据是011,填入数据并移动滑窗至末尾,解压完成。

在电路实现过程中,由于滑窗与电路中的移位寄存器有共通之处,故选择移位寄存器来实现滑窗功能,并使用数据选择器阵列来解压指针内容,以控制移位寄存器中的移位操作和输出相应的解压数据,解压电路如图7 所示。

图7 解压电路

2 软硬件协同设计

软硬件协同设计是实现可重构系统中必不可少的一步,因为eFPGA的多次重构以及处理器与eFPGA的数据交互是通过软件控制实现的。其主要的应用场景如下:

1)通过软件控制进行多次配码,以实现在有限的eFPGA 资源上实现更大规模的电路或者实现多种不同的电路功能。

2)面对复杂任务时,将适合软件实现的分配给处理器实现,适合硬件实现的分配给eFPGA 实现,最后结合起来,以实现软硬协同加速。

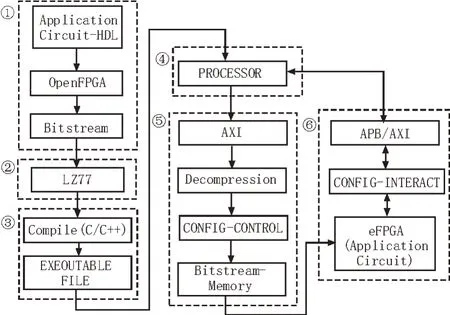

整个系统的工作流程如图8 所示。

图8 工作流程

其主要步骤如下:

1)设计电路并在OpenFPGA 生成码流。

2)利用LZ77 算法压缩码流。

3)将压缩后的码流以及配置交互信息按需写到软件设计中,并通过工具链编译生成可执行文件。

4)将可执行文件翻译成指令流写入处理器中并执行相关指令。

5)处理器通过AXI 总线将压缩码流写入到解压缩模块进行解压,并通过配置控制模块写入相应的存储空间。

6)通过软件写入相关配置信息,读出相应码流,并将其写入eFPGA 中以实现该电路,最后通过APB/AXI 总线与之交互。

3 软硬件协同实验

软件设计环境是NucleiStudio IDE 2021.02,硬件设计及仿真环境是VCS2017.12 和VERDI2016.06。该实验实现了密钥大小为128 bit 的AES 算法中的Electronic-Codebook-Book(ECB)加密模式。该模式将明文分割成多个数据块,各个数据块分别进行加密生成各自的密文块,最终拼接成完整的密文[15-16]。

主要加密步骤是字节代换、行移位、列混合和轮密钥加四个部分进行迭代操作。在使用eFPGA 实现该算法时,整个加密过程只使用了21 个周期,且每次重构只需1 630 个周期。

在软件实现AES的过程中,利用函数__get_rv_cycle()获取E203 处理器实现该算法的周期数,如图9 所示,打印出E203实现该算法用了68 873个周期,且加密结果与eFPGA 实现一致,eFPGA 比E203 实现AES 的速度提高了3 279 倍;而利用ZYNQ7020 上的Cortex-A9处理器实现该算法用了47 188 个周期,eFPGA 比Cortex-A9 提高了2 247倍,可见该算法在eFPGA中实现的加速效果显著。

4 综合及结果分析

该系统在TSMC 28 nm 工艺条件下,通过Design Compiler 对电路采用Bottom-up 的策略进行综合;在200 MHz 的频率下,时序依旧满足要求。

在200 MHz 的频率下,对E203 SOC 添加解压模块前与添加后这两种情况使用Primetime-PX(PTPX)对码流传输过程进行功耗分析,结果表明,两种情况的平均功耗分别为P1=47.9 mW 和P2=48.7 mW。

假设直接传输码流的时间为T1,能耗为E1;添加解压模块之后码流传输的时间为T2,能耗为E2;由于码流传输过程是匀速的,所以码流的压缩比ε=T2/T1。由能耗公式E=PT可得,当压缩比为98.36%时,E1=E2,此时码流传输所消耗的能耗相等,所以当重构电路的压缩比小于98.36%时,该系统相较于之前的架构所消耗的能耗更少。以AES电路为例,由于其压缩比约为68.20%,所以能耗与原先架构的相比降低了:

图10 展示了应用电路规模从1~3 953 LE 的55个不同规模电路的码流压缩比,由图可得,压缩比与规模总体上成正相关,且当规模小于3 900 LE 时,压缩比小于98.36%,故使用码流压缩传输的方法可以使eFPGA 重构的大多数电路在码流传输过程中节约部分能耗,且由该图数据可得该系统在配置过程中压缩比最小约为17.9%,所以该方法最多可在配码阶段节省约82.1%的能耗。

图10 电路规模与码流压缩比散点图

5 结论

该文讨论了一种基于eFPGA 的可重构系统设计。通过设计配置控制电路和码流解压缩电路等,使得系统变得更加灵活、节能及可靠。仿真结果表明,该系统不仅可以通过软件控制eFPGA 进行反复编程;还支持软硬协同加速器的应用开发。同时在采用TSMC 28 nm 工艺条件下对该系统进行综合,结果表明,该系统最高在200 MHz 的频率下依旧满足时序要求;利用PTPX 对其进行功耗分析时发现当重构电路码流压缩比小于98.36%时,相比于传统架构,该架构可以起到节省能耗的作用。