基于CNN 的多核芯片低功耗验证系统设计

王 宇,祝健杨,何雨旻,刘德宏,陈军健

(1.贵州电网有限责任公司电力科学研究院,贵州贵阳 550002;2.南方电网数字电网研究院有限公司,广东 广州 510663)

在电网数字化转型过程中,海量电力数据访问验证技术存在芯片功耗大,易发生数据过载且验证过程损失大的问题。传统的多核芯片低功耗验证系统主要包括基于UPF 的低功耗验证系统和基于MDP的低功耗验证系统。基于UPF 的低功耗验证系统在验证复杂芯片时,需要大量断言检查,验证效率低[1-2]。基于MDP 的低功耗验证系统对中断位置需要进行重复分析与验证,耗时较长[3]。

为了更好地验证多核芯片的低功耗性能,该文提出了一种基于CNN 的多核芯片低功耗验证系统,分别从硬件和软件方面对系统进行了设计。

1 系统硬件设计

1.1 ARM720T处理器设计

纳米级芯片的出现,使得芯片的频率和密度大大增加,多核芯片是普通芯片的升级,通过任务划分成功实现横向扩展,功耗是制约多核芯片的重要因素,主要来自漏电消耗和动态消耗,低功耗、高精度、迷你外型是目前人们对芯片的追求,由于多核芯片低功耗设计的要求逐渐提高,因此人们对低功耗验证系统也有了更高的要求[4]。

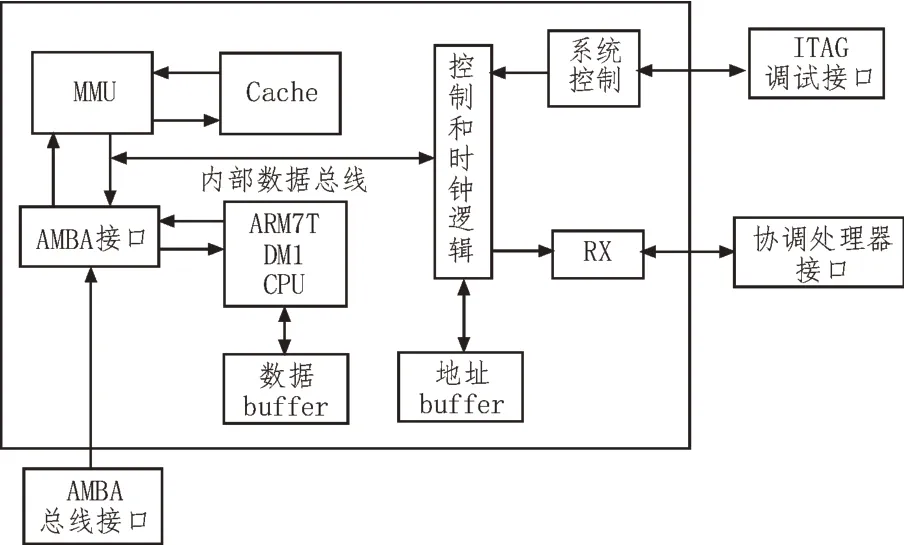

处理器的作用是执行处理指令,保证系统工作的快速性和正确性[5-6]。处理器采用ARM720T,它是一种采用集成式32 位的微处理器。ARM720T 微处理器结构如图1 所示。

图1 ARM720T微处理器结构

根据图1 可知,ARM720T 微处理器外部连接3 个接口,分别是AMBA 总线接口、ITAG 调试接口和协调处理器接口,采用数据buffer 和地址buffer 连接,并实时配合控制和时钟逻辑[7]。

1.2 写缓冲器

写缓冲器的作用主要是存放微处理器即将写入存储器的所有数据。写缓冲器大大改善了Cache 的计算性能,当处理器有数据要替换时,可以直接在写缓冲器上进行改进,而无需设计存储器。该文研究的写缓冲器电路图如图2 所示。

观察图2可知,写缓冲器电路内部有4个电阻,两个电容。在该系统中,写缓冲器先把要写的数据高速写入缓冲器,再由写缓冲器低速写入数据存储器中,写缓冲器在高速的微处理器和低速的数据存储器之间起到了数据缓冲的作用[9-10]。

1.3 程序存储器

存储模块用于存放系统程序和各类数据,由存储器和接口构成。存储器采用SST89E516RD 单片机,SST89E516RD 单片机工作原理图如图3 所示。

图3 SST89E516RD单片机工作原理图

根据图3 可知,该文研究的单片机通过3 个电阻实现电路接地。单片机的存储大小为128 Mbit,存储空间由若干个互相独立的128 kbyte 擦除块组成,擦除操作能擦除芯片中预先编辑好的域代码,存储器地址块的空间为0x0000 3000 到0x0000 3FFF,通过单片机将程序存储空间扩充至64K。此外,该系列产品充分利用了超级Flash 创新技术,存储块black 0占用64/32K 存储空间,存储块black 1 占用8K 存储空间[11-12]。

1.4 SDRAM中断控制器

中断控制器的作用是调度系统任务,必要时中断系统请求。控制模块的主要部件是EP7312 中断控制器,包括SDRAM 中断控制器和外部存储接口控制器。SDRAM 中断控制器结构如图4 所示。

图4 SDRAM中断控制器结构

观察图4 可知,SDRAM 控制器能支持两组外部SDRAM,当CPU就绪时其自动启动自动更新。SDRAM控制器内部容量为16 Mbyte,寻址空间为256 byte。根据A0-A11 和BA0/BA1 信号,找到SDRAM 的具体地址,再依据控制信号进行操作。外部存储接口控制器的特点:有6 个可选的编程信号、可编程等待状态为0~8、可编程的总线宽度为8~32 位,EP7312 直接与一个LCD 面板相连,面板的大小可调节,中断控制器能同时控制两个FIQ 及两个IRQ 中断源产生的中断[13]。

2 系统软件设计

2.1 集中度验证

在进行多核芯片的低功耗验证时,首先需要整体衡量多核芯片的低功耗程度。交并比可以用于度量相似性,是判断多核芯片低功耗的关键指标,但是,原始交并比有一定的缺点,验证中一些重要的参数可能被视为冗余而被错误筛选掉。该文在交并比的基础上作出了改进,利用“集中度”来衡量多核芯片的低功耗程度,“集中度”指的是验证的中心与低功耗真值的标准距离,更靠近真值的多核芯片,被认为具有更低的功耗[14]。

2.2 低功耗特征重现

针对不同的多核芯片,低功耗验证对所有芯片的操作无差别,但是,由于多核芯片的类型不同,低功耗验证时不可避免会损失一些性能特点。为了解决这个问题,该文设计了一种基于CNN 的低功耗特征重现模块。该模块能够根据多核芯片的整体性能和几何结构特点对低功耗特征进行重新分配,弥补验证过程中的低功耗特征损失。低功耗特征重现原理如图5 所示。

图5 低功耗特征重现原理

如图5 所示,基于CNN 的低功耗特征重现模块的本质是数据的输入与输出,模型不需要精确的数据表达式就能学习输入与输出之间的映射关系。基于CNN 的低功耗特征重现模块以多核芯片的整体性能为输入,以低功耗特征为输出,重现模块由捕捉长短距离的两种内核组成,对于每个多核芯片的整体特征,利用CNN 输入特征图的通道数目,针对依赖长距离的特征,使用条带化操作捕捉窄特征,根据特征分布紧密的情况,通过金字塔模型获取多核芯片的前后信息。

2.3 验证系统建立

为了有效降低整个金字塔的相邻特征层在合并时出现的问题,在每个相邻特征之间分别插入FPN层,形成RPN 网格结构。PRN 上集合了多核芯片的整体特征,通过低功耗特征重现得到几何编码特征图,利用CNN 对几何特征图的像素进行重新分配,得到重现的低功耗特性,根据低功耗验证结果判断多核芯片是否为低功耗芯片。

验证主系统任务损失函数的计算公式如式(1)所示:

其中,LC为验证主系统的任务损失;CE(Gi,Pi)为单核任务损失函数;Gi为真值标签;Pi为预测标签。

CE(Gi,Pi)可通过式(2)进行计算:

边缘任务损失的计算公式如(3)所示:

其中,LR为边缘任务的损失;smoothL1(di[j])是smoothL1损失函数;di为边缘预测值与真值的差。验证系统总的任务损失等于验证系统主任务损失加边缘任务损失,这证明验证系统有效[15-16]。

3 实验研究

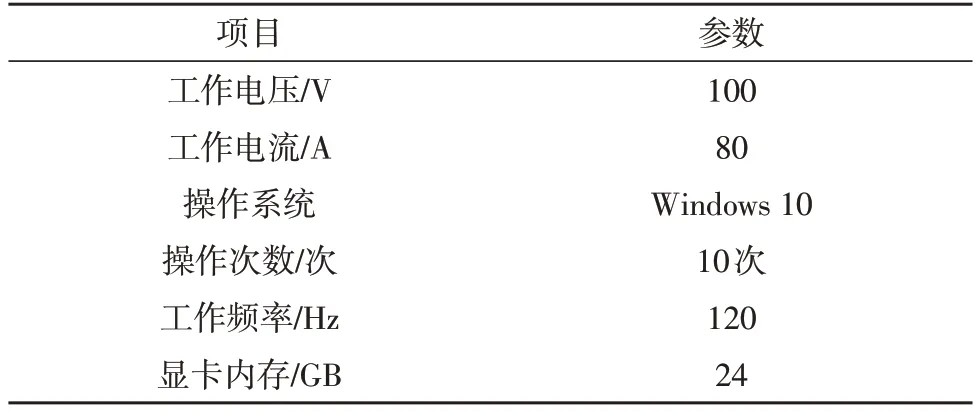

为了检测该文设计的基于CNN 的多核芯片低功耗验证系统的有效性,选用该文提出设计的进行实验研究。设定实验参数如表1 所示。

表1 实验参数

根据上述参数,选用该文设计的验证系统和文献[3]、文献[4]的验证系统进行实验对比。

分别比较验证过程的损失量和平均精度,得到的实验结果如图6-8 所示。

图6 该文系统回归任务损失量实验结果

图8 文献[4]系统回归任务损失量实验结果

根据图6-8 可知,迭代次数共80 次,随着迭代次数的增加,回归任务损失量也在逐渐减小,该文系统的损失值最低,与传统系统相比,损失值降低了10%以上。该文设计的系统利用骨干网络进行分析,通过并行调度技术和任务映射技术,对信息进行层次化分解,确定矩阵类任务,对数据进行动态分析,内部设定了监视子网,能够很好地实现信息采集和计算,确定动态流信息,确保在验证过程中系统的可视化程度和自动化程度都能得以提升。

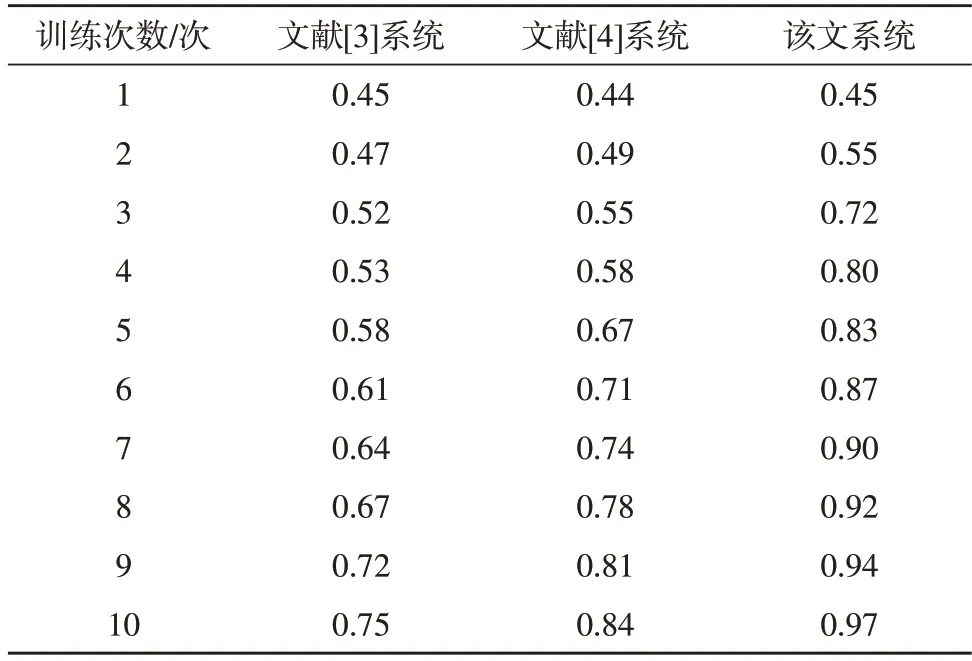

对系统精度进行检测,分别比较包围盒平均精度,得到的实验结果如表2 所示。

表2 包围盒平均精度实验结果

根据表2 可知,包围盒平均精度随着迭代次数的增加而逐渐提高,该文系统精度最高,当迭代次数达到10 次时,文献[3]提出的系统精度为0.75,文献[4]提出的系统精度为0.84,而该文系统精度可以达到0.97,平均精度提高了0.15。

4 结束语

该文利用CNN 重现多核芯片的低功耗特性[17-18],介绍了多核芯片低功耗验证的整体架构,引入的金字塔模型能够准确获取多核芯片的全部信息,利用CNN 技术对多核芯片的低功耗特性进行重新分配,避免了验证过程中低功耗特性的挤压变形,另外,通过对验证系统任务损失的计算,验证了系统的有效性。