C掺杂Sb2Te3高速相变材料

陈元浩,吴良才,黄晓江,宋三年,宋志棠

(1.东华大学 理学院, 上海 201620;2.中国科学院上海微系统与信息技术研究所 集成电路材料全国重点实验室, 上海 200050)

相变存储器(phase change memory, PCM)作为一种新型非易失性存储器,具有CMOS工艺兼容性好、集成度高、擦写速度快等优势。PCM结合相变材料能够在晶态、非晶态状态快速转变的特性,利用材料在晶态和非晶态之间的电学特性的差异,可实现信息存储[1-2]。PCM通常使用的器件结构为T型结构,其通过相变材料层下的加热电极对材料进行加热,使得相变层的晶体结构发生改变,基于此原理存储信息[3-6]。对加热电极施加高频率、短脉宽的电学脉冲,加热电极快速释放热量使得相变层熔融,相变层变为非晶态,电阻处于高阻状态,可实现对PCM的写入(Reset)操作;对加热电极施加中等频率、长脉宽的电学脉冲,使得材料受热结晶,从而电阻处于低阻状态,可实现对PCM的擦除(Set)操作[7-9]。加热电极与材料之间的界面特性会影响器件性能,如影响相变存储器件的功耗、稳定性等性能[10-11]。

PCM中起主导作用的是相变材料,可利用相变材料在晶态和非晶态之间转化的特性存储信息。目前主流的相变材料为Ge2Te2Sb5(GST),GST材料的结晶温度约为87 ℃,热稳定性比较差;同时利用GST制备的PCM器件无法在脉宽小于30 ns的条件下工作,不能满足存储器快速读写的需求。因此,需寻找其他材料替代GST,以制备能够实现快速擦写的相变存储器[12-15]。

与GST材料相变原理相近的是Sb2Te3材料,其结晶速度比GST材料更快,但是纯Sb2Te3材料的热稳定性较差,利用Sb2Te3材料制备的PCM器件在常温下的数据稳定性差,提出碳(C)掺杂Sb2Te3相变材料[16-19]。掺杂C可以有效提高Sb2Te3材料的结晶温度,也会影响Sb2Te3材料内部成键的过程,还能抑制Sb2Te3材料的结晶,使得材料的热稳定性等性能得到明显提高[20]。此外,在制备相变存储器件之前,对加热电极进行表面处理,以改变加热电极表面和相变材料层之间的界面性能,这能有效提高相变存储器件的电阻稳定性等性能[21]。

1 试验部分

利用磁控溅射技术在SiO2片上沉积C-Sb2Te3相变薄膜。将Sb2Te3靶材和C靶材置于射频靶位,固定Sb2Te3靶材的溅射功率为20 W不变。改变C靶的溅射功率,可以改变C元素在沉积的薄膜中的质量分数,使得C靶的工作功率从20 W增加至45 W(分别对应C20W(Sb2Te3)、C30W(Sb2Te3)、C40W(Sb2Te3)、C45W(Sb2Te3)材料)。C-Sb2Te3相变薄膜沉积速率为4 nm/min,设置沉积时间为20 min。在进行溅射前,腔体的真空度要求不超过2.5×10-4Pa。对制备的不同组分的C-Sb2Te3相变薄膜进行电阻-温度(R-T)测试,得到材料结晶温度随C掺杂含量的变化和材料高低阻值的变化。利用XRD测得C-Sb2Te3样品的晶体结构,用XPS分析C-Sb2Te3相变薄膜中的成键信息。

以C靶功率为40 W、Sb2Te3靶功率为20 W为溅射时靶材的溅射功率,制备相变存储器件。器件采用的是传统的T型结构,加热电极为钨电极,中间生长厚度为80 nm左右的相变材料层,再沉积氮化钛作为黏附层,最后生长金属铝薄膜,光刻后形成上电极。包含钨加热电极的流片由中芯国际制造,加热电极直径为190 nm,为了改变加热电极表面和相变材料层之间的界面性能,同时考虑到氧化和污染对金属钨加热电极的影响,本文使用射频容性耦合氢(H)等离子体对基片进行清洗处理。由于加热电极尺寸较小,测试较为困难,为验证H等离子体处理效果,使用硅片作为基底,在其上沉积一层金属钨薄膜,再对钨薄膜进行不同条件的H等离子体表面处理。在处理时,使用发射光谱仪记录等离子光谱,并对经过清洗的C-Sb2Te3相变薄膜进行比较。依据处理效果,选取部分基片,在生长相变材料之前,使用射频电源以功率为40 W、气压为20 Pa的条件生成氢等离子体加热电极表面清洗处理20 min。再将经过表面处理和未进行表面处理的基片一起进行生长相变材料、黏附层和顶电极,制备相变存储器件。对制备的器件施加电学脉冲信号,进行电压-电流测试、循环次数等测试,分析比较存储器的性能。

2 结果与讨论

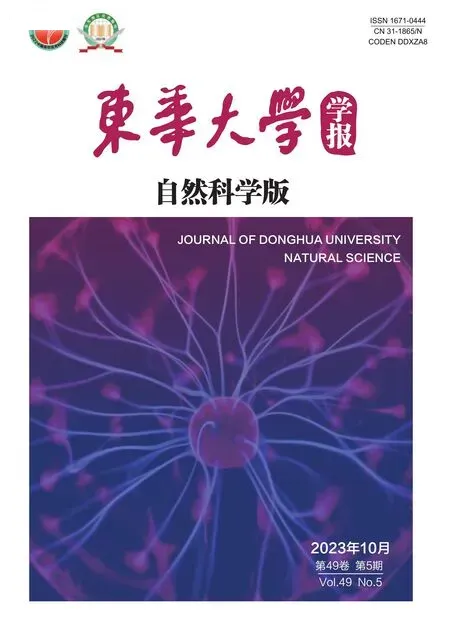

Sb2Te3、C30W(Sb2Te3)和 C40W(Sb2Te3)薄膜的电阻-温度测试结果如图1所示。由图1可知,控制电阻-温度测试系统的加热腔内温度,可改变相变薄膜的阻值。由不同组分C-Sb2Te3薄膜的电阻-温度曲线可以发现,在初始状态时,薄膜均处于高电阻状态。随着加热腔体内的温度升高,薄膜材料电阻会逐步减小。Sb2Te3材料高低电阻之间的差异较小,高电阻与低电阻之间相差不超过一个数量级,因此无法直接从电阻-温度曲线中得到Sb2Te3材料结晶温度的相关信息[15]。C20W(Sb2Te3)薄膜与未掺杂的Sb2Te3薄膜的结晶温度变化不明显,但是C20W(Sb2Te3)薄膜非晶态和晶态的阻值较Sb2Te3有所增大,较晶态阻值较大时有助于降低器件的功耗[14]。相较Sb2Te3而言,C30W(Sb2Te3)和C40W(Sb2Te3)材料非晶态、晶态电阻值的比值更大。用C30W(Sb2Te3)和C40W(Sb2Te3) 材料制备的相变存储器件可以清晰地分辨出高、低电阻间的差异。这个差异能够使得器件更清晰地分辨逻辑“0”“1”[22]。

图1 Sb2Te3、C30W(Sb2Te3)和C40W(Sb2Te3)薄膜的电阻-温度测试结果Fig.1 R-T test results of Sb2Te3, C30W(Sb2Te3) and C40W(Sb2Te3) films

由图1(a)可以看出,相较于其他C-Sb2Te3相变薄膜材料,Sb2Te3薄膜材料的电阻-温度曲线在结晶温度附近的斜率变化较小。当腔体内的温度未达到结晶温度时,Sb2Te薄膜的电阻随着温度上升而缓慢减小;当腔体内的温度加热到结晶温度,薄膜材料的电阻值会突然减小,电阻-温度曲线出现明显的斜率变化,由此可得出材料的结晶温度。根据薄膜电阻随温度变化的测试结果,Sb2Te3薄膜的相变形为在电阻-温度曲线图中不明显,即没有明显的结晶温度拐点。随着C掺杂含量的升高,Sb2Te3薄膜会出现较明显的拐点,其中C30W(Sb2Te3)、 C40W(Sb2Te3)和C45W(Sb2Te3)薄膜均有明显的拐点温度。

由图1(b)可知,C掺杂含量的增加可使材料的结晶温度升高,C30W(Sb2Te3)和C40W(Sb2Te3) 薄膜结晶时的温度超过230 ℃。进一步提高C溅射的功率发现,C45W(Sb2Te3)材料的结晶温度较C40W(Sb2Te3) 薄膜变化较小。在对数坐标下对电阻-温度曲线进行求导,Sb2Te3薄膜的下降速率变化不明显;C掺杂Sb2Te3薄膜的电阻-温度曲线在电阻随温度升高而降低的过程中,出现两次下降速率的转变,分别对应初始非晶态到中间态和中间态到晶态的过程。由第一次转变时的温度(120~160 ℃)可以看出,随着C掺杂含量的增加,材料结晶温度有一定上升;根据第二次转变时的温度(240~250 ℃),得到C30W(Sb2Te3)的结晶温度约为240 ℃,C40W(Sb2Te3)薄膜的结晶温度约为245 ℃。

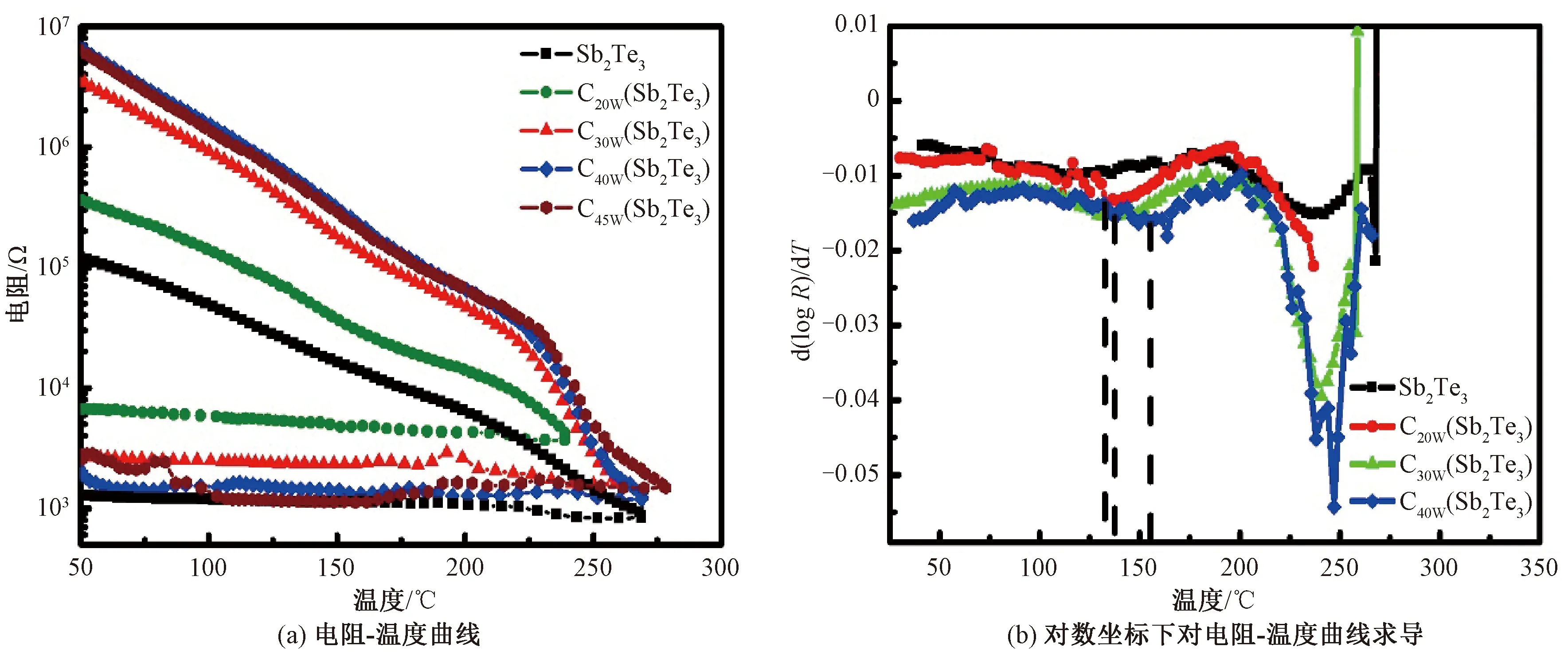

利用XRD获得薄膜内部的晶体结构等信息。用磁控溅射制备的C-Sb2Te3相变薄膜,初始时处于非晶态,为了得到晶态的薄膜,需要对薄膜进行退火处理。在纯氮气环境中以不同温度对薄膜进行3 min退火处理,而后进行XRD测试。图2为C30W(Sb2Te3)和C40W(Sb2Te3)薄膜的XRD图。根据文献[23],常温下Sb2Te3薄膜内部会产生面心立方相(FCC)的衍射峰,材料开始结晶;当温度升高到220 ℃,Sb2Te3薄膜内部的面心立方相的衍射峰消失,同时六方相的衍射峰出现。

图2 薄膜的XRD测试结果Fig.2 XRD test results of the films

由图2可以看出,掺杂C会使得Sb2Te3薄膜的结晶过程受到明显的抑制。退火温度为220 ℃时,材料未出现明显的衍射峰;退火温度为260 ℃时,材料出现六方相衍射峰,随着温度升高,更多的六方相衍射峰出现,由此可知在温度为260 ℃时,Sb2Te3薄膜仍未完全结晶,和掺杂C后Sb2Te3薄膜结晶温度上升的结果吻合。使用Scherrer公式[24]计算晶粒尺寸。

D=Kλ/(Bcosθ)

式中:D为晶粒尺寸;K为Scherrer常数(K=0.89);λ为X射线波长(λ=0.154 nm);θ为衍射角度,(°);B代表衍射峰的半高宽(rad),为方便表征,将弧度制换算成角度制。

衍射峰的半高宽增加,则晶粒尺寸减小。以009峰为例,C30 W(Sb2Te3) 薄膜的009峰分别在260和300 ℃时候的半高宽为0.503°和0.593°;C40W(Sb2Te3) 薄膜的009峰分别在260和300 ℃时候的半高宽为0.507°和0.752°,晶粒尺寸有明显的减小,由此证明C掺杂可通过使晶粒细化从而影响材料的结晶过程。

为分析C掺杂的含量在相变过程中对Sb2Te3薄膜的成键情况的作用,使用XPS对样品进行测试,改变C掺杂含量,测试各元素不同轨道的能量。为避免样品表面受到的污染影响测试结果,需在进行测试前使用Ar离子刻蚀样品的上表面,去除表层可能被氧化或者污染的部分。

图3为不同C含量的Sb2Te3薄膜对应的Sb-3d,Te-3d的XPS图谱峰。由图3可知,随着C掺杂含量的增加,可以看出Sb2Te3中的Sb 3d3/2、Sb 3d5/2、Te 3d3/2、Te 3d5/2的结合能均产生变化,说明C的掺入对于Sb2Te3中的成键情况产生影响。C30 W(Sb2Te3) 薄膜的Sb 3d3/2、Sb 3d5/2结合能分别为528.2和537.5 eV;C40W(Sb2Te3)薄膜能量分别左移0.3 eV。同时,Te 3d3/2、Te 3d5/2的能量也从572.3和582.7 eV变为571.8和582.2 eV。由此可知,掺杂C过程中,C 原子可能与Sb 和Te 原子成键,从而影响Sb2Te3薄膜的成键过程,使得材料的结晶温度等特性改变。

图3 C20W(Sb2Te3)、C30W(Sb2Te3)和C40W(Sb2Te3)薄膜的XPS测试结果Fig.3 XPS test results of C20W(Sb2Te3), C30W(Sb2Te3) and C40W(Sb2Te3) films

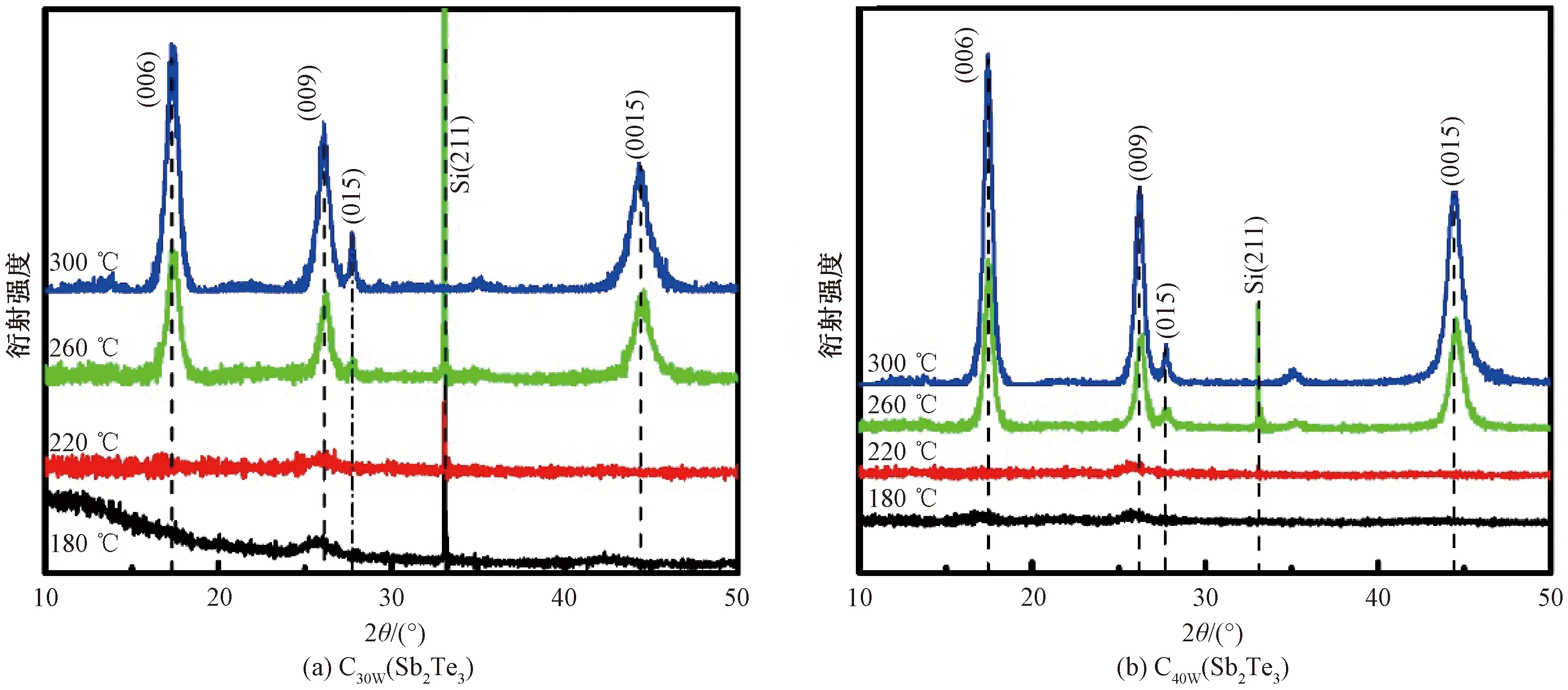

基于C-Sb2Te3相变薄膜的数据,使用合适的组分来制备相变存储器件,测试分析器件的性能。C掺杂的含量越高,结晶温度越高、非晶热稳定性越好,由此选择C40W(Sb2Te3) 薄膜材料为器件的相变层。钨加热电极直径为190 nm,为了改变加热电极表面和相变材料层之间的界面性能,同时考虑到氧化和污染对钨加热电极的影响,使用射频容性耦合氢(H)等离子体对基片进行清洗处理,并使用发射光谱仪记录等离子光谱。经H等离子进行表面清洗的等离子体光谱如图4所示。由图4可知,使用13.56 MHz的射频电源(功率分别为30和50 W,气压为20 Pa)进行放电,采集的光谱上均出现氢656.28 nm特征峰,说明腔体内等离子体中存在大量活性的H原子。H原子可以清除样品表面的氧化层。

图4 经H等离子进行表面清洗的等离子体光谱Fig.4 Plasma spectra of using hydron for surface cleaning

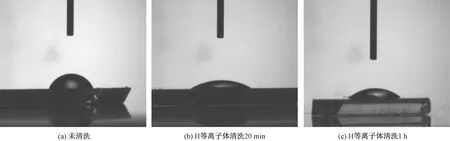

使用功率为40 W的H等离子体先对制备的钨薄膜进行清洗处理,再对其亲水性进行测试。钨薄膜表面的亲水性测试结果如图5所示。由图5可知,钨薄膜表面清洗处理的时间越长,其亲水性越好,说明H等离子体对电极表面有改性作用;经过20 min的H离子处理,水接触角由64.2°变为36.2°,而经过1 h的H离子处理,水接触角变为27.1°。由于金属一般是亲水性,其表面越光滑。亲水性越好,因此可以推测H等离子体处理加热电极表面的使用可以使材料的表面质量改善。

图5 钨薄膜表面的亲水性测试结果Fig.5 Hydrophilicity test on the surface of tungsten film

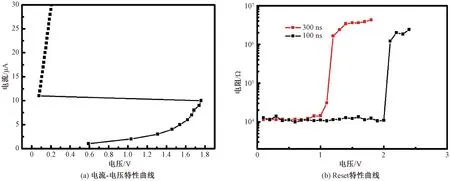

基于C40 W(Sb2Te3)材料制备的相变存储器件的电流-电压特性曲线和不同脉宽下器件的RESET特性曲线如图6所示。由图6(a)可知,当电流上升到阈值电流(Ith)时,C40 W(Sb2Te3)材料发生相变,由非晶态转化成了晶态,导致电压突然间减小。此时的Ith为11 μA,对应的阈值电压为1.8 V;继续增大电流,C40W(Sb2Te3)材料处于晶态,电阻稳定为低阻,则电流值和电压值呈线性关系。对重置为低阻的器件施加脉冲,使得器件回到高阻,可以发现脉宽减小,其所需的电压值增大。脉宽为300 ns时,电压为1.1 V即可转变为高阻值,但脉宽100 ns电压需要2 V才能转变为高阻值状态。由于材料相变所需的能量固定,减小施加给器件的脉冲电压时间,势必要增加施加的电压,因此材料可以产生相变。

图6 C40W(Sb2Te3)材料的电流-电压特性曲线和不同脉宽下器件的Reset特性曲线Fig.6 I-U characteristic curve of C40W(Sb2Te3) device and Reset characteristic curves of the device at different pulse widths

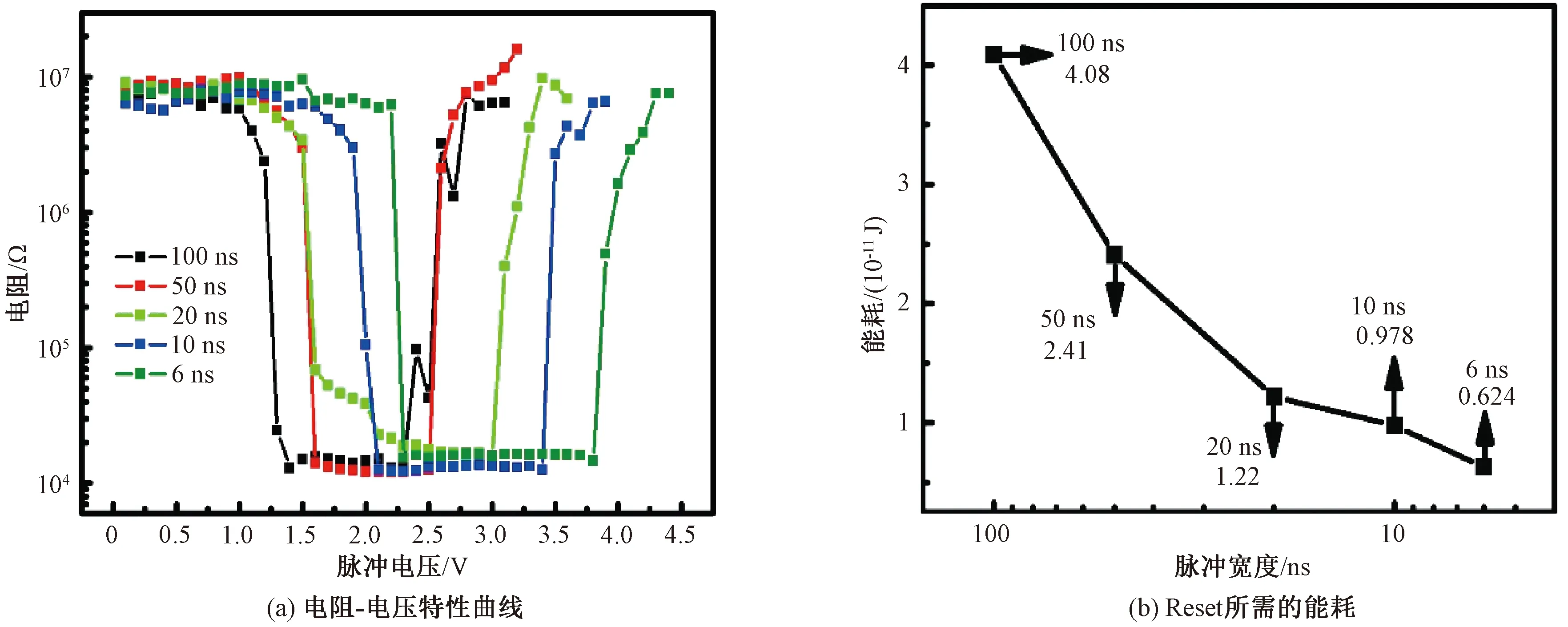

通过电阻-电压测试对相变存储器件单元进行重置操作,使得器件回到高阻状态,电阻为106~107Ω。当增加的脉冲信号电压达到SET所需的阈值时,器件由高阻状态变为低阻状态,电阻变为104Ω左右。继续增加脉冲电压,相变材料的电阻值保持低阻值。这是因为当施加的脉冲电压超过Reset所需的阈值时,材料内粒子的排列由有序的多晶态变为无序的非晶态,电阻回到高阻状态。相比GST材料,同等脉冲宽度下,Sb2Te3所需Reset电压更小,消耗的能量更低。同时,C-Sb2Te3材料的高低阻值之间的比例稳定,阻值差距在两个数量级以上,可以有效区分器件单元的“0”“1”状态。

基于C40 W(Sb2Te3)材料制备的相变存储器件在不同脉宽下的电阻-电压特性曲线和不同脉宽下Reset所需的能耗如图7所示。制备的相变存储器件单元的材料相变需要一定的能量,因此不断减小施加电压的脉冲宽度,Set与Reset所需要的电压都会上升,和不同脉宽下器件的Reset曲线结果吻合。将脉宽减小到6 ns,器件依旧可以在较小的电压情况下(Set 2.3 V/Reset 3.8 V),进行完整的相变操作。由图7(b)可知,器件在不同脉宽下,Reset所需的能耗。脉冲宽度为50 ns时,传统GST的能耗大于4.7×10-10J[12]。相较GST,C-Sb2Te3材料的能耗更低。脉宽为6 ns时,能耗为6.24×10-12J,器件可以同时满足在低能耗和快速读写操作的需求,具有应用前景。

图7 C40W(Sb2Te3)器件在不同脉宽下的电阻-电压特性曲线和不同脉宽下Reset所需的能耗Fig.7 R-U curves of C40W(Sb2Te3) device at different pulse widths and the energy consumption required for Reset for the device at different pulse widths

由H等离子体处理加热电极表面的测试结果可知,H等离子体处理能够改变加热电极表面和相变材料层之间的界面性能。因此,选取一组相变存储器件,在生长相变层之前,先使用H等离子体进行清洗处理,比较经H等离子体处理与未经H等离子体处理的相变存储器件的性能。

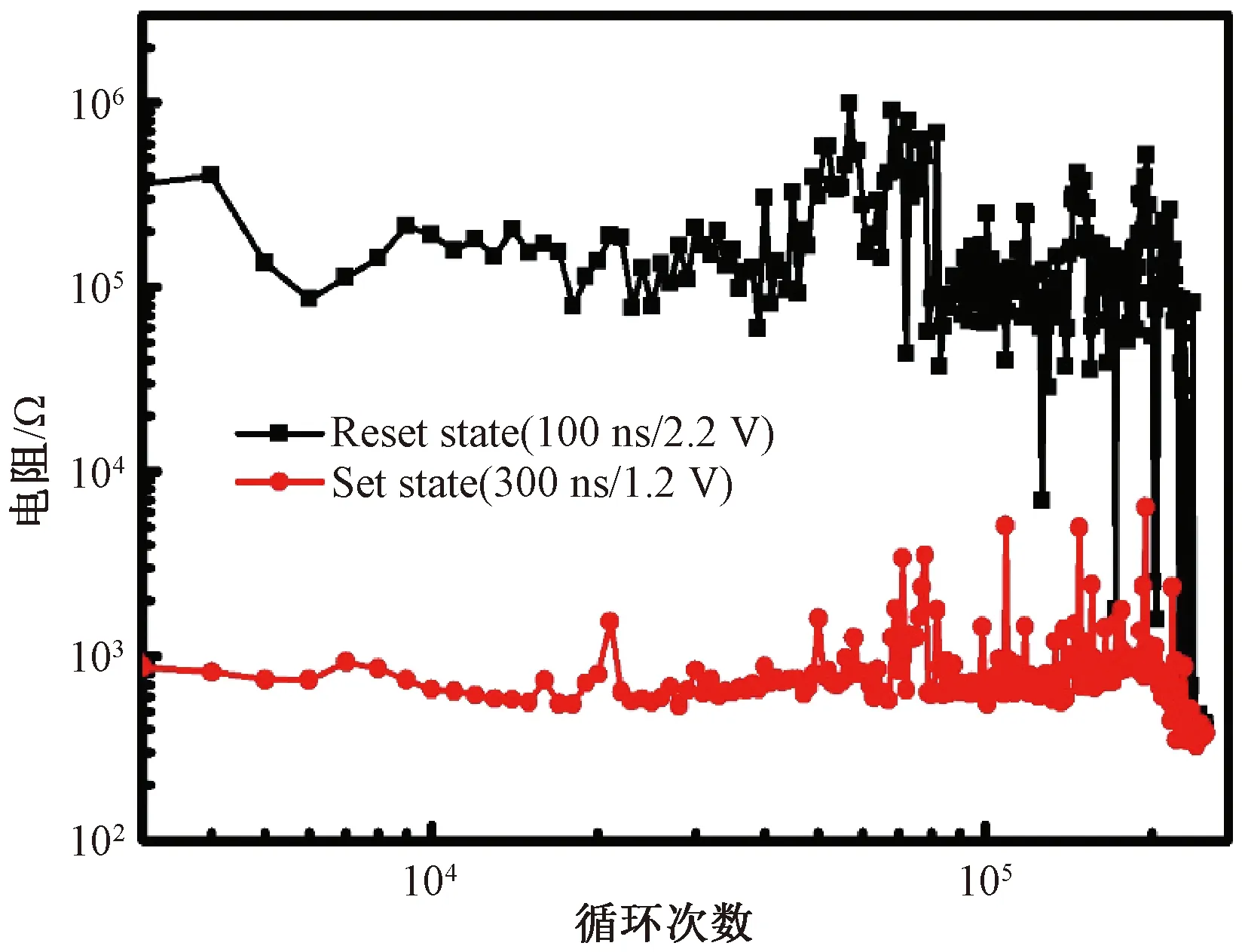

在加热电极未进行处理的情况下,基于C40W(Sb2Te3)制备相变存储器件,并对其擦写循环性能进行测试,相变存储器件的疲劳特性图如图8所示。由图8可知,高电阻与低电阻的阻值范围分别为105~106Ω和103~104Ω,高电阻和低电阻之间可以保持2个数量级左右的差距,但电阻值不稳定。对器件施加脉冲电压,测试器件的疲劳性能。设置Set的脉冲为300 ns/1.2 V,Reset的脉冲为100 ns/2.2 V,器件循环约4×104次后,高电阻和低电阻状态均出现明显的数值波动。在接近1.7×105次循环后,高低阻值无法再进行区分,器件失效。

图8 C40W(Sb2Te3)器件的疲劳特性图Fig.8 Cyclability properties of C40W(Sb2Te3) device

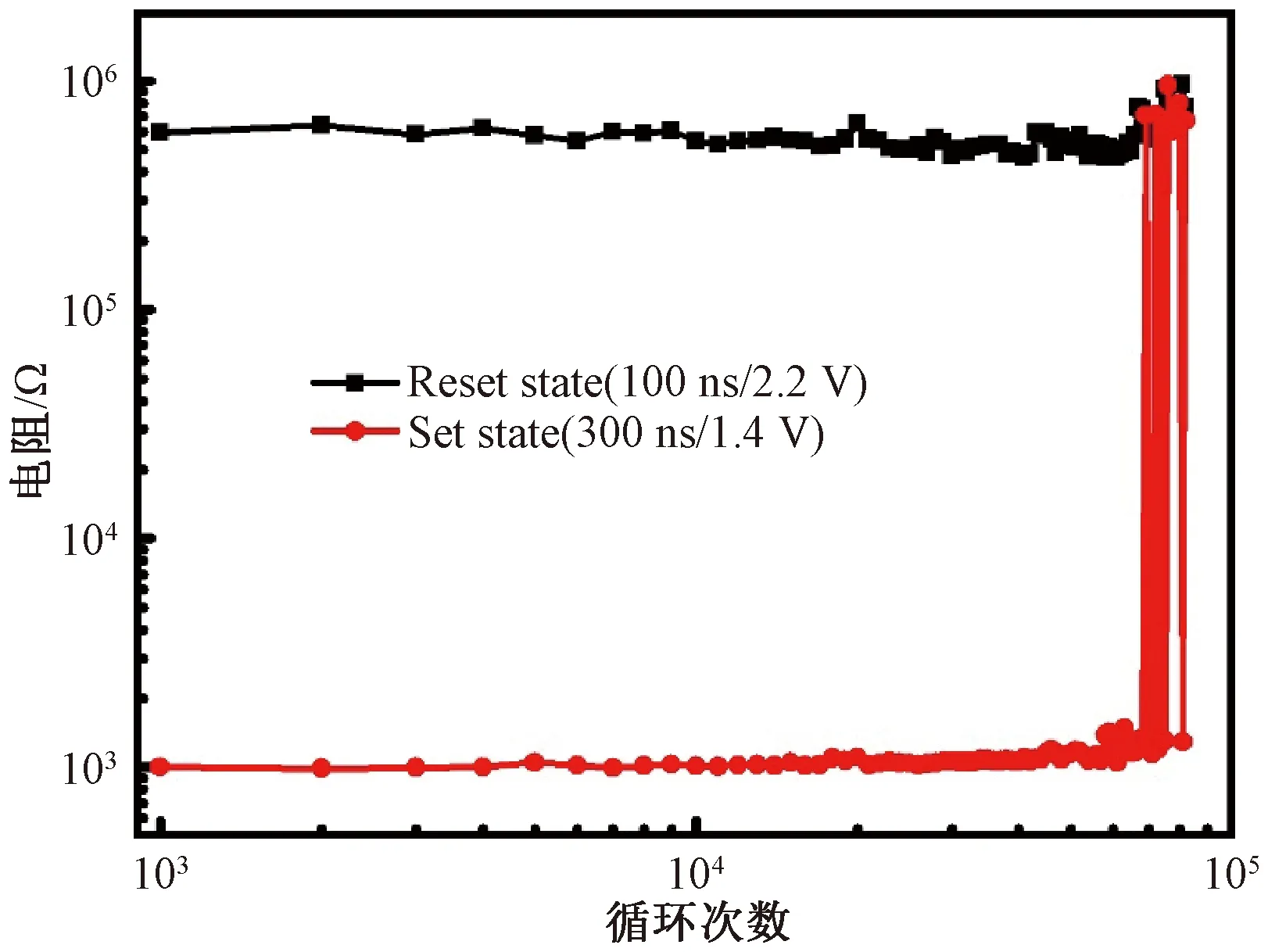

加热电极经H等离子体处理后的C40W(Sb2Te3)器件的疲劳特性如图9所示。由图9可知,使用H离子清洗加热电极表面,相变存储器件的高电阻约为6×105Ω,低电阻约为103Ω,电阻值的波动明显减小,阻值更稳定。设置Set的脉冲为300 ns/1.4 V,Reset的脉冲为100 ns/2.2 V,对器件施加脉冲电压,测试器件的疲劳性能,器件循环次数达7×104次后高电阻和低电阻才出现明显的波动。

图9 氢等离子体处理后的C40W(Sb2Te3)器件的疲劳特性Fig.9 Cyclability properties of C40W(Sb2Te3) device with hydrogen plasma cleaning

3 结 语

以Sb2Te3为基础,使用C掺杂制备C-Sb2Te3薄膜与相变存储器件。通过电阻-温度、XRD、XPS、亲水性、电阻-电压、电流-电压、擦写循环等测试,研究C-Sb2Te3薄膜以及基于其制备的存储器件的性能。电阻-温度测试结果显示,掺杂C后的Sb2Te3的薄膜,结晶温度有明显提升,同时高、低阻态间的阻值差异增大;XRD测试结果表明,掺杂C会使得材料的晶粒尺寸缩小,可改善材料受热膨胀的影响;C的掺入也会影响Sb2Te3材料的成键情况,使得其结晶温度升高,增加非晶态的电阻。使用H等离子体处理钨加热电极表面后,器件高、低阻态的阻值稳定性明显提高,说明H等离子体处理能够改善加热电极与相变层之间的界面性能。C掺杂可以有效改善Sb2Te3相变材料的性能,器件可进行105次可靠的高速擦写操作,是一种对相变材料进行掺杂改性的可行方案。