AlN/GaN HEMT毫米波器件结构仿真研究

李晗溱,宓珉瀚,周雨威,龚 灿,马晓华

(西安电子科技大学 微电子学院,西安 710071)

0 引言

第三代半导体材料GaN具有宽禁带、高电子饱和速度[1]的优势,使其能够兼顾更高的工作频率与更大的输出功率密度[2-6]。GaN基HEMT器件的栅长一般在纳米尺度,因此会产生严重的短沟道效应和源漏穿通效应[7],使器件缓冲层的泄漏电流很大,甚至无法夹断。缓冲层的泄漏电流会严重限制器件的频率和功率特性,但采用强极化势垒AlN[8]则可以改善此现象,由于AlN/GaN异质结的自发极化和压电极化[9-10]很强,因此可以在AlN势垒很薄的情况下产生很高的二维电子气密度,从而提高器件的纵横比、抑制短沟道效应[11]。2008年,Zimmermann等[12]制备出势垒层厚度为3.5 nm的AlN/GaN HEMT,测得峰值跨导为480 mS/mm,电流截止频率fT和最高振荡频率fmax分别为52 GHz和60 GHz。2011年,Medjdoub等[13]在4英寸硅衬底上通过MOCVD生长出势垒层厚度为6 nm的AlN/GaN异质结,并在该外延片上制备出栅长为160 nm的器件,器件的最大跨导为600 mS/mm。fT和fmax分别可达103 GHz和162 GHz。2012年,Shinohara等[14]在SiC衬底上制备的20 nm栅长的AlN/GaN HEMT的最大饱和电流密度可以达到4 A/mm,最大跨导超过1 S/mm,fT和fmax分别高达342 GHz和518 GHz。2015年,Shinohara等[15]又报道了电流截止频率fT为454 GHz、最高振荡频率fmax为444 GHz的AlN/GaN HEMT。可见,AlN作为强极化势垒层能产生较高的截止频率,再结合减薄势垒层厚度或减小栅长可以进一步优化器件频率特性。因此,AlN/GaN HEMT器件在未来高频应用方面有极大的潜力。

本文借助二维器件仿真工具Silvaco TCAD,系统分析对比了不同势垒结构以及不同尺寸栅长对器件的特性影响。从而研究器件纵横比与阈值电压、最大直流跨导、截止频率等参数的关系,在此基础上进一步优化器件结构,旨在为后续的器件制备提供理论依据。

1 器件结构与研究方法

本文仿真采用的器件结构如图1所示,栅源间距Lgs为0.9 μm,栅漏间距Lgd为2 μm,栅长Lg可调;GaN沟道层厚度为400 nm,缓冲层厚度为500 nm,SiN厚度为2 nm,AlN势垒层厚度可调。

图1 器件结构示意图

仿真时采用的物理模型分别为能带定义模型K.P模型、SRH(Shockley-Read-Hall)复合模型、平行电场依赖模型fldmob(其中电子迁移率MU0=750 cm2/V·s,电子饱和速度VSATN=8.2×106cm/s)以及极化模型。定义势垒层、沟道层与缓冲层的掺杂浓度为1015cm-2。

在上述器件结构的基础上,首先固定栅长为100 nm,势垒层厚度分别取2.5 nm、4 nm、5 nm和6 nm。对其进行直流特性及小信号特性的仿真,对比得出势垒层厚度的最优值为4 nm。确定势垒层厚度后,对栅长分别为50 nm、100 nm、150 nm和200 nm的器件进行直流特性及小信号特性的仿真,研究器件的栅长与阈值电压(Vth)、最大直流跨导(Gm.max)、截止频率(fT&fmax)等电学参数的关系,进而分析了器件纵横比与短沟道效应的关系以及由于短沟道效应引起器件特性退化的原因[16],最终确定最优栅长。

2 结果与讨论

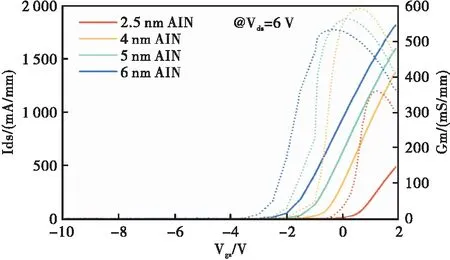

2.1 势垒层结构优化

栅长为100 nm的具有不同势垒厚度的AlN/GaN HEMT器件的转移和输出特性曲线如图2和图3所示。对器件的转移特性进行仿真时,将漏极电压Vds偏置为6 V,栅压Vgs从-6 V扫描至2 V;对器件的输出特性进行仿真时,器件的漏极电压Vds从0 V扫描至10 V,栅压取2 V~-8 V,步长为1 V,图中仅对Vgs=2 V时的最大饱和电流作对比。

图2 不同势垒层厚度的AlN HEMT转移特性曲线

图3 不同势垒层厚度的AlN HEMT输出特性曲线

从转移特性曲线中可以看到,器件阈值电压随势垒层厚度的增加负漂,这是因为势垒越厚,二维电子气(two-dimensional electron gas,2DEG)密度越大,需要更负的栅极偏置来耗尽2DEG,实现器件关断。势垒层厚度为4 nm时跨导最大(592 mS/mm),跨导随势垒层厚度的增加先增大后减小。在势垒层厚度大于4 nm时,跨导随势垒层厚度的增大而减小,主要原因在于随着势垒层厚度的增加,栅极对沟道电子的控制能力减弱,即跨导与势垒层厚度成反比,如式(1)所列。随着AlN势垒层厚度的增加,AlN势垒层中会出现局部弛豫现象,这会产生更多的失配位错,失配位错的增加会对界面质量造成不利影响,进而增强了散射机制对迁移率的影响[11,17]。与此同时,随着势垒层厚度的增加,2DEG密度增加,意味着2DEG更接近界面更容易受到散射机制的影响,从而降低迁移率,影响跨导。而当势垒层厚度小于4 nm时,跨导减小,如图4所示。势垒层厚度过小导致2DEG密度急剧下降,势垒层厚度为2.5 nm时,器件的跨导减小,原因是2DEG密度减小导致的有源区电阻增大,从而抑制非本征跨导的提升,如式(2)所列。

图4 不同势垒厚度的AlN HEMT载流子分布图以及能带图

(1)

(2)

从输出特性曲线中可以看到,Vgs=2 V时器件的最大饱和电流随势垒层厚度的增大而增大,这也与图4中载流子面密度随势垒层厚度的变化趋势相吻合。势垒层厚度为2.5 nm时,器件的饱和电流远小于其他3个厚度的器件。

最后对4种不同势垒厚度的器件进行小信号特性的仿真,如图5所示,势垒层厚度为4 nm时的fT和fmax最大,随势垒层厚度的增加,截止频率减小。由式(3)所列,截止频率和跨导正相关,因此截止频率随势垒层厚度的变化趋势与跨导随势垒层厚度的变化趋势一致。如表1所列是对不同势垒厚度的AIN HEMT的各项参数的对比,基于本文仿真目的,为确定适合高频应用的器件结构,最终确定势垒层厚度为4 nm。

表1 不同势垒层厚度的AlN HEMT的各项参数对比

图5 不同势垒厚度的AlN HEMT小信号特性曲线

(3)

2.2 栅长优化

基于上述分析,固定势垒层厚度为4 nm的具有不同栅长的AlN/GaN HEMT器件的转移和输出特性曲线如图6和图7所示。对转移特性和输出特性的仿真偏置与上一小节一致。

图7 不同栅长的AlN HEMT输出特性曲线

从转移特性曲线中可以看到,阈值电压随栅长的减小而负漂,主要原因在于短沟道效应,栅长越小,纵横比越小,短沟道效应越严重,需要更负的栅压才能夹断导电沟道。跨导随栅长的减小先增加后减小,这也是由于栅长的过度减小,使得短沟道效应变严重。

从输出特性曲线中可以看到,随着栅长的减小,器件饱和输出电流增大,这是因为在源漏间距固定的情况下,栅长减小会使得沟道电阻减小,因此饱和输出电流增加。

如图8所示,栅长分别为100 nm和50 nm时,器件在关断状态下(Vgs=-6 V)漏压为0 V和6 V的栅下载流子分布。从图8(b)与图8(d)的对比可以明显看出,栅长为100 nm时,器件在漏压6 V的情况下还能很好地关断,但栅长减小至50 nm后,栅下载流子分布明显增加。背景载流子浓度的增大会在漏压较大时造成源漏穿通现象,使得亚阈值电流增大,甚至造成器件难以关断的情况。

图8 栅长分别为100 nm和50 nm时不同漏压下的载流子分布

如图9所示,为了解释短沟道效应对器件特性退化的影响,又进一步对比了关断状态下(Vgs=-6 V)不同栅长器件在不同漏极电压下异质结处的导带图,x轴坐标值为相对于源极的距离。势垒高度随栅长的减小而减小,主要原因在于栅长越长,耗尽作用越强;与此同时,当漏极电压为30 V时的势垒高度相对于0 V时的均有下降,其中栅长为200 nm时的降幅为4.9%,150 nm时为6.3%,100 nm时为8.4%,50 nm时为14.8%,可见随着栅长的缩短,DIBL现象越来越严重。这是因为随着栅长的缩短,势垒降低越来越严重且势垒的宽度越窄,势垒高度降低和势垒宽度变窄使载流子更容易越过势垒,从而亚阈值电流增大。

图9 不同栅长器件在不同漏压下异质结处的导带图

如图10和图11所示,对不同栅长的器件进行了小信号仿真,器件截止频率随栅长的减小而增大,与器件最大跨导变化趋势不一致,这是因为器件寄生电阻Cgs和Cgd随着栅长的减小均减小。结合式(3)可知,在栅长大于50 nm的范围内,寄生电容对器件截止频率的影响比跨导大,但基于上述分析可知,栅长减小至50 nm时短沟道效应严重,因此折中取栅长为100 nm。

图10 不同栅长的AlN HEMT小信号曲线

图11 不同栅长的AlN HEMT的截止频率变化

3 结论

本文通过对不同势垒层结构以及不同栅长的器件进行直流特性和小信号特性的仿真,分析了纵横比与短沟道效应的关系,以及短沟道效应引起器件特性退化的原因。对比确定出AlN/GaN HEMT的势垒层厚度为4 nm,栅长为100 nm时截止频率较高,且不会产生严重的短沟道效应。