提升微波固放电路电流承载力的复合膜层结构

王 平,张 楠,靳文轩,王 峰

(1.中国空间技术研究院西安分院,西安 710000;2.西安电子科技大学 微电子学院,西安 710126)

0 引言

星载固体功率放大器是宇航电子产品的重要类别,承担微波信号的功率放大、增益控制、相位控制等功能。随着无线通信新标准新技术的发展,日益要求提高微波固态功率放大器的性能,使之在更宽的频带内,具有更高的输出功率、效率、可靠性以及线性度[1]。微波功率模块实现发射信号的合成和放大,是机载、舰载、星载等新一代固态有源相控阵雷达的核心部件—T/R组件中非常重要的组成部分[2]。随着星载用途不断扩大,为同时满足大功率和小型化的目标,原有的小功率放大器逐步被MMIC芯片所替代,大功率、大体积的行波管放大器逐渐被GaN固态功率管替代。国产星载固放实现了从无到有、从“大个头”变为小模块,逐渐高频化、大功率的质的飞跃[3]。星载Q频段和W频段连续波固放在我国首次开发成功并在轨搭载验证[4]。创造性将固态和真空器件的优点有机结合的微波功率模块(MPM),具备了大功率、高效率、小体积和低噪声等优点,可用于空间通信、电子对抗以及民用领域,也是近年来微波固放的发展方向。[5-6]

微波固体功率放大器的应用中,由于大功率微波信号的加载,较大电流在功率模块电路中传输,电路导体发热明显,导体可承受的电流密度与电路导体阻抗对于保证电路的性能有着重要影响。因此,功率模块中的固放电路基板的电流承载能力成为衡量功率模块可靠性的重要指标。

功率模块中良好的器件散热依赖于优化的散热结构设计、封装材料选择(热界面材料与散热基板)及封装制造工艺等。基板材料的选用是关键环节,直接影响到器件成本、性能与可靠性[7]。电路基板既是固放微波信号的传输途径,也是功率芯片的安装载体、机械支撑保护和芯片工作热量的散热通道,对于微波固体功率放大器的正常应用十分重要。功率放大信号需要从基板上制作的电路线条上传输,为将大功率电路、器件的热能及时散去,基板的热导率必须很大[8]。但是,考虑到氧化铍基板粉末的剧毒特性、氮化铝基板的易水解特性以及覆铜板介质材料的低导热和低膜层附着强度特点,综合制造成本,仍然是氧化铝基板的使用能满足大多数需求。

目前,业内对于微波固放电路基板的电流承载能力的研究较少。程浩等[7]针对常用陶瓷基板开展了金属层结合强度、可焊性、导热性、可靠性等特性测试,但对基板载流能力没有给出定量数据;王志会等[9]基于氮化铝基板采用厚膜和薄膜工艺实现了射频功率负载的制作,但无电流承载力的技术数据;马丽琴[10]针对微波功放中通过焊膏粘结的印刷基板提出了散热工艺解决方案,但对印刷基板自身电流承载能力没有涉及;葛琪[11]对CuCGA互连焊点电流承载能力进行了研究,但主要针对面阵列封装器件的焊点尺寸对电流密度和温度的影响,不涉及电路基板。赵艳雯[12]针对不同厚度铜箔和不同线径的覆铜PCB走线进行了电流承载能力研究,但对于氧化铝基板上的薄膜线路的电流承载能力没有涉及。周勤[13]在高导热氧化铍基板上探索氧化铝体系厚膜浆料的兼容性,但厚膜工艺与氧化铝基板上薄膜工艺的差异较大。

星载微波固放中,基于高纯氧化铝陶瓷基板和薄膜工艺制作的固放电路十分重要。但是,常规固放电路的膜层厚度较薄,膜层耐焊性有限,实践中曾出现信号传输线条功率加载下烧断的情况。因此提高星载微波固放电路电流承载力十分必要。

文章通过分析星载微波固放电路的电流承载力需求和现行工艺方法的局限性,提出了一种基于薄膜工艺的高导电率、高耐焊新型复合膜层结构,在满足大功率应用需求对于电流承载力需求的同时,明显提高电路应用耐焊性,保持了高的电路可靠性。

1 星载微波固放电路的电流承载能力需求分析

1.1 整体电流承载能力需求分析

星载固放产品主要由EPC、射频链路以及控制电路三部分组成,其中射频电路的主要功能是将输入的射频信号进行多级放大,保证固放输出达到要求的功率值。因此承受较大的工作电流。

星载微波固放电路在工作时,不同频段固放电路能够输出的最大功率不同,基于陶瓷基板设计和制造的L、S频段固放产品,应用功率已达到200 W,5~10年后最高功率希望达到500 W,固放电路线条上通过的电流相比以往提高了10倍,固放产品的热流密度也提高了10倍,最高热流密度需求达到1 kw/cm2。我国自主研发的四代接收机固放模块,目前工作电流要求达到10 A,未来其工作电流最高要求达到20 A以上,明显高于常规薄膜电路和LTCC低温共烧陶瓷电路上允许的电流应用水平。

1.2 局部电路电流承载能力需求分析

固放电路中的高阻线承受着功率放大过程的主要电流,不同线宽的高阻线有着最低的电流承载能力需求,而不同导体厚度的高阻线可承受的最大极限电流不同。某产品对于固放电路中的不同导体厚度高阻线应承受最小电流提出了如表1所列的具体要求。

表1 高阻线电流承载能力需求

从表1中数据可知,固放电路中对于电流承载能力提出了至少9 A的应用需求。文献报道中0.635 mm宽、2.5 μm厚的金线条,理论上可以承受的最大电流可达9.6 A[14]。实际试验结果显示,高纯氧化铝基板上制作的焊点周围无缺陷的镍铬-镍-金结构的微带高阻线可承受9 A、24 h的高电流,而存在明显表面划伤的高阻线,5 A电流加电15 min后,出现线条烧断的故障现象。

上述数据表明,固放电路的高阻线表面存在划伤等缺陷会显著降低固放电路的电流承载能力。此外,考虑到因固放产品是散热型产品,实际宇航应用中会考虑到热分析及砷化镓、氮化镓器件的结温及一级降额,同时考虑到基板上器件焊点的软化点,电流通过时电路基板的温升上限必须要考虑进去。参照介质基板通用试验规范中的试验温度100 ℃,陶瓷基板载流能力导致的温升上限不应超过100 ℃。在满足固放电路高阻线上耐受极限电流、基板整体温升的同时,高阻线的制作工艺还需要考虑到高阻线的压降不能过大,导体阻值尽可能小。

2 提升电路电流承载力的复合膜层结构研究

为了提升单层固放电路的电流承载力,基于高纯氧化铝基板(εr=9.9,标称热导率=27 W/m·K)和高介电常数基板(εr=36.5,标称热导率=2.1 W/m·K),从材料的选择与优化、复合结构膜层加厚技术、图形制作工艺技术几个方面进行了研究。

2.1 材料的选择与优化

Cuviello和Coulton总结了不同基板上不同方阻的可耐受电流值,具体如表2所列[14]。表2可知,方阻越大,可耐受电流越小;基板材料不同,耐受电流也不同。含有薄膜电阻的大功率固放电路,首选氧化铍、硅等高导热率基板材料,其次考虑氮化铝,继而采用氧化铝基板。考虑到氧化铍材料的剧毒特性、硅材料的微波损耗较大以及氮化铝基板的较高成本等因素,氧化铝基板是较好的选择。而电路中含有薄膜电阻,将造成局部电流承载能力的显著下降(电阻部位导电性差,热量更为集中)。

表2 常用基板上不同方阻耐受电流数据

基板材料已确定前提下,提升电路的电流承载力,重点在于电路膜层材料的选择。常规膜层体系中不同的材料担负不同的作用,具体如表3所列。

表3 常用膜层特性表

如表3所列,提高电流承载力,需要采用金、铜这样的高电流导体层。高的金层与铜层厚度可以保证高的电流承载力,但会带来膜层附着恶化、线条轮廓变差、加工难度与加工成本增加等问题。最终是否完全采纳表中的厚度数据,要根据膜层附着力、电路线条轮廓外观、加工难度、加工成本等影响因素综合考虑。

2.2 复合膜层结构膜层加厚技术研究

基板材料确定后,微波固放电路的膜层厚度决定了其能承受的最大信号功率。为适应大功率电路的电流承载能力需求,必须开发膜层厚度数倍于常规薄膜陶瓷电路的加厚膜层固态电路。常规情况下,基于氧化铝基板薄膜工艺体系制作的MIC产品,最顶层导电层Au约为3 μm的,膜层总体厚度不超过4 μm。这一总厚度难以满足更大功率部件的应用需求。

理论上,根据公式R=ρl/(d.w),保持ρ(金的材料电阻率)、l(线条长度)和w(线条宽度)不变,将金层厚度d加厚到2.54 μm的3倍即7.62 μm,金的导体电阻将缩小为原来的1/3,而相同功率下,电流可承载能力可增加为原来的1.732倍,如0.635 mm宽度线条最大可承受16.6 A的电流(此为理想情况计算值,实际膜层表面缺陷会导致可耐受电流显著下降)。但是,电路装配过程中在金焊盘上常采用Sn63Pb37焊料进行器件焊接,为避免“金脆”现象,需要多次搪锡去除厚金层,制造效率较低,可靠性也存在隐患。用其他金属进行膜层加厚,则无法满足键合需要。因此需要制作复合膜层以满足电路的不同功能需求。为此需研究薄膜加厚的具体复合膜层结构、复合结构中每层膜层的制作工艺方法与具体参数、膜层总体厚度与应力的控制方法等,涉及到膜层结构设计、镀液(镀金、镀铜、镀镍)体系选择、镀层厚度确定与优化、膜厚控制、层间附着考核等多方面内容。参考表3,最终确定了NiCr-Au-Cu-Ni-Au这一复合结构。复合膜层结构中,镍铬层为溅射工艺生成,Au、Cu 和Ni层均采用电镀工艺形成。

复合膜层结构中膜层的选择以及厚度的确定,主要考虑保证大承载电流能力的同时,应减轻工艺难度、确保不同膜层之间的性质兼容以及膜层的应用长期稳定性。铜层的加厚,可有效降低电路温升,但会增大电路图形制作难度;镍层厚度的增加,确保了表面金层不被铜层扩散影响,但降低了膜层结构的导电性,增加电路的温升。

复合膜层加厚过程不仅仅是厚度提高,更要考虑加厚过程对于膜层应力、图形精度、膜层附着力、锡焊工艺兼容性、键合工艺兼容性等多方面的影响。复合膜层的加厚方法一般有两种:电镀与溅射。溅射的缺点是时间长、成本高,因此选择效率较高的电镀方式。电镀加厚首先需要解决多层结构膜层的应力累积造成的附着力问题。

图1为采用仿真软件仿真的NiCr-Au-Cu-Ni-Au这一复合结构中,各层膜的应力分布情况.从图1中可以看出,各层膜中镍层的应力值最大,底层的金膜和顶层的金膜所受应力则最小,每层的应力最大点均位于高阻线最密集处。经分析,镍层应力最大的原因在于,镍层除受自身热膨胀产生的应力作用之外,由于位置处于铜层和金层之间,受上下层金属的挤压作用也产生一定应力作用[15]。

图1 复合膜层结构中不同膜层应力分布图

复合膜层结构构建的是否合理,一方面应该考虑氧化铝基板和其上沉积的各种膜层各自的应力分布,另一方面还应考虑复合膜层结构与氧化铝基板界面的应力。理论上,界面处表面粘附的屈服应力一般为50 MPa。如果有效力增大至该值以上,则膜层和基板局部发生分离。一旦膜层自基板发生分离,芯片工作产生的热量无法通过基板、热沉传递到管壳外,电路的局部传热受阻,可能使膜层发热过度导致电路断开失效[15]。

图2显示了加热工作过程中作用在基板和复合膜层之间粘附层上的有效力。最大界面应力为5.64 MPa,比理论可以承受最大的屈服应力小一个数量级,此膜层结构在粘附应力方面满足要求。

图2 膜层与基板界面应力分布图

图3为复合膜层结构保持总厚度不变时,铜层厚度增大时,各层最大应力的变化曲线,可以看出,各个膜层自身应力随着铜层变厚都在变小[15]。

图3 膜层应力随铜层厚度的变化曲线

复合膜层结构与基板之间界面应力随铜层厚度的变化情况如图4所示。可知,随铜层厚度增加,界面应力也随之变大,但仍比理论可以承受最大的屈服应力小一个数量级,说明该膜层复合结构粘附应力满足要求[15]。

图4 界面应力随铜层厚度的变化曲线

从图5仿真结果可知,随着镍层厚度从1 μm增加到2 μm,电路上最高温度持续升高。

图5 最高温度随镍层厚度的变化情况

图6为复合膜层结构保持总厚度不变时,镍层厚度变化时,各层最大应力的变化曲线,可以看出,各个膜层应力随着镍层变厚都在逐渐变大[15]。

图6 膜层应力随镍层厚度的变化情况

经采用仿真软件进行复合膜层的电、热多维物理场仿真分析,结合实际工艺实验验证,最终确定了NiCr(500 Å)-Au(2~3 μm)-Cu(3~5 μm)-Ni(1~2 μm)-Au(3 μm)这一最终复合膜层结构。这一结构的复合膜层结构整体应力适中,而加工难度较小,工程应用可行性高。

2.3 复合膜层结构图形制作工艺技术研究

多层复合膜层电路,由于工艺流程中不同材料多次刻蚀、多次电镀的工艺特点,如不做控制,图形精度明显低于常规电路。在复合膜层结构的电路图形过程中,影响图形精度的因素包括掩膜版图形精度、图形转移精度、图形刻蚀精度以及薄膜加厚时侧向生长等。

多层复合膜层制作中,膜层加厚过程增加的微米级的电镀铜、电镀镍、电镀金等膜层厚度不仅会形成应力累积,也会引起带线边缘膜层晶粒粗大和横向过多延伸,明显降低电路图形精度和线条轮廓质量,影响电路性能和长期可靠性。在经过电镀后,镀层表面粗糙度和线条宽度都会因为镀层结晶不精细、线条侧向生长,而导致线条宽度和表面粗糙度发生不可逆的变化,极大影响产品的应用。一方面,图形精度的恶化导致电路的实际加工精度达不到设计需求,影响电路最终性能;另一方面,线条边缘粗大的晶粒导致线条轮廓不平整、存在毛刺,在大功率加载情况下容易造成尖端放电,极大影响产品的实际在轨应用。

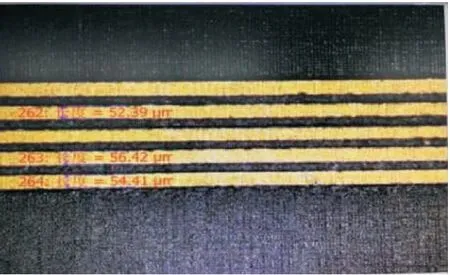

经过对影响图形精度的各个因素进行分析研究,采取了优化镀液体系和电镀参数、优化工艺流程、制版图形补偿和改变图形刻蚀方法等多方面的措施,来解决图形精度差的问题。通过优选晶粒细腻的镀铜溶液体系,调整电镀铜工艺参数,确保镀层间牢固附着的同时,横向延伸最少,确保线条精度。同时,考虑到图形转移、膜层蚀刻和膜层增厚,都会给电路尺寸带来误差。在固定工艺流程后,设计特征尺寸电路进行全流程制作,将成品“特征尺寸”与原始“特征尺寸”数值进行比对,掌握变化趋势与大致尺度。而后根据变化值对设计电路尺寸进行工艺性调整后,再次进行全流程制作。循环改进后,得到了新工艺流程的电路尺寸工艺补偿值范围,提高图形制作精度。图7是100 μm的复合膜层结构的线条图片,线条精度满足设计需求(±15 μm)。

图7 复合膜层结构100 μm线条图片

对于宽度在100 μm以下的细线条,线宽偏差的影响更大,经多次实验,优化工艺流程和图形精细补偿均无法解决线条边缘粗糙的问题。为此采用溅射-一次镀金-二次镀金-激光直写刻蚀图形的新流程,流程如图8所示,完成了细线条图形的制作,可以得到较高的线宽精度,线条图片如图9所示。

图8 激光刻蚀复合膜层结构电路的流程

图9 激光刻蚀50 μm线条图片

3 实践测试结果

对制作出的复合结构膜层进行了膜厚测试,测试数据如表4所列。数据显示,复合膜层结构的总厚度控制在11 μm~14 μm,一致性较好。

表4 复合膜层结构膜厚测试数据

线宽精度测试结果如表5所列。数据显示,复合膜层结构的100 μm线宽精度控制在15 μm以内,一致性较好。

对复合膜层结构电路导体表面电阻进行了测试,数据如表6所列。表面电阻一致性较好,在4 mΩ左右。

表6 复合膜层结构表面电阻测试数据

对复合膜层结构的电路膜层在可靠性试验后进行了附着力测试。首先进行275 ℃、6 h的高温存储后,随后按照-55 ℃±3 ℃~125 ℃±3 ℃,产品在高温或低温下搁置15 min,循环125次,高低温转换时间小于1 min的要求进行温度循环试验。试验完毕使用垂直焊环拉力法测试膜层附着力。测试数据如表7所列。1×1 mm2面积上的焊环拉力值均大于2 kg,附着力满足要求。

表7 复合膜层结构电路附着力测试数据

附着力测试后的放大图如图10所示。

图10 附着力测试后的放大图

对复合膜层结构的镀金层表面进行了键合力测试,Φ25 μm金丝的破坏性键合拉力值>3.5 g,250 μm金带的破坏性键合拉力值>100 g,均满足宇航工程应用要求。

对基于高纯氧化铝基板,采用复合膜层结构的制作的高阻线进行了电流承载力测试,其中1组样件表面膜层状态良好,2组样件表面膜层存在明显划痕。测试结果如表8所列。测试结果表明2组样件在9 A的工作电流均可稳定工作。经分析,复合膜层结构由于增加了导电厚铜层与镍阻挡层,显著增大了电流承载能力,即使高阻线线条表面存在划痕,也不影响工作的可靠性。由于测试条件所限,未能开展更大电流的承载能力测试,但从已有的测试结果推算,复合膜层结构可以承受20 A的电流。

表8 复合膜层结构高阻线电流承载力测试

对基于高介电常数基板制作的复合膜层结构的耐电流能力进行了测试,在0.4 mm的线条上施加5 A的电流,未观察到线条烧断的失效现象。再次证明了复合膜层结构对于提升电流承载能力的有效性。

对复合膜层结构的电路膜层的耐焊性也进行了考察。使用Sn63Pb37焊料、320 ℃的常用手工焊接条件,采用反复搪锡的方式,验证多个复合膜层结构孤立焊盘的耐焊性,试验结果显示,最少的可搪锡次数为18次,证实了此复合膜层结构的高耐焊性。

对上述试验数据和实际工程实践分析,可得到如下认识:

(1)复合膜层结构具有良好的电流承载能力和耐焊性,不仅可以用于较大功率微波电路的制作,在需要多次铅锡焊料返修的电路产品上也能发挥突出优势。

(2)复合膜层结构的膜层附着力与膜层表面的金丝、金带可键合性良好,但因制作中膜层多次电镀,膜层颗粒较大,电路表面和线条边缘轮廓相对粗糙,不适用于对电路线条轮廓有高要求的高频段电路;而对于组装工艺的实施而言,也需要针对其特殊的表面状态,优化焊接和键合工艺参数。

4 结论

文章提出一种提升陶瓷基微波固放电路电流承载能力的工艺途经,通过镍铬、铜、镍、金等不同材料叠加的复合膜层结构,提升电路线条的导热能力,提升固放电路的电流承载力和应用可靠性。测试结果表明,NiCr-Au-Cu-Ni-Au复合膜层结构,高纯氧化铝基板上电路可在9 A电流下稳定工作(表面膜层完整和表面存在明显划伤结果相同),高介电常数基板上0.4 mm线条可耐受5 A电流,复合膜层结构的膜厚控制范围、线宽精度、焊环拉力、Φ25 μm金丝的破坏性键合拉力与250 μm金带的破坏性键合拉力等,均满足宇航工程应用要求。膜层结构中导电厚铜层与镍阻挡层的加入,不仅提升了电路的导电性与导热性,提高了固放电路的电流承载力,最终保证了微波固放电路的应用可靠性,为提升星载微波固放电路的电流承载能力提供了一个有效途径。