新型再生长沟道GaN基准垂直MOSFET仿真研究

李萌迪,祝杰杰,侯 斌,张 鹏,杨 凌,贾富春,常青原

(西安电子科技大学,西安 710071)

0 引言

近些年随着生产力的迅速发展与全球能源需求的持续增长,导致能源方面的问题日益凸显。电能是受到最广泛应用的能源之一,但电能在转化与运用过程中会产生部分的无用功从而不可避免地出现能量的损耗,导致电能的转化效率较低从而造成了能源的浪费。电力控制和电能转换过程中最核心部分即为电力电子技术,而电力电子器件是其最重要、最基础、最核心的元器件,因此对于电力电子器件的相关研究具有非常重大的意义[1-2]。目前电力电子器件所采用的材料主要为Si,其具有价格低廉、工艺成熟等特点。而GaN作为近几十年发展起来的第三代宽禁带半导体材料(禁带宽度为3.4 eV),相比于Si,其具备更高的击穿场强(3.3 MV/cm)与更大的电子饱和速度(2.7×107cm/s)等优势,因此GaN拥有更广泛的应用领域和更大的市场潜力[3-4]。

GaN基准垂直金属氧化物半导体场效应晶体管(metal oxide semiconductor field effect transistor,MOSFET)器件是一种电压型控制器件,由于其具有高输入阻抗、驱动功率低、开关速率快以及对表面态陷阱不太敏感等优点,从而成为目前研究的热点[5]。但由于GaN基准垂直MOSFET导通时反型沟道载流子的迁移率较低,造成器件工作时导通电阻与损耗较大[6]。为了解决该问题,UCSB的Gupta等[7]提出了再生长沟道GaN MOSFET结构,其在传统GaN MOSFET结构的基础上,通过金属有机物化学气相沉积在原来n-p-n沟槽结构上重新生长一层非故意掺杂(unintentional doping,UID)GaN夹层,制备了更高电子迁移率的再生长沟道层,使得沟道载流子的迁移率从7~10 cm2/V·s提高至25~40 cm2/V·s,导通电阻从9.3 mΩ·cm2大幅下降至3.8 mΩ·cm2。

该再生长沟道GaN MOSFET结构主要是对器件的沟道区域进行结构创新,而其他区域如源极区、漏极区与漂移区还具有进一步优化的空间。文章主要对再生长沟道GaN MOSFET结构与优势进行介绍,通过仿真对这种结构的电学特性进行验证,并与常规器件进行对比分析;但该结构在导通时,器件内部载流子在除沟道外的其他区域还存在一些不合理的分布现象,因此针对该结构进行进一步的改进,主要对器件源极区域与漂移区域的载流子分布进行了合理优化,旨在不影响器件击穿特性的前提下进一步降低其导通电阻的大小,从而减小该器件工作时的功率损耗。

1 再生长沟道GaN基准垂直MOSFET

1.1 GaN材料简介

以Si为代表的第一代半导体,尽管具备价格低廉、工艺成熟的特点,但其作为单质半导体,不仅禁带宽度较窄,而且材料结构单一,只能通过掺杂浓度来改变材料性能,应用灵活性和广泛性受到了极大的限制。以GaAs、InP为代表的第二代半导体[8],作为Ⅲ-Ⅴ族化合物半导体,可以通过调节其组分形成异质结,在结界面处形成高迁移率的二维电子气(two-dimensional electron gas,2DEG),从而在高频方面取得广泛应用;然而禁带宽度仍比较窄,耐压等级受到限制,不适合制作高压大功率器件。

GaN材料作为新一代半导体材料,具备出色的材料物理及电学性质。当GaN面向高频应用时,材料通过自发极化和压电极化,会在GaN/AlGaN异质结界面感生出高载流子迁移率(2 000 cm2/V·s)与浓度(>1×1013cm-2)的2DEG,使得器件具有极低的导通电阻和极短的电子渡越时间,从而使器件在高频方面展现出优良的性能[9-10];当GaN面向高压大功率应用时,能够承受更高的击穿场强(3.3 MV/cm),使得制备的器件具有更高的击穿电压,并且在同等的耐压要求下,GaN所制备的器件具备更低的导通电阻,从而GaN材料在高压大功率电力电子领域也具有很大的潜力[11-12]。

1.2 GaN基准垂直MOSFET导通电阻组成

对于GaN基准垂直MOSFET器件来说,导通电阻是衡量该器件综合性能最重要的参数之一,导通电阻的大小决定了该器件在工作时所产生的功率损耗。对于一个理想的GaN MOSFET器件,其导通电阻越小那么该器件在工作时的功耗往往越低,因此在设计GaN基准垂直MOSFET器件时应尽可能的减小其导通电阻。图1为该器件的导通电阻组成图,可以看出总导通电阻Ron主要由5个部分构成,分别是源极区体电阻Rs,沟道电阻Rch,漂移区总电阻Rdri(包括积累层电阻Ra与漂移区体电阻Rdrift),漏极区体电阻Rd,以及器件金属-半导体接触总电阻Rc(包括源极接触电阻Rcs与漏极接触电阻Rcd)。

图1 GaN基准垂直MOSFET器件导通电阻组成图

其中,金属-半导体接触电阻Rc(Rcs+Rcd)可以通过提高N型GaN材料掺杂浓度或高温快速退火的方式来降低其阻值大小; 源极区体电阻Rs与漏极区体电阻Rd可以通过适当提高其各自的掺杂浓度来使得其体电阻得到有效地降低;沟道电阻Rch与漂移区总电阻Rdri相对来说在MOSFET器件总导通电阻Ron中的占比最大,其中沟道电阻在总导通电阻中占比往往会超过一半。

1.3 再生长沟道GaN基准垂直MOSFET结构优势

对于GaN基准垂直MOSFET器件来说,其沟道载流子迁移率过低的原因主要有[7]:

1)栅槽是通过电感耦合等离子体设备进行刻蚀形成,因此会产生大量不可控的刻蚀损伤,从而这些刻蚀损伤会降低沟道处载流子的迁移率;并且由于残余Si的引入会增加正电荷,可能导致更低的击穿电压和阈值电压;

2)栅极沟槽处刻蚀造成半导体一侧界面的不平整度增大,从而引起器件沟道处界面散射的增加,使得沟道处载流子迁移率的下降;

3)P+GaN基区内部电离后的Mg离子对沟道载流子的离子散射较大。

因此对于GaN基准垂直MOSFET器件来说,要想降低其导通电阻最有效的方法便是提高器件反型沟道载流子的迁移率以降低其沟道电阻。

常规GaN MOSFET器件其在栅槽刻蚀后,栅介质直接沉积在栅槽处,器件的反型沟道形成于栅介质与半导体(P型GaN基区)界面半导体一侧处;而对于再生长沟道GaN基准垂直MOSFET结构,如图2所示,在栅槽刻蚀后,会在其上方利用金属有机化学气相沉积MOCVD重新生长一层非故意掺杂UID-GaN,接着在UID-GaN上沉积一层原位的栅介质,该器件的反型沟道形成于原位栅介质与UID-GaN界面靠近UID-GaN一侧,该非故意掺杂UID-GaN即为器件的再生长沟道层。

图2 再生长沟道GaN基准垂直MOSFET结构示意图

再生长沟道GaN基准垂直MOSFET结构可以有效提高器件沟道迁移率的原因主要有[13-16]:

1)由于非故意掺杂UID-GaN层的存在,载流子可以通过这层再生长沟道层进行传输,而该层并没有经过刻蚀工艺,栅介质与半导体界面更为平整,大大降低了界面不平整散射效应;

2)再生长沟道层的存在使得器件沟道远离P+GaN层,并且该再生长沟道层并没有进行掺杂,从而有效减小了电离杂质对沟道载流子的影响。适当增加UID-GaN层的厚度可能有助于进一步降低导通电阻,这样可以使沟道进一步远离P+GaN层,从而进一步降低电离杂质散射对沟道载流子输运的影响。

2 再生长沟道GaN基准垂直MOSFET器件仿真

2.1 结构仿真

本节借助仿真软件对再生长沟道GaN基准垂直MOSFET器件进行研究,并与常规结构的电学特性进行对比。图3与图4分别为常规GaN基准垂直MOSFET(简称为常规结构,w/o UID-GaN)与再生长沟道GaN基准垂直MOSFET(简称为再生长沟道结构,w UID-GaN)的仿真结构图。从图中可以看到两者的区别仅仅在栅极与半导体之间是否有UID-GaN再生长沟道层,其他结构参数均为一致,图中红框所框选的区域为栅槽处的局部放大。

图3 常规GaN基准垂直MOSFET仿真结构图

图4 再生长沟道GaN基准垂直MOSFET仿真结构图

该UID-GaN再生长沟道层的厚度定义为50 nm,背景载流子浓度为1×1016cm-3。

2.2 转移特性与输出特性仿真

图5为两种结构转移特性对比图,常规结构阈值电压为2.97 V,再生长沟道结构阈值电压为2.25 V,这是由于再生长沟道的引入使得器件沟道处更容易反型,从而导致阈值电压的下降。

图5 常规结构与再生长沟道结构转移特性对比图

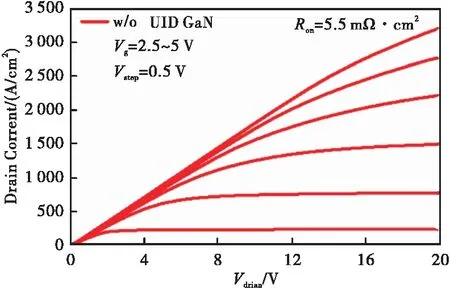

图6和图7为常规结构与再生长沟道结构的输出特性图,可以看出常规结构的导通电阻为6.1 mΩ·cm2,而再生长沟道结构的导通电阻为5.5 mΩ·cm2,验证了再生长沟道结构由于提高器件反型时沟道载流子的迁移率,从而降低器件总导通电阻。

图6 常规结构输出特性图

图7 再生长沟道结构输出特性图

2.3 击穿特性仿真

图8为两种结构的击穿特性对比图,器件的击穿电压定义为当漏电流密度达到50 mA/cm2时所对应的漏极电压Vdrain,在图中以红色虚线标注。

图8 常规结构与再生长沟道结构击穿特性对比图

常规结构的击穿电压为1 078 V,再生长沟道结构的击穿电压为1 103 V,因此可以证明再生长沟道的引入不会引起GaN MOSFET器件击穿特性的恶化。这是因为对于GaN MOSFET器件来说,其击穿电压主要受漂移区域厚度和掺杂的影响,而文章中的仿真结构中漂移区厚度为4 μm,远大于再生长沟道层UID-GaN的厚度50 nm,因此UID-GaN的引入不会影响GaN MOSFET器件的击穿特性。

3 新型再生长沟道GaN基准垂直MOSFET

从上一节的仿真数据可以看出,对于GaN基准垂直MOSFET来说,再生长沟道层的引入在不影响击穿特性的前提下,有效减小了器件的导通电阻,同时,器件的阈值电压也有所下降,但其导通时内部的载流子在沟道外其他区域还存在部分不合理的分布现象。该器件导通时的电流路径可以分为4个部分,从上至下分别为源极区域、沟道区域、漂移区域与漏极区域,如图9所示。

图9 再生长沟道GaN基准垂直MOSFET电流导通路径图

由于该器件仿真结构中n+GaN漏极区的掺杂浓度高达1×1020cm-3,因此漏极区域导通电阻在器件总导通电阻中占比极低,故对该区域的载流子分布暂不进行优化,文章主要是针对器件的源极区与漂移区域进行载流子的分布优化。

3.1 载流子分布优化:源极区域

再生长沟道GaN基准垂直MOSFET在制备过程中,要在栅槽区域进行再生长沟道层沉积,该过程需要在600 ℃以上的高温下进行。考虑到如果采用后栅工艺,即先对源漏极电极进行制作,那么GaN再生长时的高温会对源漏极欧姆金属造成负面影响,如欧姆接触电阻退化、出现金属爆点等。因此,该器件在源漏极金属蒸发前需要先进行再生长沟道层沉积,同时为了防止该沟道层被氧化,再生长结束后需进行栅介质Al2O3的沉积,但这样会导致后续在源极蒸发时源极金属帽子下方有一层Al2O3,如图10所示,红框为源极区域的局部放大图;图11为源极区域载流子分布优化后示意图,即通过对源电极金属帽下方与N+GaN源极区之间的Al2O3进行F基刻蚀,使得源极金属帽子直接搭在N+GaN上方与半导体材料相接。

图10 源极区域优化前结构图

图11 源极区域优化后结构图

将源极区域载流子分布优化前,未进行源极金属帽子下方Al2O3刻蚀的器件称作w/o Al2O3etch;而对源极金属帽子下方Al2O3刻蚀优化后的器件称作w Al2O3etch,图12为两种结构导通时总电流密度图。从图中可以看出,w Al2O3etch器件其源极区域的电流导通路径相对于w/o Al2O3etch得到了有效的缩短。对于该仿真的新型再生长沟道GaN MOSFET来说,器件源极区域的掺杂浓度是固定不变的,从而源极区域可以等效为一个电阻,其阻值大小随电流导通路径的长短是线性变化的,因此w Al2O3etch器件源极区域的导通电阻得到了有效的降低。

图12 源极区域优化前后导通时总电流密度对比图

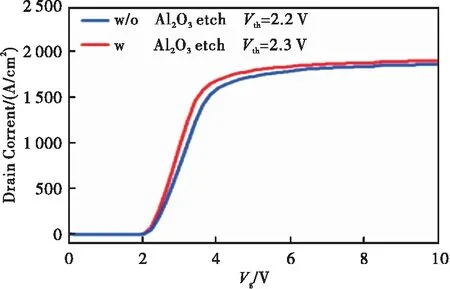

从图13、图14两种的转移与输出特性对比图可以看出,源极区域优化后对器件的阈值电压影响较小,其中优化前w/o Al2O3etch器件的阈值电压为2.2 V,而优化后w Al2O3etch器件的阈值电压为2.3 V。但将源极区域优化后使得器件的导通电阻大小得到了有效的降低,其中w/o Al2O3etch器件的导通电阻为2.4 mΩ·cm2,而w Al2O3etch器件的导通电阻下降至2.1 mΩ·cm2。

图13 源极区域优化前后转移特性对比图

图14 源极区域优化前后输出特性对比图

为了验证源极金属帽子下方Al2O3的刻蚀是否会对器件的击穿特性产生影响,对w/o Al2O3etch与w Al2O3etch的击穿特性进行仿真,图15为两种结构的击穿特性对比图,可以看出w/o Al2O3etch与w Al2O3etch的击穿电压相等都为1 059 V。这是因为对于再生长沟道GaN MOSFET来说,器件处于阻断状态下时主要靠P型基区与N型漂移区组成的PN结来耐压,因此对源极金属帽子下方Al2O3进行刻蚀后并不会对器件的击穿特性造成影响。

图15 源极区域优化前后击穿特性对比图

3.2 载流子分布优化:漂移区域

当再生长沟道GaN基准垂直MOSFET器件工作时,电子从源极Source区通过反型沟道后会进入到N-GaN漂移区内,但在带正电的栅电极Gate对电子的吸引作用下,导致栅电极下方产生电流拥挤现象,并会在其下方形成一层载流子的积累层,由于这个积累层的存在会造成MOSFET器件漂移区对应导通电阻的增加。图16为该器件漂移区域载流子分布优化前结构示意图,图17为导通时的总电流密度分布图,从中可以看出载流子在进入到漂移区后,在栅极下方产生了明显的拥挤现象。

图16 漂移区域优化前结构图

图17 漂移区域优化前导通时总电流密度图

通过在栅极下方插入一层载流子分布层(current distribution layer,CDL),该层与P+GaN层相连接,并且掺杂浓度略高于漂移区的掺杂浓度。在本仿真结构中,漂移区的掺杂浓度为5×1015cm-3,厚度为4 μm;CDL的掺杂浓度为1×1016cm-3,厚度为0.5 μm。载流子分布层CDL的存在使得漂移区内栅极下方的电子横向延伸到器件的平面方向,漂移区内载流子分布更均匀,从而器件漂移区对应的导通电阻下降。图18为漂移区域载流子分布优化后结构示意图,图19为导通时的总电流密度分布图,可以看出优化后的结构中漂移区内栅极下方载流子的分布更为均匀。

图18 漂移区域优化后结构图

图19 漂移区域优化后导通时总电流密度图

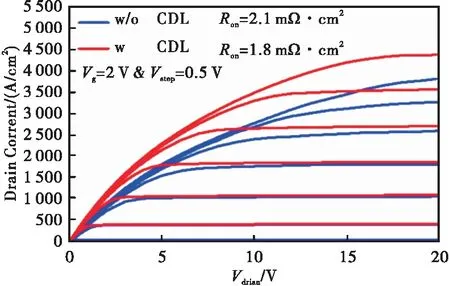

将漂移区域载流子分布优化前,不具有载流子分布层CDL的器件称作w/o CDL;而将优化后具有载流子分布层CDL的器件称作w CDL。图20为两种器件转移特性的对比图,从中可以看出,载流子分布层CDL的插入对器件转移特性几乎没有影响,两种器件的阈值电压均为2.3 V。

图20 漂移区域优化前后转移特性对比图

图21为优化前后两种器件输出特性的对比图,从中可以看出具有载流子分布层CDL的器件具有更低的导通电阻以及更高的饱和输出电流,其中w/o CDL器件的导通电阻为2.1 mΩ·cm2,而w CDL器件的导通电阻下降至1.8 mΩ·cm2。

图21 漂移区域优化前后输出特性对比图

为了验证栅极下方载流子分布层CDL的加入是否会对器件的击穿特性产生影响,对两种器件的击穿特性也进行了仿真。图22为优化前后两种结构的击穿特性对比图。

图22 漂移区域优化前后击穿特性对比图

从图22中可以看出,漂移区优化前结构w/o CDL的击穿电压为1 059 V,漂移区优化后结构w CDL的击穿电压为1 053 V。因此可以证明w CDL结构在不影响再生长沟道结构击穿特性的前提下,有效提高了器件的饱和输出电流并降低了器件的导通电阻。

4 结论

文章首先对GaN材料作以介绍,并对再生长沟道GaN基准垂直MOSFET器件的结构优势进行了分析;然后利用Silvaco TCAD软件对该结构的电学特性进行仿真验证,并与常规结构作以对比,通过仿真结果可以证明再生长沟道层UID-GaN的引入在不影响击穿特性的前提下,有效减小了器件的导通电阻。但该再生长沟道结构在导通时,器件内部载流子在除沟道外的其他区域还存在一些不合理的分布现象。因此文章在再生长沟道GaN基准垂直MOSFET的基础上进行了结构改进,主要针对器件在源极区域与漂移区域的载流子分布进行了合理优化。最终设计出了阈值电压为2.3 V的新型再生长沟道GaN基准垂直MOSFET,器件的导通电阻低至1.8 mΩ·cm2,击穿电压高达1 053 V。