高精度电流采样电路设计*

张治东,刘兴辉,阮 昊,尹飞飞,赵皆辉,郜嘉铭

(1.辽宁大学 物理学院,辽宁 沈阳 110036;2.江苏集萃智能集成电路研究所有限公司,江苏 无锡 214028)

0 引 言

对于直流刷式电机来说,采样并检测到电流信息可以确定负载条件的变化,也可以用来限制启动电流或者失速电流。因此,一种高精度的电流采样电路以及相对应的电流调节功能对于电机驱动芯片来说十分重要。传统上,H桥电机驱动芯片的电流采样是通过在外部并联电阻器接地从而对电流进行限制。产生分流器检测电机的电压降,与芯片内部或者外部的参考电压进行比较[1]。这种方式采样电流的精度十分依赖功率电阻的阻值大小,很难保证较高的精度[2,3]。因此,在电阻采样方法的基础上,本文提出了一种带有特殊电流镜架构的电压钳位电流采样电路。

1 一种电机驱动电路的新型电流采样方法

1.1 电流采样系统组成

本文提出的电流采样电路在芯片内部集成了一个电流采样电路模块用来取代传统的并联电阻器采样电流的方法。图1给出了该电流采样系统的具体组成结构。

图1 电流采样系统的电路组成

1.2 电流采样电路的结构与原理

如图2所示,电流镜架构包括采样管MNDRV以及镜像管MNsense,输入电流由采样管的漏极流向采样管的源极;镜像管用来镜像功率管的漏极电流,并以一定的比例将该电流缩小,当栅极电压达到预设电压值时,采样管与镜像管能够线性导通,而不需要管子处于完全饱和状态(处于线性区即可),便可以对采样的电流进行比例镜像。镜像管和采样管的漏极分别接到误差放大器的正负两端,2 个管子的源极接地。

图2 电流采样电路具体结构

理想情况下,MOS管处于线性区时,漏极电流为

因此,若采样管MNDRV与镜像管MNsense的VGS与VDS相同,则其镜像电流与采样电流的比例就会与MNDRV与MNsense的宽长比呈线性,但由于采样管与镜像管的漏极电位在实际情况下很难做到完全相同,因此,本文采用高精度误差放大器将2个管子的漏端电压钳位到近似相同的电位。

传统的误差放大器钳位电流镜架构中常使用1 个MOS管作为镜像管,在本文中采用将多个镜像管串联、采样管并联的连接方式。因为电流需要镜像的比例较大,为了版图的匹配性更好,将采样管与镜像管采用相同的单位栅宽以及相同的栅长,为此将具有相同单位栅宽以及相同栅长的NMOS管进行并联以增大栅宽作为采样管,将具有相同单位栅宽以及相同栅长的NMOS管进行串联以增大栅长作为镜像管,则镜像管整体的栅长Lsense为

式中 Lsense1~Lsensen为单个镜像管的栅长。当MOS 管栅漏之间的电压增大时,实际的反型层沟道长度会逐渐减小,会对处于饱和区时的镜像管的漏极电流iD有一定的影响,如式(3)所示

式中 μ0为镜像管的沟道表面电子迁移率;Cox为单位面积栅氧层电容;VGS为镜像管的栅源电压;VTH为镜像管的阈值电压;VDS为镜像管的漏源电压;λ 为镜像管的沟道长度调制系数,表示给定的VDS增量所引起的沟道长度的相对变化量,因此对于较长的沟道,沟道长度调制系数较小。在实现与采样管具有相同栅长从而满足良好的版图匹配性的前提下,采用这种串联镜像管的方式增大了镜像管整体的栅长,从而能够有效地抑制沟道长度调制效应,将大大提高电流镜的精度,同时也将增大输出阻抗和电源抑制比。这种连接方式尽管会带来面积上的损耗,但相对于传统的外部电阻器采样方式,依旧能够节省大量的面积。

通过误差放大器采用负反馈的接法将采样管与镜像管的漏极钳位到同一电位使2个MOS管的漏极电压相同,最后误差放大器的输出连接到输出管MN1 的栅极,MN1 的源极接镜像管MNsense的漏极,采样电流即从输出管MN1 的漏极输出到共源共栅电流镜中。

基于以上的考虑通过将4 个采样管MNDRV并联并将3个镜像管MNsense串联使其电流比例为1:K,使得镜像管镜像到的理想电流值为

式中 Isense为通过电流镜镜像后的电流,IDRV为低侧功率管的待采样电压,K 为电流镜的镜像比例,本文中K 定为1 000。

共源共栅电流镜由4 个PMOS 管组成,采样电流由输出管MN1的漏极连接到MP3 的源极同时连接到MP1 与MP2的栅极,其中MP3、MP4 为cascode 级,MP1、MP2 为电流镜,将采样电流镜像到MP2 的漏极即MP4 的漏极,输入到采样电阻Rsense中,最后使用标准模数转换器将负载电流作为Rsense电阻器两端的电压进行测量,默认情况下电流镜的比例为1:1,若所需采样的电流值过小,可适当调整电流镜的比例来降低对采样电阻的要求。若电机驱动芯片为双相或三相结构,则当两相或者三相的低侧MOS功率管同时开启,通过本文中的采样电路可将两路或者三路的采样电流通过共源共栅电流镜相加输入到采样电阻Rsense中。

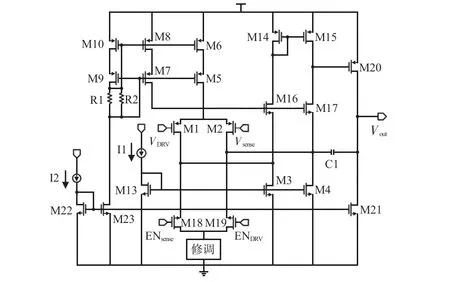

1.3 误差放大器和修调模块

为了将镜像管MNsense与采样管MNDRV的漏极电压以较高的精度钳位到同一电位,需要误差放大器具有低失调电压、高增益、较高的电源抑制比、较大的共模输入范围等性能[4,5]。本文中的误差放大器结构如图3 所示,采用了折叠共源共栅—共源的两级放大器结构,采样管MNDRV的电压与镜像管MNsense的漏极电压分别输入到误差放大器第一级的共源共栅放大器中M1与M2管的栅极,M5、M6、M7、M8、M9、M10、R1、R2构成了低压共源共栅电流镜,由电流源I2为运放提供偏置电流,增大运放的电源抑制比,同时这种结构所消耗的电压相比于非低压的结构减少了一个阈值电压。I2也为第二级运放的M21 提供了偏置电流作负载。I1为第一级的M3、M4 提供了偏置电流作为共源共栅管M16、M17的电流镜,且为了保证M3、M4 的直流电流恒不为0,在本文中I1的电流值为I2的1.5 倍。第一级的输出电压从M15的漏极流出输入到M20 的栅级,并从M20 的漏极得到最终的输出电压Vout。

图3 电压钳位运算放大器

采用了折叠共源共栅作为第一级保证了运放的增益同时采用了共源级作为第二级进一步增大了运放的增益,整体增益为

由于第一级为折叠共源共栅结构,输出阻抗Rout1较大,具体为

因此,主极点在第一级的输出端,次主极点在第二级的输出端,为了保证运放的稳定性,在第一级的输出端与第二级的输出端之间加入补偿电容C1,从而将主极点推向了更低频处,增大了主次极点之间的距离,此时的主极点p1和次主极点p2分别为

但是,由于补偿电容C1会使第二级的输入与输出短接从而产生一个右半平面的零点将会影响电路稳定性,需要增加调零电阻来消去此零点。在本文中将共源共栅管M17的rds作为调零电阻,采用合适的尺寸从而将零点抵消。

在实际中,由于制造工艺的偏差,标称相同的器件都存在有限的不匹配,从而会产生直流失调,即当VDRV与Vsense相等时,Vout并不等于零而是会产生一个失调电压VOS,in

式中 ΔID为由于失调产生的漏极失调电流,因此为了抑制由于该失调电流对于误差放大器的影响,本文设计了一个修调模块,具体电路如图4 所示。该模块由8 个NMOS管组成,其中MN1 -MN4 的栅极分别由EN1 -EN4控制,MN5 -MN8的栅极由偏置电压Vbias进行输入从而产生四路偏置电流,通过4个使能信号控制MN1 -MN4 的导通状态,从而产生不同的偏置电流。再通过ENsense与ENDRV两个使能信号控制为哪一支路注入额外的偏置电流,从而实现对失调电压的补偿。

图4 修调模块

2 仿真结果与分析

采用海力士0.18 μm 的BCD 工艺进行电流采样电路设计,并采用Spectre工具进行功能与性能的仿真[6]。电路整体的供电电压为24 V,误差放大器的供电电压为电机驱动芯片中低压差线性稳压器(low dropout regulator,LDO)模块提供的5 V 电压,当驱动控制信号使驱动管导通,对底边驱动管的电流进行采样,采样电流的大小由电机外部负载大小决定,如图5 所示为不同待采样电流下的仿真结果。

图5 IDRV由200 mA~1 A变化Isense的值

根据电流采样误差公式δ =ΔI/IDRV×100%。可得采样电流在0.1~1 A范围内变化时的具体采样精度值,具体如表1所示。当IDRV为400 mA 时,电流采样误差达到了0.81,相比于其他的电路结构具有较大优势,这是因为本设计中采用了特殊的电流镜架构以及较高增益的误差放大器所致。表2为本文与其他电流采样电路的采样方式以及采样误差的对比。

表1 电流采样精度

表2 电流采样精度对比

图6(a)所示为误差放大器的环路特性曲线,运放的环路增益为100 dB 左右,相位裕度为59.3°。该运放的目的是为了将采样管与镜像管的漏端钳位,足够的增益与相位裕度保证了钳位的精度以及系统的稳定性。图6(b)所示为误差放大器的电源抑制比(power supply rejection ratio,PSRR),因为电流采样电路主要应用在电机驱动芯片中,因此对于速度的要求较低,在低频下PSRR 最好情况可以得到121 dB左右,在10 kHz下最差的PSRR为73 dB左右,满足运放对于电源小信号的抑制要求。

图6 增益与相位裕度及电源抑制比

3 结 论

本文提出了一种应用于H 桥电机驱动芯片的高精度电流采样电路,通过特殊的电流镜结构以及高增益高电源抑制比的误差放大器实现了较高的精度,最好可以达到99.19%,相比于传统的电机驱动芯片内的电流采样方法,本文的电流采样电路可以节省较大的面积,同时适用于双相以及三相的直流电机驱动芯片,能够有效地监测芯片的电流大小。