一种低噪声C 类LC 压控振荡器的设计

葛士曾, 陈德媛, 张 瑛

(南京邮电大学 集成电路科学与工程学院, 江苏 南京 210023)

0 引 言

在无线通信和测量等领域[1-2],锁相环电路是一种反馈系统,LC 压控振荡器和环形压控振荡器[3]在锁相环电路中普遍应用,将表现出负阻性质的有源器件与LC 谐振电路相结合,从而输出等幅振荡信号。这是由于它的相位噪声性能在高频信号表现较好。

文献[4]采用双VCO 架构增加总的频率调谐范围,并通过降噪的LDO 稳压器降低相位噪声。文献[5]使用电容反馈回路和衬底偏置技术,设计了一种正交压控振荡器,通过增加输出振荡信号的摆幅来降低相位噪声。文献[6]提出了一种自动频率校准器(AFC),通过调节控制电压从而选择最合适的子带来减小VCO 电路的增益,达到降低电路相位噪声的目的。为了优化VCO 电路的相位噪声表现,本文设计了一种低噪声C 类LC 压控振荡器。

1 LC 振荡器

LC 振荡器由负阻结构和LC 谐振腔组成,如图1 所示。其中L和C分别是LC 振荡器的等效电感和等效电容。为了使LC 振荡器保持正常的工作状态,维持等幅振荡,设计一个负阻结构[7-8]抵消寄生电阻Rp的影响。

图1 LC 振荡器模型

在设计上采用互补式交叉耦合对管的构造,通过分析该构造的小信号等效模型[9],得出负阻的公式:

式中:gmN和gmP分别为NMOS 和PMOS 管的跨导。

2 电路设计

本文设计基于40 nm CMOS 工艺,采用互补型交叉耦合全差分振荡器电路[10],其最大输出频率和相位噪声性能介于NMOS 和PMOS 交叉耦合振荡器电路之间[11],通过采用共模反馈电路对交叉耦合PMOS 对管进行偏置可以解决该问题。LC-VCO 电路结构如图2 所示。

在LC-VCO 电路中,通过隔离直流信号的电容将交叉耦合PMOS 对管M1和M2、NMOS 对管M3和M4之间的栅极和漏极相连接从而形成交流耦合,可以使得LCVCO 电路产生的信号传输到交叉耦合对管的栅极。在LC-VCO 电路平稳振荡时,共模信号反馈环路通过负反馈将共模信号Vcm经过电感的中心抽头与参考信号Vref比较,使得共模电压Vcm保持在参考电压Vref范围内,并且可以根据给定的LC-VCO 电路电流产生足够低的偏置电压Vb,通过电阻和隔离直流信号的电容形成低通滤波网络来偏置交叉耦合PMOS 对管M1和M2,使交叉耦合PMOS 对管M1和M2在饱和区内工作,来保证振荡器C 类振荡,使得饱和区的交叉耦合PMOS 对管对整体噪声的贡献变小。而且由于LC-VCO 电路的下方通过电流镜对NMOS 管M3和M4进行偏置,为电路提供电流,从而避免了传统的尾电流管限制,使得LC-VCO 电路输出振幅最大化,改善了LC-VCO 电路的相位噪声。

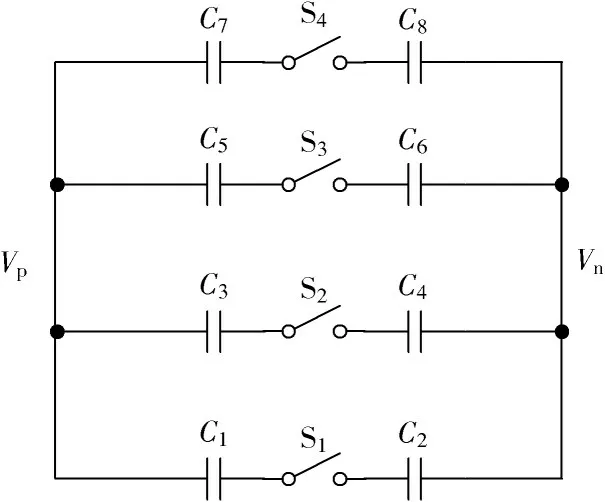

2.1 开关电容阵列

本文设计中使用4 组开关电容完成LC-VCO 电路频率的粗调谐。如图3 所示,通过4 个开关S1、S2、S3、S4控制4 组具有不同容值的电容接入LC-VCO 电路,从而取得16 条不同振荡频率范围的子频段。

图3 开关电容阵列

本文设计中的开关由3 个NMOS 管来完成,开关电容电路如图4 所示。S1处于高电平的情况下,NMOS 管M5、M6、M7均闭合,电容C1、C2连接到LC-VCO 电路中。

图4 开关电容电路

为了保证16 个子频段相邻之间能够相互重叠,达到50%的重叠率,而且完成较大范围的频率调谐,开关电容C1~C8需要设计合适的容值。

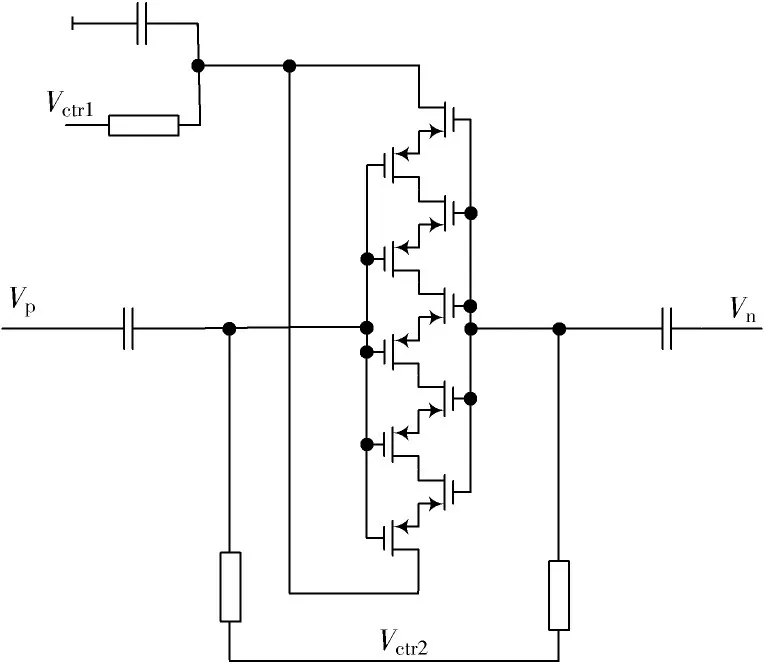

2.2 差分可变电容的设计

电路中的差分可变电容的设计如图5 所示,通过Vctr1和Vctr2两个差分控制电压来调节可变电容的容值大小。

图5 差分可变电容管

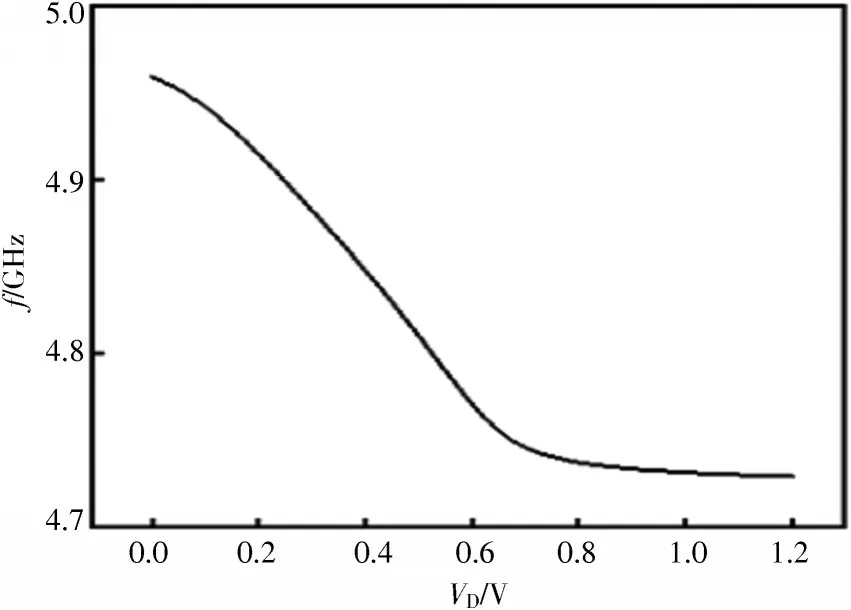

差分可变电容随差模信号VD(Vctr1-Vctr2)变化的C-VD曲线仿真结果如图6 所示,差模信号在0~0.6 V 范围内时,差分可变电容的电容值在22.5~171.2 fF 范围内变化,并且曲线具有很好的线性度。

图6 可变电容管的C-VD变化曲线

图7 为LC-VCO 电路输出信号频率随差模信号VD变化的曲线。由图7 可知,差模信号VD在0~0.6 V 范围内,频率变化曲线线性度较好。

图7 LC-VCO 电路的f-VD曲线

对于锁相环电路整体的设计来说,LC-VCO 电路的差分控制电压Vctr1在0.6~0.9 V,Vctr2在0.3~0.6 V 时,使差模信号VD在0~0.6 V 范围内,从而使电荷泵取得较好的线性度,电流匹配度较好,减少了输出时钟抖动,同时也降低了锁相环的噪声。

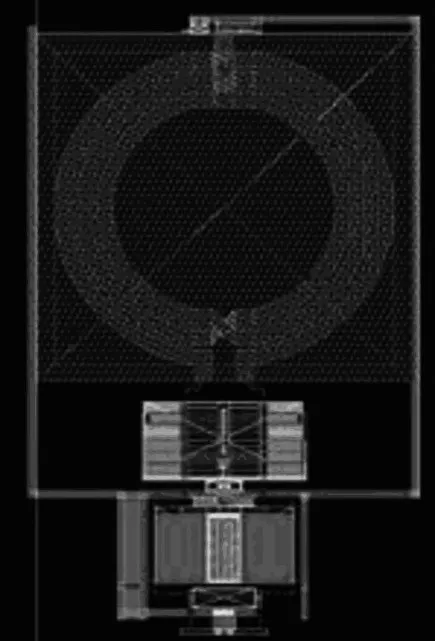

3 版图设计及仿真结果

本文中的LC-VCO 电路采用40 nm 工艺设计并绘制了电路版图,如图8 所示。由于电路采用的是全差分式的构造,所以在布局设计时采用了对称结构,从而保证非理想的情况下,各个元件引入的寄生电容近似相等。电路版图核心面积为:144 μm×250 μm=0.036 mm2。

图8 LC-VCO 核心电路版图

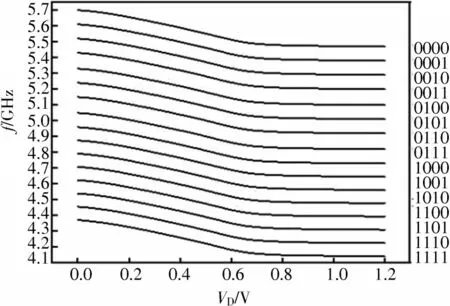

当差分控制电压Vctr1在0.6~0.9 V,Vctr2在0.3~0.6 V内,控制S1、S2、S3、S4四个开关的开闭,得到16 个子频段。每个子频段在差分控制电压Vctr1和Vctr2控制下的输出时钟频率如图9 所示。根据图9 可知:各个子频段的输出频率连续变化,并且相邻子频段之间有重叠,重叠率达到了50%,可以实现子频段之间的连续变化;差模信号VD在0~0.6 V 范围内,每个子频段的线性度都很好,使LC-VCO 电路保持确定的增益。

图9 LC-VCO 电路频带时钟频率图

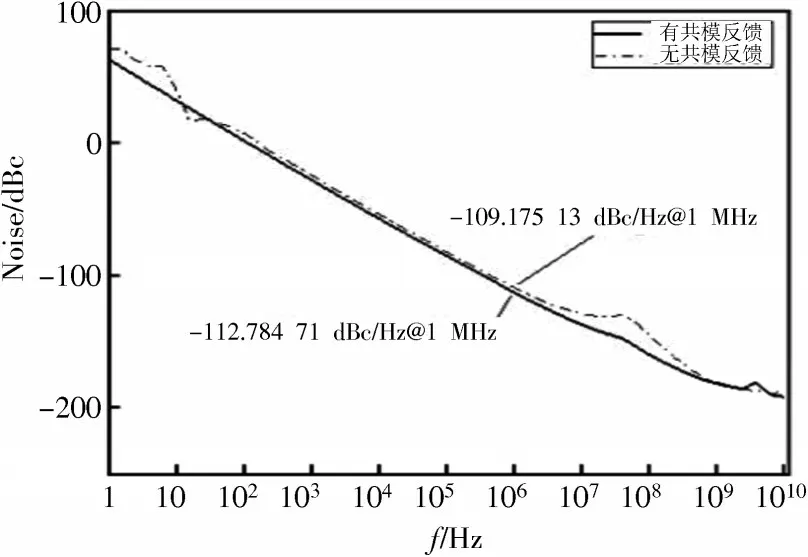

LC-VCO 电路中心频带处相位噪声的比较如图10所示。根据图10 可知,采用共模反馈电路偏置的LCVCO 电路在中心频率频偏1 MHz 时对应的相位噪声为-112.8 dBc/Hz,而未采用共模反馈电路偏置的LC-VCO电路的相位噪声为-109.2 dBc/Hz,相比之下,采用了共模反馈电路的相位噪声减小了3.6 dBc/Hz。

图10 LC-VCO 电路中心频带相位噪声比较

LC-VCO 电路有相位噪声、调频范围和功耗等性能指标。通过品质因数(FOM)[12]可以反映出LC-VCO 电路整体的性能表现,其定义为:

式中:f0为中心频率;LΔf为在信号频率频偏Δf处的相位噪声;PDC为直流功耗;参考功率P的值为1 mW。

本文设计的LC-VCO 电路与其他文献方法中的LCVCO 电路的性能比较如表1 所示。本文设计的LC-VCO电路在相位噪声方面表现更为突出,同时调谐范围和功耗也具有很好的性能表现。本文设计的LC-VCO 电路的FOM 值为-183 dBc/Hz,与其他文献方法的FOM 指标相比,也具有一定的优势。

4 结 论

基于40 nm COMS 工艺设计一种宽频带、低噪声的LC-VCO 电路,运用4 个开关对电容阵列改变电路中所连接固定电容的电容值,从而对输出时钟频率进行调节,最终实现输出时钟频率能够在16 个子频段内变换;同时通过差分控制电压改变差分电压变容管的电容值,从而在子频段内进行频率调节。通过采用共模反馈电路对交叉耦合PMOS 对管进行偏置,减小电路的相位噪声,从而实现在0~0.6 V 的差分电压控制下频率输出。

注:本文通讯作者为陈德媛。