PCB设计中阻抗匹配的信号改善方法

赵 号 邓磊刚 吕圣泽

(西安航空计算技术研究所,陕西 西安 710600)

0 引言

印制电路板(printed circuit board,PCB)是互连电子元器件系统的物理载体,其设计的好坏直接关系到最终生产出来的电子产品能否正常工作。随着科学技术的不断发展,大数据、云计算等新科技都依赖高速数据的传输来实现,传输信号的频率也从兆赫兹(MHz)突破到吉赫兹(GHz),甚至到太赫兹(THz)[1]。高频电路的广泛应用,使PCB 设计中越来越重视信号的传输质量。在PCB 高速信号传输系统的设计中,信号在传输过程中发生反射是不可忽视的现象,分析信号反射对信号完整性的影响是有研究意义和工程应用价值的。

高速信号的普及应用带来极大的技术优势,同时也给高速电路带来了信号失真、不能正常工作的风险,增加了PCB 设计的难度[2]。随着计算机辅助工程(computer aided engineering,CAE)技术的不断发展,PCB 设计工程师开始使用Hyper lynx 仿真软件分析PCB 设计中传输路径上高速信号的质量。通过仿真软件分析可以发现,传输线阻抗是否匹配明显影响高速信号的传输质量。

本文基于传输线理论阐述了传输线的反射和阻抗匹配原理,采用Hyper lynx 仿真软件分析了5 种阻抗匹配设计的特点,并提出了PCB 设计中改善高速信号质量的方法。

1 信号完整性和传输线理论

1.1 信号完整性

信号完整性是指要保证在一个高速电路系统中,高速信号从源端传出后,无失真地在传输线路上传导,最终到达目的端,目的端接收到高速信号能保证下级系统正常工作并输出正确的结果[3-4]。如果一个高速电路能使电路中所传输的每一个高速信号都保持不失真,则该高速电路便是一个具备较好信号完整性的高速电路系统。在实际的高速、高频PCB 中,高频传输线路不仅会呈现出电阻特性,同时也会呈现出它的电容性和电感性,并且在不同频率下它的容性电路和感性电路值也不相同。

1.2 传输线理论

传输线理论在研究信号完整性理论方面得到了广泛应用,该理论将基本电路分析理论和电磁场分析理论联系了起来。由于PCB 上传输线的物理尺寸可能是电波长的若干倍或是波长的几分之一,所以传输线可以等效为一个具有分布参数的电路网络[5-6]。传输线结构如图1所示,使用双线描述传输线结构,因为信号的传输路径是一个包括发射路径和返回路径的完整回路。图1 中,采用微分的思想取传输线上非常小的一段导体Δz进行理论分析,这段导体可以等效为集总元件电路系统进行研究,集总元件电路结构如图2 所示。长度有限制的传输线可以看作是由多个集总元件电路级联耦合的电路系统。

图1 传输线结构

图2 集总元件电路

传输线工作中,传输的信号波可以划分为混合波、行波和驻波3 种。传输线工作在行波状态下时,传输线上只有入射波,不存在反射波,此时传输线上每点的阻抗一致,整个传输路径上阻抗非常均匀,传输线能完整地传导信号。传输线工作在驻波状态下时,传输线上入射信号和反射信号共存且入射波和反射波幅值相同,传输信号在传输线上进行简谐振动,传输线不能进行有效的信号传导,失去了传输特性。传输线工作在混合波状态下时,传输线上入射信号和反射信号共存但传输线具备信号传输性能,信号的传输质量会变差。在实际工程中,传输线大多数情况下是处在混合波的工作状态,为了使传输线有更好的传输性能,应尽可能地减少反射波的产生。

当反射信号不会出现,也就是当负载阻抗ZL与传输线特征阻抗Z0相等时,传输线达到行波的工作状态,完整传输信号,此时传输线达到阻抗匹配。显然,当传输线达到阻抗匹配时,传输线处在行波的工作状态,传输的高速信号不失真,信号质量最优。

2 传输线的信号完整性分析

2.1 传输线反射

高速信号在传输线上传导时,若传输线的瞬时阻抗不一致,信号便不会完全向前传导,信号的部分能量会从阻抗变化处反射,而信号的其余部分继续向前传输,最终传输到目的端的信号出现失真[7-8]。信号发生反射后,失真信号波形如图3 所示,因为透射波和反射波的叠加,失真信号出现了过冲、欠冲和振铃的现象,信号传输质量下降。

图3 失真信号波形

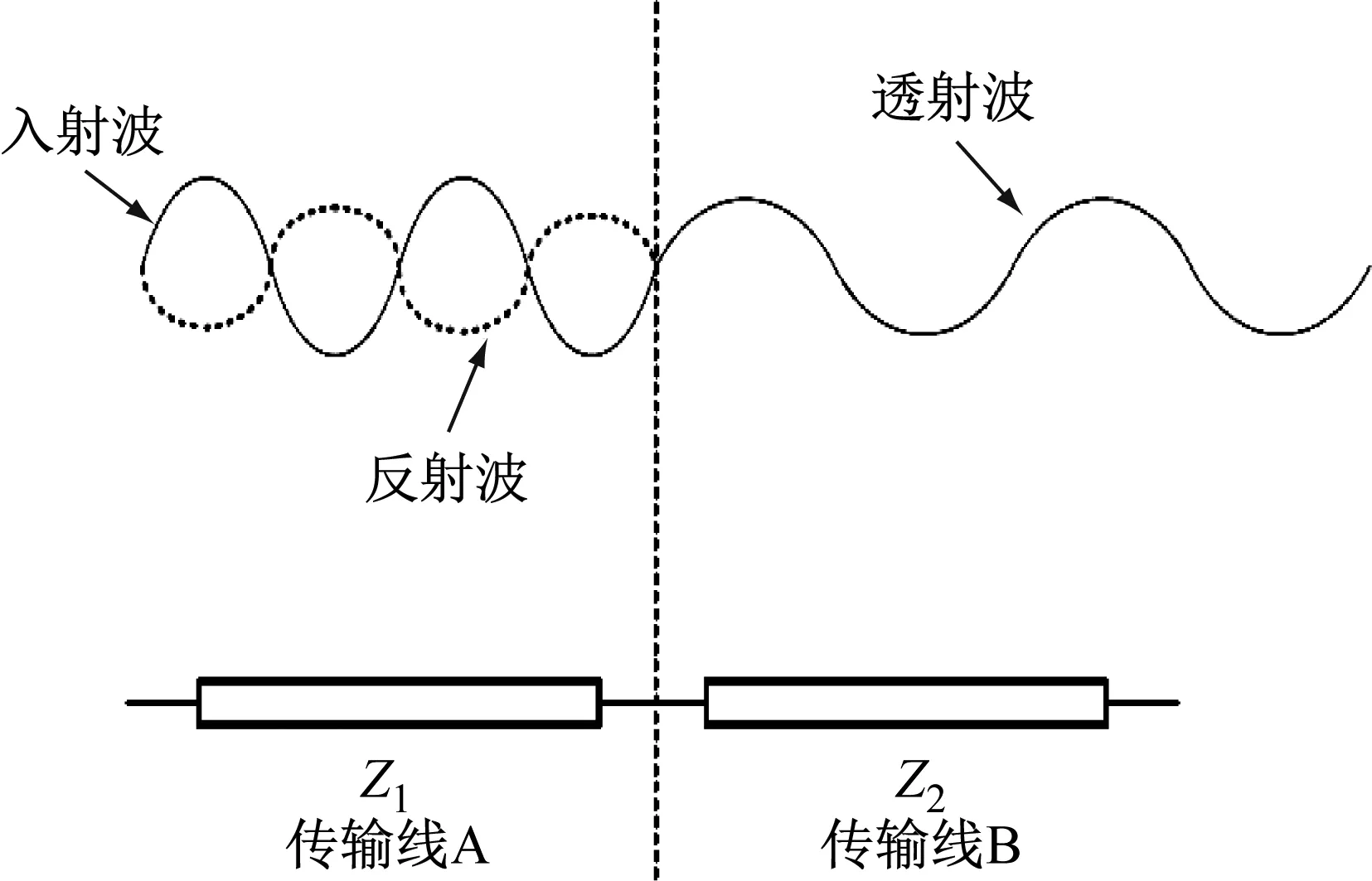

由传输线理论的分析可知,当传输线上阻抗不相同时会引起信号发生反射,信号在传输线上发生反射的示意图如图4 所示。若传输线A 与传输线B 的特征阻抗Z1和Z2不同,传输线A 与传输线B 连接处必然发生阻抗突变,使信号发生反射,降低信号传输质量。

图4 传输线信号反射示意

2.2 阻抗匹配

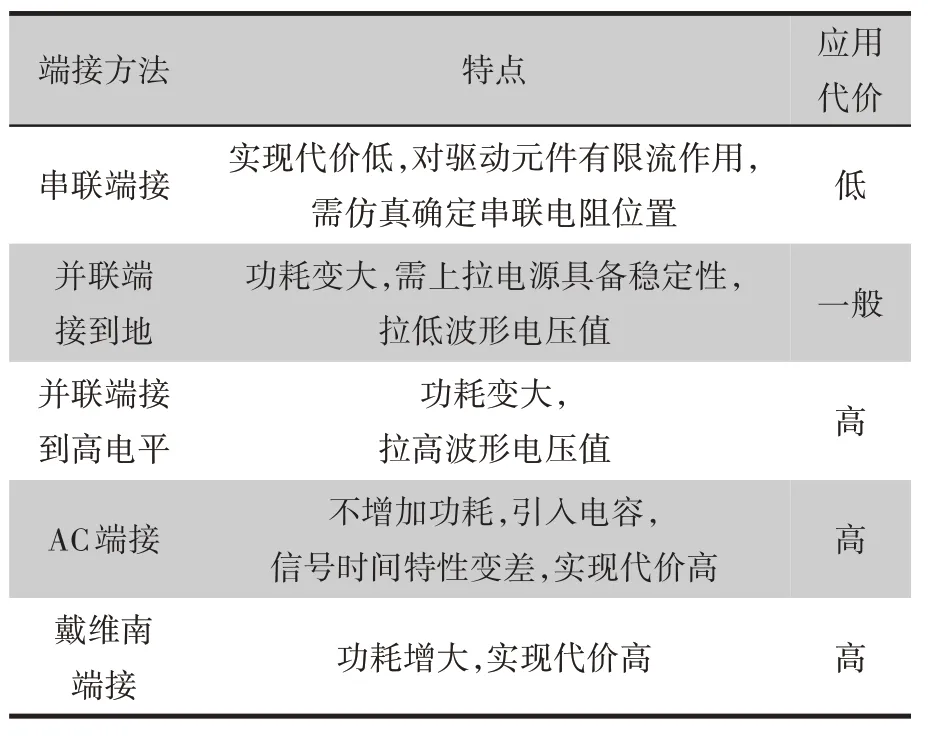

当传输线上的阻抗不一致时,高速信号会发生反射,出现信号过冲、欠冲和振铃等现象。由传输线理论可知,当负载阻抗和传输线特征阻抗相同时,反射系数便为零,使信号反射消失。完善电路结构,使信号传输路径上的阻抗一致,便称为阻抗匹配[9-11]。常用的端接匹配方法有串联端接、并联端接到地、并联端接到高电平、戴维南端接和AC 端接,各端接方法如图5 所示。5 种端接匹配方式的特点总结见表1。

表1 5种端接方法的特点

图5 5种端接方法

3 PCB设计中信号质量仿真分析

3.1 控制板卡仿真模型

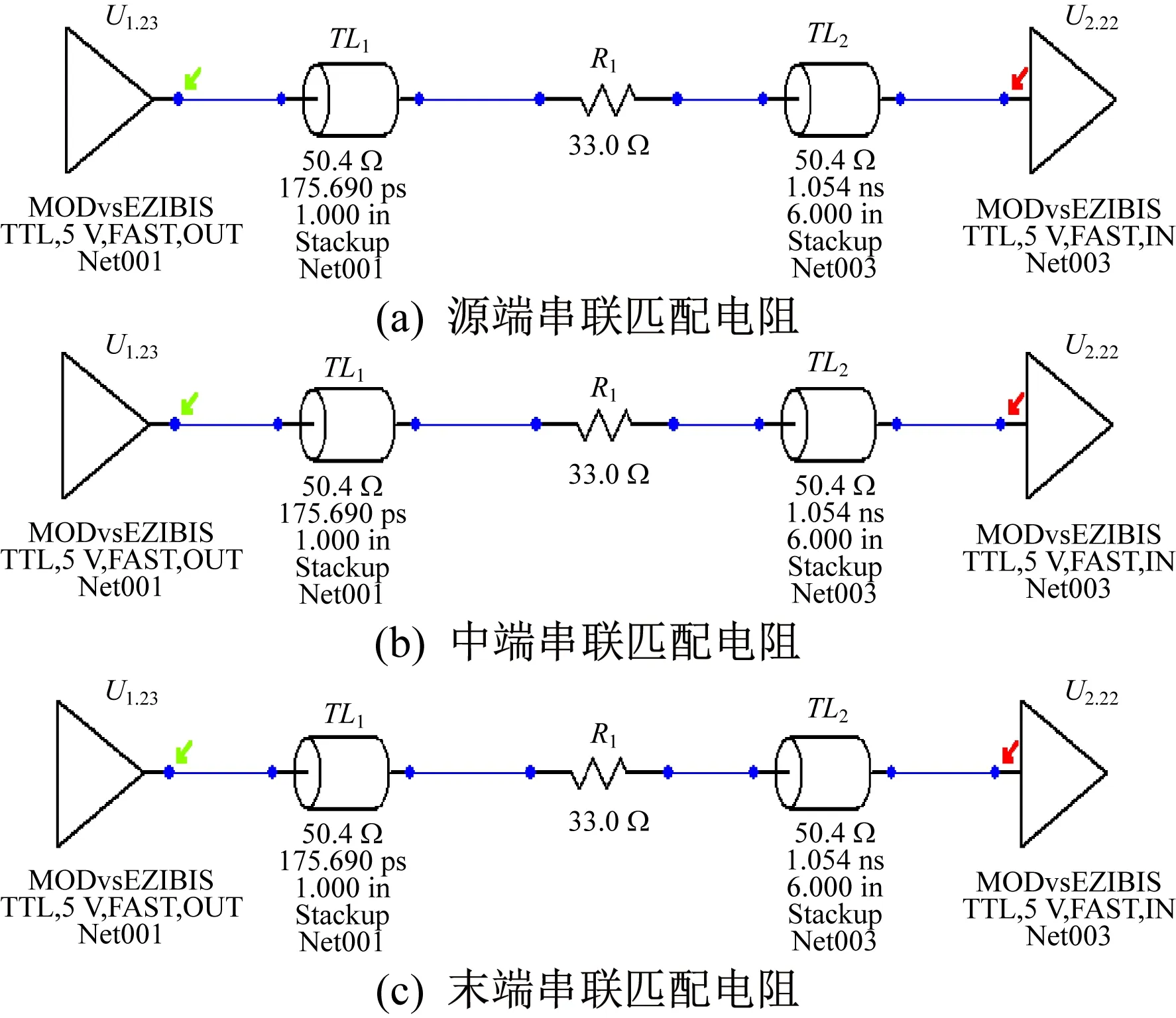

PCB 从原理图出发进行设计时,首先就是进行PCB 上元器件的布局设计,好的布局不仅有利于PCB 的布线设计,而且也可以保证电子产品的可制造性、可维修性和可靠性。分析梳理出电路系统的拓扑结构是进行布局设计的关键,本文研究的控制板卡的电路系统的拓扑结构如图6 所示,研究对象是现场可编程门阵列(field programmable gate array,FPGA)和数字信号处理器(digital signal processor,DSP)之间传输的高速单端信号的信号质量,影响因素设置为传输线有无串联匹配电阻、源端串联匹配电阻、中端串联匹配电阻、末端串联匹配电阻。结合工程实际,建立的电路有无串联匹配电阻的仿真模型如图7所示,建立的源端串联匹配电阻、中端串联匹配电阻和末端串联匹配电阻的仿真模型如图8 所示。建立正确的仿真模型,为后续仿真分析打下了基础。

图6 控制板卡电路系统拓扑

图7 传输线仿真模型

图8 串联匹配电阻仿真模型

3.2 信号质量仿真分析

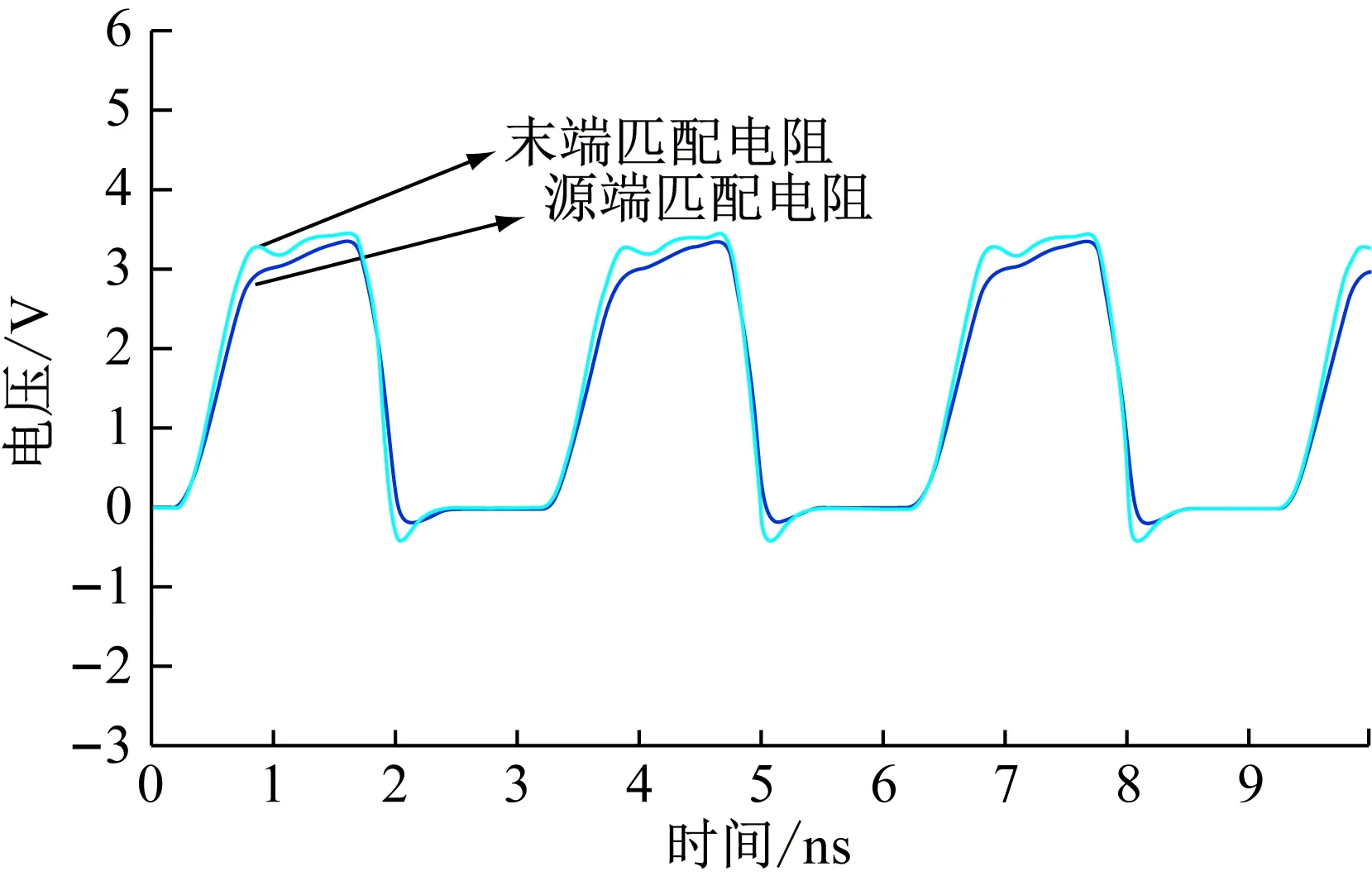

建立正确的电路仿真模型后,对不同模型的信号质量进行Hyper lynx 仿真软件分析对比。仿真模型设置了3.3 V、33 MHz 的TTL 信号为激励信号,对FPGA 到DSP 之间一条177.8 mm(7 000 mil)传输线的33 Ω匹配电阻的目的端接收到的信号质量、源端串联匹配电阻与中端串联匹配电阻的目的端接收的信号质量、中端串联匹配电阻与末端串联匹配电阻的目的端接收的信号质量、源端串联匹配电阻与末端串联匹配电阻的目的端接收的信号质量对比分析,4组对比仿真分析图如图9~图12所示。

图9 有无匹配电阻仿真波形对比

观察仿真结果,由图9 可知,进行了阻抗匹配的传输线比没有阻抗匹配的传输线,传输的信号质量更好。由图10 可知,进行阻抗匹配的长传输线上,源端串联匹配电阻的传输线比中端串联匹配电阻的传输线,传输的信号质量更好。由图11 可知,中端串联匹配电阻的传输线比末端串联匹配电阻的传输线,传输的信号质量更好。由图12 可知,源端串联匹配电阻的传输线比末端串联匹配电阻的传输线,传输的信号质量更好。

图10 源端、中端串联匹配电阻仿真波形对比

图12 源端、末端串联匹配电阻仿真波形对比

综上所述,PCB 设计中,对电路系统中传输高速信号的传输线进行阻抗匹配是改善信号质量的重要方法。如果采用的是串联电阻的阻抗匹配方式,将匹配电阻放置在靠近源端是最佳的布局方式,传输出的信号质量最好。

4 结语

根据传输线理论分析可知,传输线有3 种工作状态,分别为行波、驻波和混合波。要使传输线传输的信号质量最好,就要使传输线工作在行波状态下,此时负载阻抗和传输线特征阻抗相等,称为阻抗匹配。

通过Hyper lynx 仿真软件分析可知,传输高速信号的电路系统要进行阻抗匹配,尽量使用代价较小的串联电阻匹配方式,匹配电阻的布局位置要尽可能地靠近信号发射源端,这样能保证传输到目的端的高速信号质量最好。