C波段宽带薄膜体声波滤波器设计及验证

蒋世义,蒋平英,,马晋毅,陈彦光,徐 阳,刘 娅,徐 溢

(1.中国电子科技集团公司 第二十六研究所,重庆 400060; 2.重庆大学 光电学院,重庆 400044)

0 引言

现代通讯电磁环境错综复杂,对通讯设备的高灵敏、高精度、高速率以及灵活机动性等综合特性提出了更高的要求,需求迫切。射频滤波器为射频链路中的核心元器件,为满足这一需求,急需兼具高频率、大带宽及小体积的特点[1]。目前,射频系统普遍采用的射频滤波器主要有低温共烧陶瓷(LTCC)、声表面波(SAW)和薄膜体声波(FBAR)滤波器。LTCC滤波器虽然可实现大带宽,但由于品质因数(Q值)低,矩形系数小,使近端阻带抑制性能下降,将导致接收机的抗干扰性能下降。SAW滤波器虽然带宽能做很大且具有高温度稳定性,但由于线宽制作限制,难以实现高频滤波。FBAR滤波器不仅具备矩形系数高、适用于高频滤波、耐功率高、重复性好及高Q值等优势,且芯片面积小(约1 mm2),质量轻(小于0.1 g),且由于大量采用微电子标准化工艺,FBAR滤波器具有微电子产品一致性高及可制造性好的特点[2]。

本文介绍了一种适用于三维堆叠小型化的C波段宽带薄膜体声波滤波器的设计及封装方法,并进行了工艺验证。通过对压电层薄膜进行钪掺杂、膜层结构设计、参数优化,实现了相对带宽大于5%薄膜体声波滤波器的设计。通过表面硅基微机电系统(MEMS)工艺制备与凸点式晶圆级封装工艺,完成了滤波器的制备。最终研制出标称频率5 800 MHz、插入损耗小于2.8 dB、阻带抑制大于40 dBc、体积仅1.0 mm×1.0 mm×0.35 mm的C波段宽带薄膜体声波滤波器。为小型化C波段宽带薄膜体声波滤波器的研制提供了有效的设计和工艺技术支撑。

1 C波段宽带薄膜体声波滤波器设计

1.1 封装设计

FBAR滤波器的体积主要由封装形式所决定。为了满足三维堆叠的小体积需求,滤波器将采用晶圆级(WLP)封装形式。而即便是WLP封装,其与基板互联的方式不同,最终整个器件占用面积也不同。

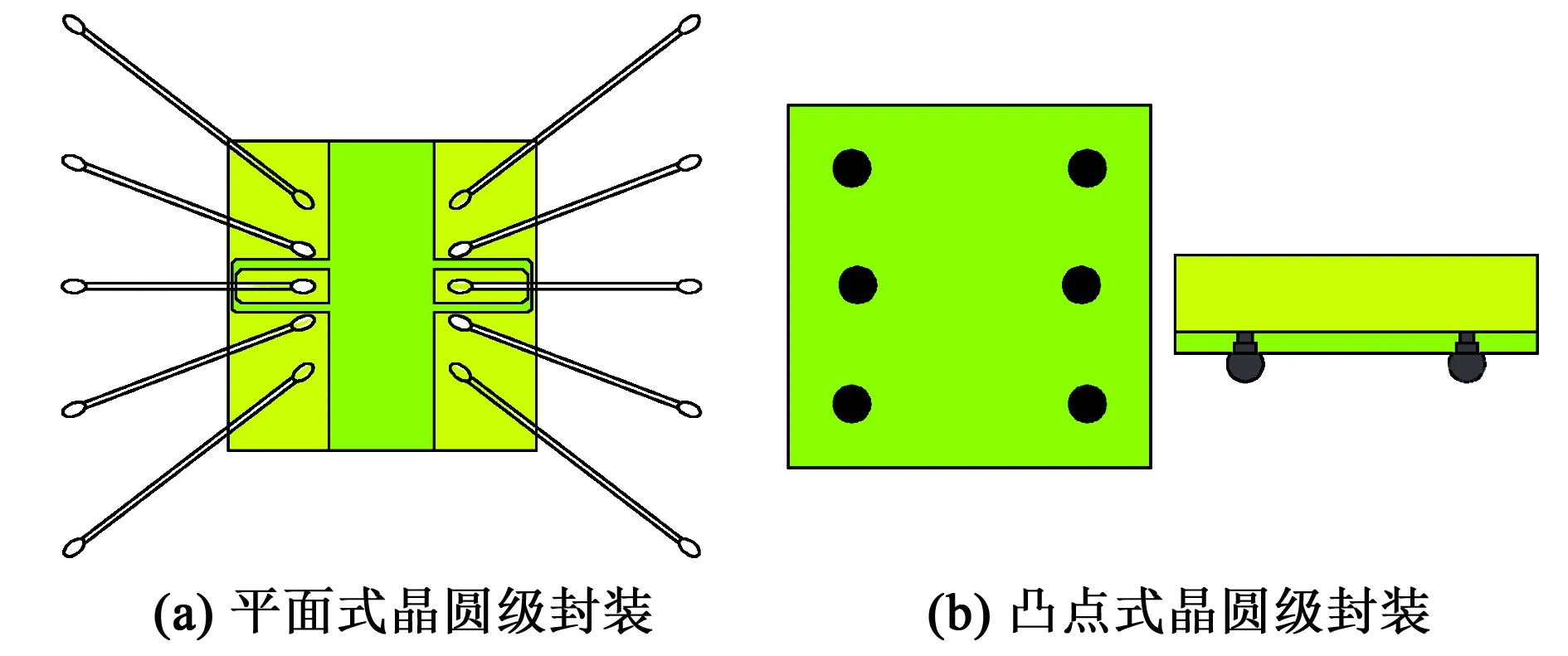

目前常用的WLP封装如图1所示。平面式WLP是目前最常用的,但其需要配合点焊线完成器件与基板电路的互联,额外增加了面积的消耗,总占用面积大;凸点式WLP封装采用盖帽通孔植球,倒装形式与基板互联,占用面积仅为芯片尺寸大小,因此本文介绍的器件采用图1(b)所示的凸点式晶圆级封装[3-5]。

图1 FBAR滤波器晶圆级封装示意图

1.2 压电材料选择

1.3 材料参数提取

材料参数的准确性决定了滤波器的仿真精度,并且薄膜材料与块体材料不同,其材料参数与其膜厚相关。本文对20%钪含量压电材料参数(包括相对介电常数、声粘度常数、纵波声速、密度等)进行提取。

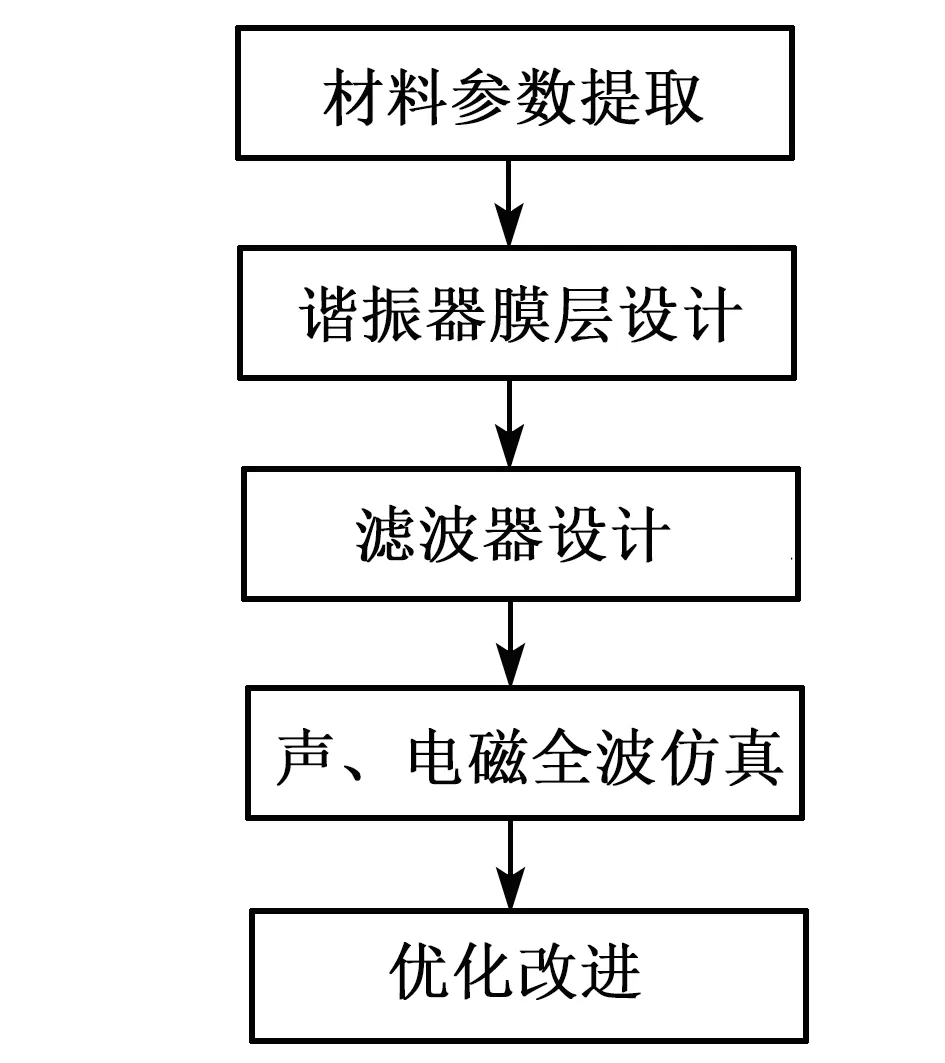

压电薄膜材料参数提取流程如图2所示。首先,采用Mason模型与预设材料参数进行谐振器设计[8],制作并探针测试FBAR,通过去嵌入技术得到谐振器的频响曲线,建立谐振器的等效MBVD模型,按照等效参数与材料参数的系列公式[9],提取得到压电薄膜的材料参数。最后在Comsol软件中进行三维有限元建模验证,从而建立膜厚与材料参数的数据库。

图2 压电薄膜材料参数提取流程

1.4 结构模型优化

1.4.1 声-电磁全波仿真设计流程

本文采用声-电磁全波仿真对FBAR滤波器进行仿真设计,其设计流程(见图3)为:

图3 FBAR滤波器全波仿真设计流程

1) 建立谐振器的MBVD模型,并通过实测曲线和仿真曲线的拟合,提取得到谐振器的参数,并将参数写入优化后的Mason模型中。

2) 利用商用电磁仿真软件建立外围封装的三维电磁模型,用于封装S参数的仿真与提取。

3) 采用Mason模型与电磁参数相结合的方式,进行滤波器仿真设计。

4) 绘制版图,将版图代入仿真模型,得到滤波器的电磁模型。最终进行滤波器带版图的设计及优化,直至满足目标电性能要求。

1.4.2 滤波器膜层及结构设计

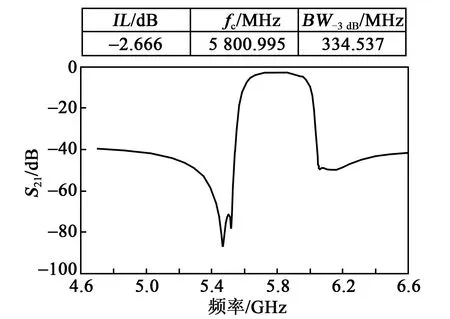

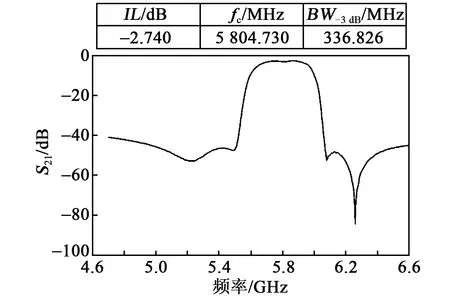

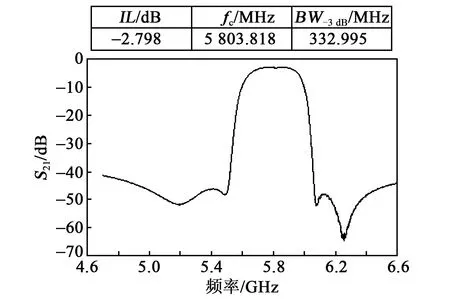

为了获得滤波器的快速滚降,选择了阶梯形滤波器结构。为减小谐振器杂波,通过有限元仿真,选择了合适的电极厚度比及谐振器面积;兼顾阻带抑制和插入损耗,采用了4串4并的拓扑结构。采用商用电磁仿真软件建立封装、基板、焊盘的电磁模型,计算了滤波器外围电路的S参数,如图4所示。通过初步设计,滤波器指标满足预期目标。设计参数如表1、2所示。仿真曲线如图5所示。图中,IL为插入损耗,fc为中心频率,BW-3 dB为-3 dB带宽,S21为幅度。

表1 膜厚设计参数

表2 谐振器面积设计参数

图4 FBAR滤波器初步电磁仿真模型

图5 FBAR滤波器初步仿真曲线

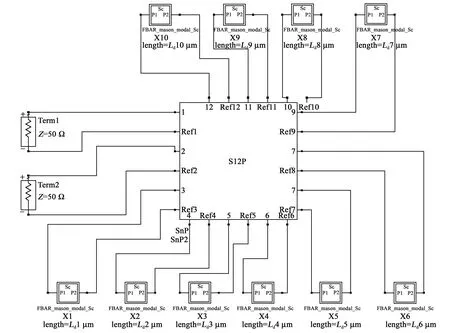

1.4.3 滤波器全波仿真

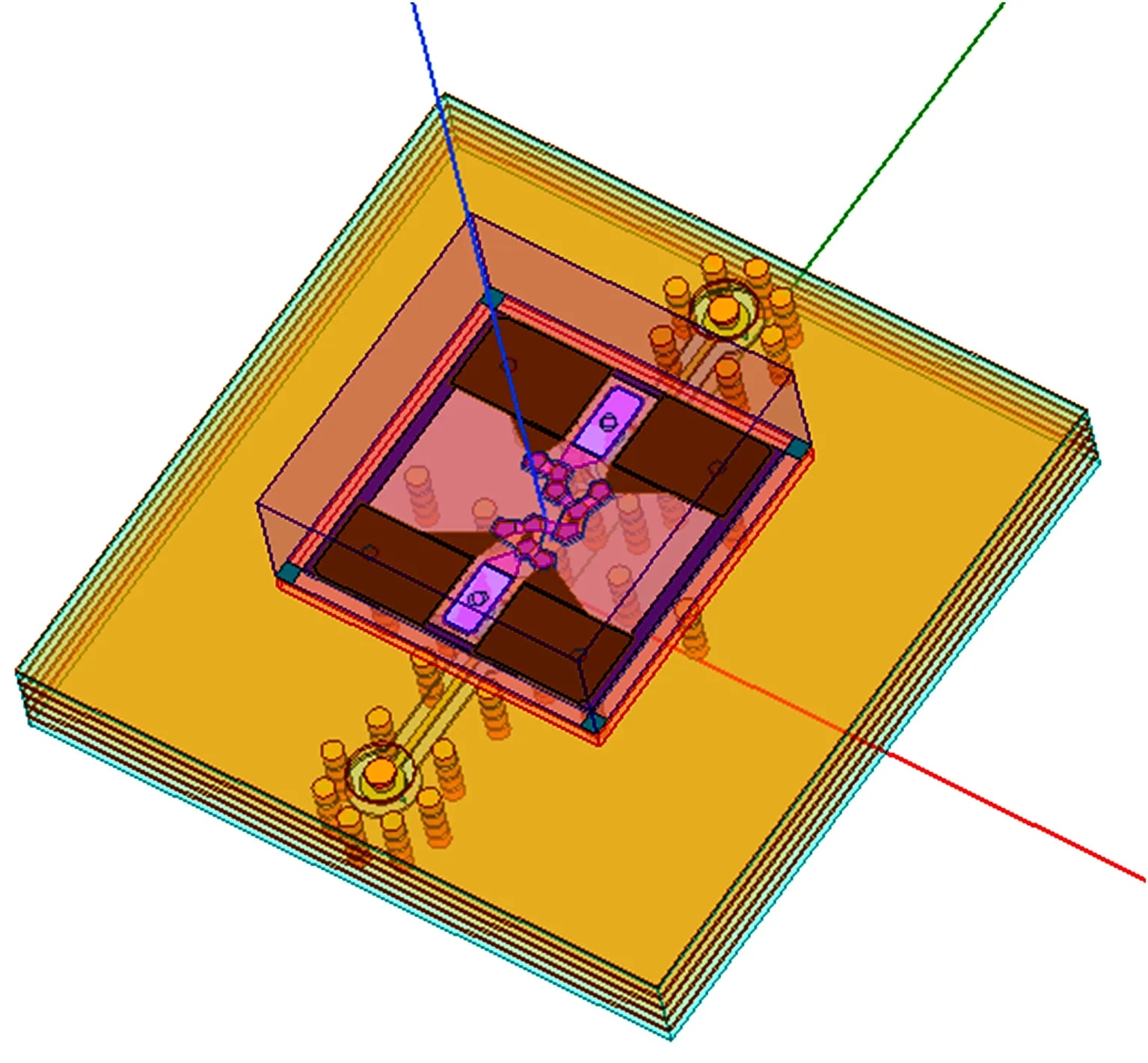

将初仿得到的谐振器数据进行版图绘制,并将绘制完成的版图代入初仿模型中,建立器件的全电磁仿真模型,如图6所示。将相应的谐振器等效模型接入相应的端口(见图7)进行全波仿真,对面积及膜层厚度进行优化后,得到的响应曲线如图8所示。

图6 全电磁仿真模型

图7 全波仿真模型

图8 全波仿真频响曲线

2 工艺验证

在工艺实现上,选用Q值较高的空腔结构,以实现更低的插损,采用高阻硅片进行FBAR滤波器制作。为提高器件的环境适应性、有效保护器件,采用有机感光膜作为封装材料实现WLP封装,工艺流程如图9所示。在封装工艺过程中,通过研究光刻曝光量、烘烤温度、时间等工艺参数,解决了封装过程中导致的FBAR滤波器薄膜塌陷问题[10]。

图9 凸点式WLP工艺流程图

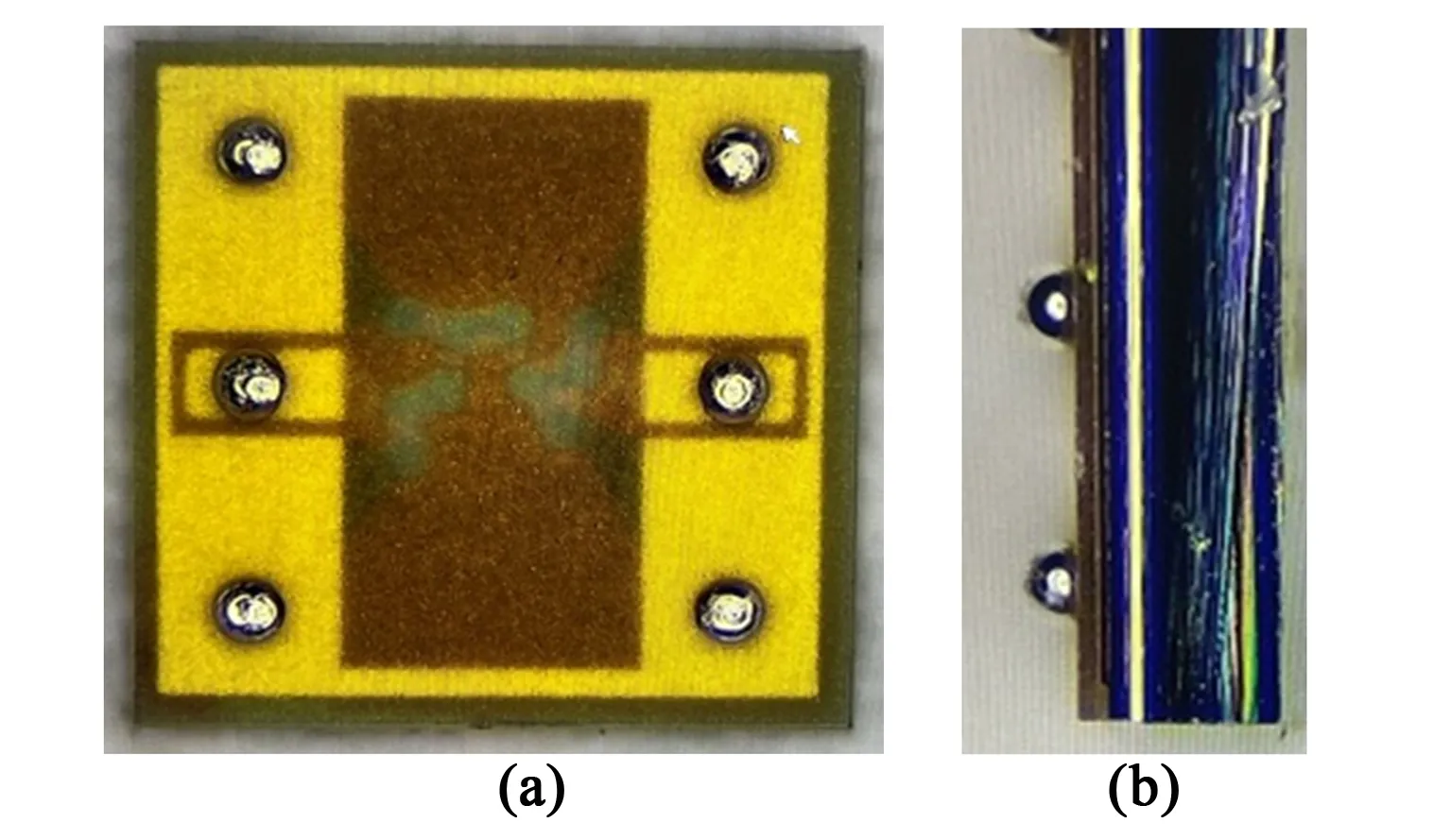

通过硅基表面MEMS工艺,完成了FBAR滤波器的制作,通过有机膜光刻机及植球工艺完成了凸点式晶圆级封装,芯片实物图如图10所示,芯片尺寸为1.0 mm×1.0 mm×0.35 mm。

图10 C波段宽带FBAR滤波器实物图

3 测试及分析

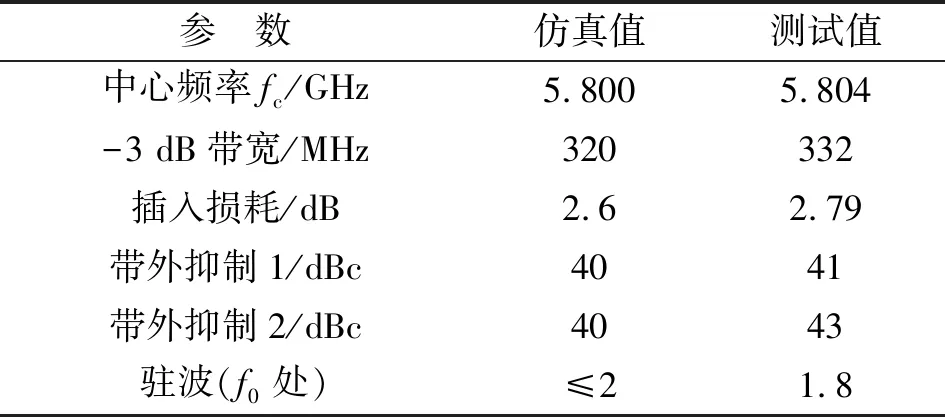

由于器件体积小,工作频率高,外围电磁参数对器件性能影响较大,因此,设计了高频器件专用测试夹具及校准板。通过校准测试,滤波器频率响应曲线如图11所示。仿真与实测参数对比如表3所示。

表3 仿真与实测参数对比

图11 宽带FBAR滤波器频率实测响应图

从表3可看出,实测与仿真结果基本吻合。由于工艺验证过程中膜厚的偏差,导致了频率指标的仿真和实测存在细微的偏差,频率可通过调频工艺进行修正。

4 结束语

本文介绍了一种适用于三维堆叠的凸点式晶圆级封装的C波段宽带薄膜体声波滤波器的设计方法,通过对压电层薄膜进行钪掺杂、膜层结构设计、参数优化实现了相对带宽大于5%薄膜体声波滤波器的设计;通过表面硅基微机电系统(MEMS)工艺制备与凸点式晶圆级封装工艺,完成了滤波器的制备及验证,实现了相对带宽大于5%、带外抑制大于40 dBc的薄膜体声波滤波器,通过测试及分析,仿真结果与实测吻合较好,证明了本文描述的设计及工艺方法的有效性。同时,从初仿与增加版图仿真后的数据对比可以看出,增加版图仿真后的数据与实测数据更为吻合,但增加版图仿真对通带影响较小,对阻带影响较大,为快速实现滤波器性能评估提供了思路。