基于FPGA 的带包覆层管道脉冲涡流在役检测系统设计

黄文丰,杨 帆,付跃文,李朝阳

(1.南昌航空大学 无损检测技术教育部重点实验室,南昌 330063;2.佛山市地铁运营有限公司,佛山 528000)

带包覆层管道被广泛应用于核电领域以及特种设备中,对易发生腐蚀的管道位置常用超声检测或导波检测进行定期检测[1]。传统的检测手段需要拆除部分或全部包覆层进行检测,脉冲涡流检测(pulsed eddy current testing,PECT)作为一种非接触式检测手段可以实现管道带包覆层检测[2-3]。目前PECT 研究主要集中在检测信号处理,根据不同检测对象,使用合适的算法在上位机对厚度或缺陷进行识别,而对实现在役检测带包覆层管道和识别局部缺陷的相关系统研究较少,对能够采集PECT 信号和有效识别厚度和缺陷的仪器存在巨大需求。现场可编程门阵列(FPGA)作为硬件电路,内含大量可通过编程连接的逻辑资源,具有并行处理能力、可重构和低功耗的优点,被广泛应用于信号采集及处理系统。对于PECT,使用FPGA 运算速度更快,根据不同检测需求,方便更新内部逻辑实现不同算法,同时减少对上位机设备的需求,实现微型化系统。

针对带包覆层管道检测,文献[4]通过计算在一定信号幅值区域内信号斜率变化识别不同厚度的检测信号;文献[5]通过改变PECT 探头聚焦特性提升带包覆层管道局部腐蚀缺陷检测能力;文献[6]通过对不同厚度非铁磁性钢板PEC 信号分析,并提取斜率特征量进行厚度检测;文献[7]利用射线检测,无需拆除包覆层,可对带包覆层管道局部缺陷进行设备不停机定期检测,但射线检测时对作业环境需要戒备,具有一定危险性;文献[8]指出定期检测以及抽样检测无法规避日常运行中因腐蚀缺陷造成的管道容器泄漏风险,对在役设备进行在线监测尤为关键;文献[9]搭建物联网分析平台,对油气输送管道实时监控并确定缺陷位置。

针对带包覆层管道设计一套可识别局部缺陷的在役检测系统,有利于提高生产效率以及维护生产安全。本文设计利用FPGA 作为主控芯片设计一款脉冲涡流在役检测系统,利用FPGA 的并行计算能力和可重复编程的特点,搭配低噪声高增益的信号调理电路和24 位模数转换器,采集PECT 信号,并在FPGA 上实现对缺陷检测算法,实现在役检测带包覆层管道的腐蚀情况。

1 系统设计思路

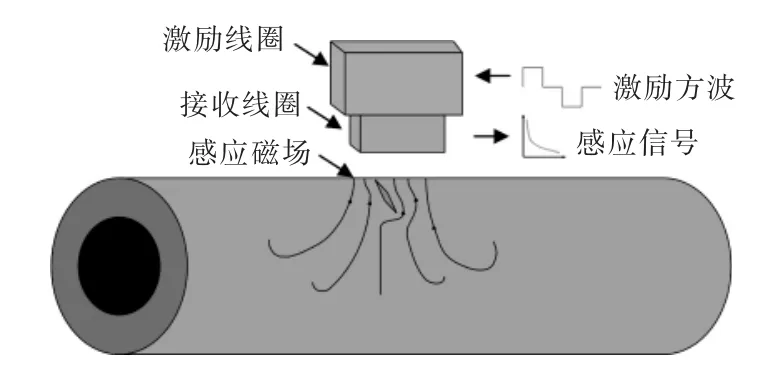

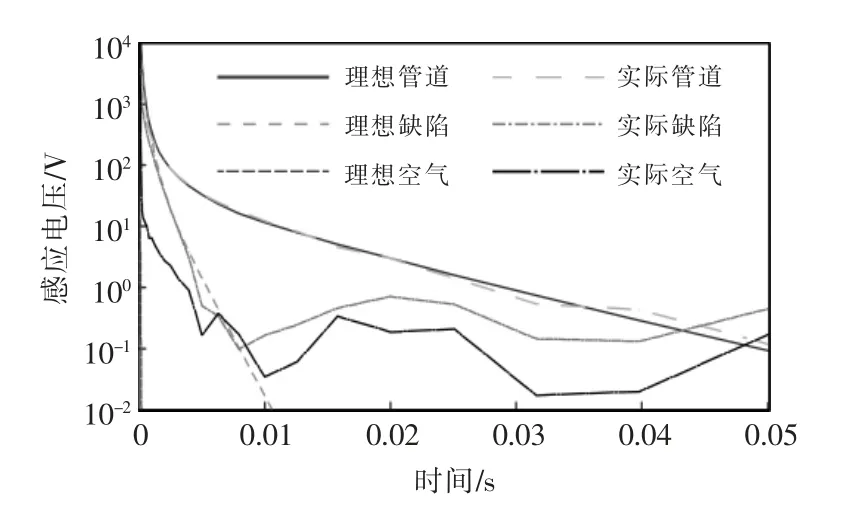

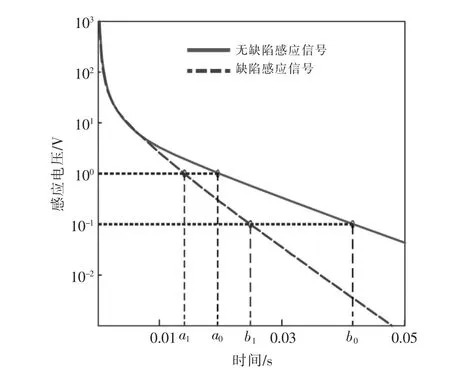

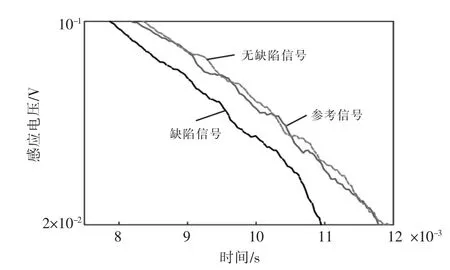

脉冲涡流检测技术是一种新兴的无损检测技术,与常规涡流检测相比,其激励信号是方波,具有更强的能量检测金属构件深层缺陷或减薄,可在不拆除保温层情况下,在役检测金属构件,被运用于带包覆层管道检测。其原理为对激励线圈施加方波,方波下降沿时的涡流感应信号将反映构件的厚度情况,如图1 所示。当出现腐蚀、减薄或缺陷时,感应信号衰减曲线衰减加快,衰减曲线的斜率变化反映被测构件的健康状况,其示意图如图2所示。

图1 检测原理示意图Fig.1 Schematic of detection principle

图2 检测信号示意图Fig.2 Schematic of detection signal

所设计的脉冲涡流在役检测系统,在被测带包覆层管道的易发生腐蚀缺陷的位置上放置聚焦探头,系统定时采集各个探头的感应涡流信号,根据探头检测信号的变化来判断构件的腐蚀情况并报警。

2 系统实现

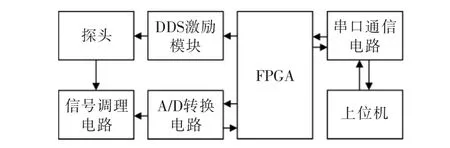

系统由上位机、FPGA 模块、信号采集模块、信号发生器、PECT 探头组成,如图3 所示。系统根据输入参数设置激励信号频率,通过控制信号发生器对探头发射双极性脉冲信号,探头接收线圈上的感应涡流信号通过信号调理电路进行放大,在A/D 转换电路中转换成数字信号传输到FPGA 内进行数据滤波处理。系统将采集正常管道的数据作为参考信号,后续采集信号将与该参考信号运算比对,计算得出检测信号与参考信号之间的斜率变化,使用信号末端斜率作为对腐蚀缺陷的识别特征,分析腐蚀深度程度,并将结果上传到上位机存储。系统可设置时间,定时检测各个位置腐蚀缺陷情况。

图3 检测系统示意图Fig.3 Schematic of detection system

2.1 信号调理电路

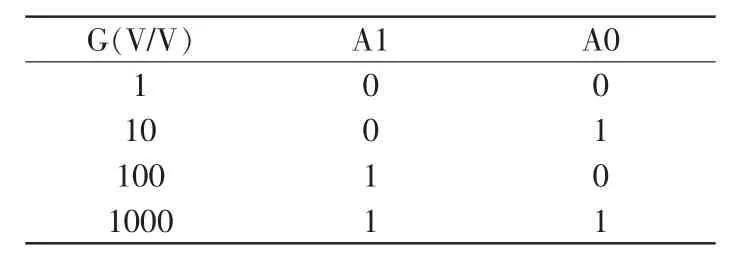

带包覆层管道的脉冲涡流检测信号后期幅值极小,接近几微伏甚至纳伏级别,且容易被噪声淹没,因此需要在采集信号前进行放大处理。选用ADI公司的仪表放大器AD8253 芯片,具有出色的直流低噪声性能,三运放拓扑结构能够滤除共模噪声信号,放大倍数可通过增益引脚被设为1、10、100、1000 倍,如表1 所示。

表1 增益控制Tab.1 Gain control

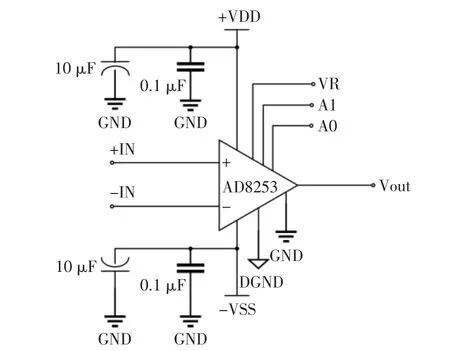

信号从探头差分输入到AD8253,控制放大倍数,将后期信号放大至后续识别处理的幅值范围,其原理图如图4 所示。

图4 AD8253 原理图Fig.4 Schematic of AD8253

2.2 ADC 采样电路

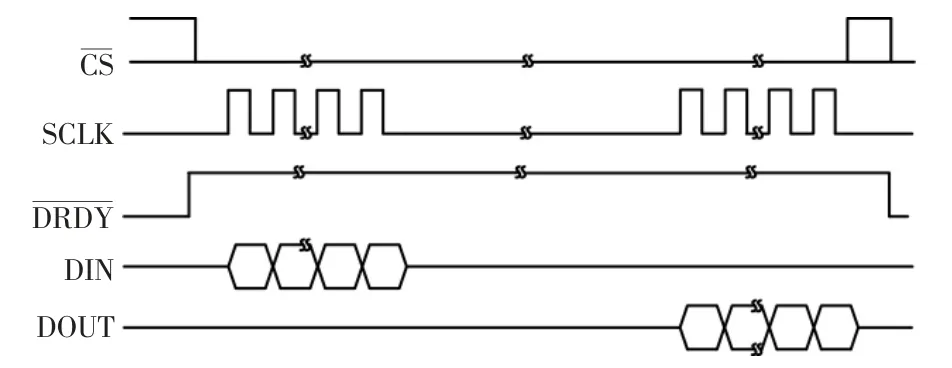

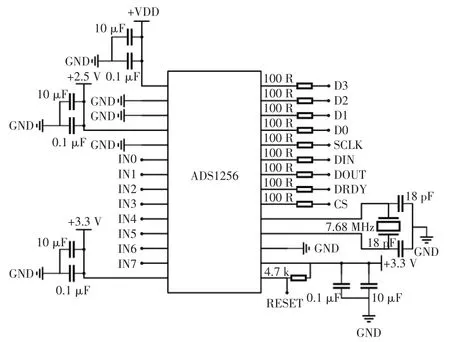

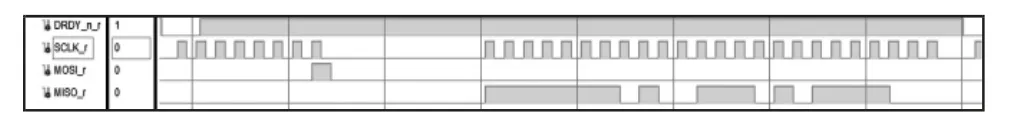

系统模数转换器选择Ti 公司的ADS1256,是一款24 位Σ-ΔADC,其信号有效位为23 位,输入为8通道单端输入或可配置为4 通道差分输入,输入范围为±5 V,采样率最高可达到30 kSPS。ADS1256 通过SPI 协议进行控制,通过写入内部寄存器来设置采集通道、采样率和控制信号采集转换等,其时序图如图5 所示。

图5 ADS1256 时序图Fig.5 ADS1256 timing

设计中将ADS1256 作为从机,在激励方波下降沿时,FPGA 控制ADS1256 进行采集,在SCLK 下降沿,ADS1256 读取指令并写入寄存器,FPGA 从最高位开始读取采样数据,在更改采样通道时,FPGA 对ADS1256 写寄存器指令进行重新配置。ADS1256 通过寄存器来控制采集通道,写寄存器格式为4 位写寄存器指令,8 位地址,16 位寄存器数据,寄存器数据后8 位决定寄存器执行命令。通道寄存器后8 位命令字配置如表2 所示。ADS1256 原理图如图6 所示。

图6 ADS1256 原理图Fig.6 Schematic of ADS1256

2.3 信号处理

由于检测环境复杂多变,检测信号可能夹杂着干扰引起的噪声,主要有白噪声和周围磁场突变引起的尖突噪声等,需要滤除高频噪声和尖刺。Savitzky-Golay 卷积平滑算法能有效滤除信号中的高频部分和剧烈毛刺,平滑信号,用于后续计算曲线拟合斜率,具体操作方法如下:

取信号任一时间点的值y,有:

式中:ai为权重。取半个时窗宽度为N,进行k 阶拟合则有以下方程:

式中:Y*为时窗拟合数据;E 为残差。

由实际检测数据可得式中A 的最小二乘积:

式中:Y 为时窗内实际检测数据,由此可得时窗内拟合数据为

通过计算可得X(XT·X)-1XT,选用中间行数值作为系数,每个时窗中心数据y*为

式中:yi为时窗内实际检测数据;hi为多项式拟合系数。

令N=12、k=6 对时窗内数据进行拟合,通过式(6)求出参数,确定好参数后,在FPGA 上进行运算得到平滑数据。

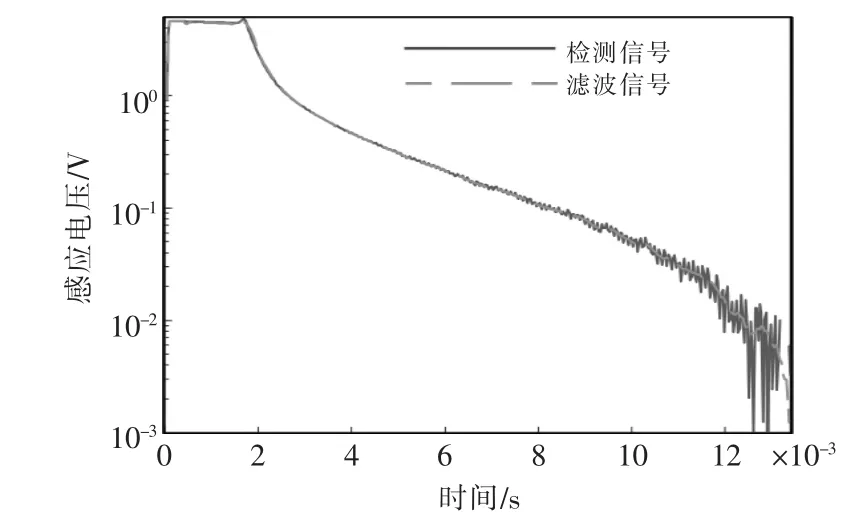

脉冲涡流检测信号在单对数坐标系如图7 所示,通过计算某个电压幅值范围内的斜率,判断该信号所处位置是否有缺陷。

图7 脉冲涡流信号原理图Fig.7 Schematic of pulsed eddy current testing signal

在一个幅值范围内,检测斜率k 存在关系:

根据实验可得出被测带包覆层管道的斜率区分幅值范围,在FPGA 上为了节省芯片内部资源和运行时间,可通过判断信号在此区域内的时间长度来区分管道缺陷大小。管道缺陷位置检测信号在区域内的时间长度会小于正常管道检测信号,故当区域内的时间长度小于所设置的阈值时,系统将会在该位置上的探头报警。

2.4 FPGA 代码设计

使用Verilog HDL 语言编写FPGA 各个模块,包括ADC 控制模块、算法运算模块、时钟分频模块和通信模块等,实现激励探头、信号采集处理及通信。

2.4.1 激励和采集模块

模块定时对功率放大器发送双极性方波信号,方波下降沿同步触发采集模块,控制ADC 采集检测信号,参考信号存入一个RAM 中,其他检测信号将存入另一个RAM 中,方波上升沿采集结束后,数据进行后续降噪处理。

2.4.2 信号处理模块

在完成一次采集后,对缓存数据进行平滑滤波处理,先求出Savitzky-Golay 卷积平滑算法参数。利用FPGA 计算时窗内各个数据与系数之间乘积,计算浮点数乘法会占用过多乘法器资源,因此利用数据右移代替数据与浮点数乘法,比如与系数0.042146 相乘,等效成数据右移5 位、7 位、9 位、10位后再求和。该模块每处理一个数据需要25 个数据进行处理,降噪数据前12 个数据和最后12 个数据与原数据相等,因此结果会延迟采集数据13 个系统时钟。每个数据处理后与所预设的幅值区域比较,当采样数据进入该区域内时开始计时,与参考信号比较在该区域内的时钟数,判断该管道位置有无缺陷。当检测信号在区域内的时钟数超出所设阈值范围,系统将对该位置进行报警,并将检测数据保存至RAM 中并上传至上位机。

3 试验结果

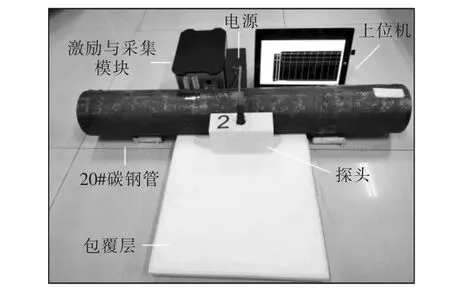

实验使用长度800 mm、外径120 mm、内径100 mm 的20# 碳钢管道,管道中部外表面有一个40×40×3(mm3)的局部缺陷。在40 mm 提离下,激励信号为4 Hz 的5 V 双极性方波信号,放大1000 倍采集带包覆层碳钢管道的感应信号,将采集数据上传至上位机,检测系统实物如图8 所示。

图8 系统实物图Fig.8 Physical diagram of the system

根据式(6)预先计算好滤波算法所需参数和判断缺陷的阈值,所得参数如表3 所示。

表3 Savitzky-Golay 拟合参数Tab.3 Savitzky-Golay fit parameters

使用片上逻辑分析仪(ILA)抓取FPGA 采集模块内部信号,图9 所示为SPI 通信管脚的电平变化时序图,实际采样率为30120 Hz。

图9 ADS1256 实际时序图Fig.9 ADS1256 actual timing

图10 所示为脉冲涡流检测信号与降噪后的信号,Savitzky-Golay 算法可有效去除信号中的噪声和脉冲,使检测信号平滑,在半对数坐标系下,处理后的检测信号在预设的幅值范围内递减。选取合适的采集信号作为参考信号。与传统PC 机上进行运算对比,使用FPGA 进行处理的速度大大提高,比PC机快120 倍。

图10 脉冲涡流检测信号Fig.10 Pulsed eddy current detection signal

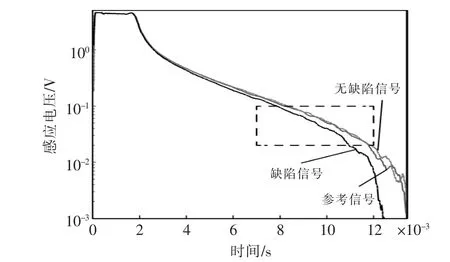

按表3 所示,切换通道采集有无缺陷位置的感应信号,采集及处理结果如图11 所示。可以看出,缺陷位置的检测信号相较于无缺陷位置,信号衰减速度更快,斜率更小,区域内时间更短,不同信号在选取的幅值区域如图12 所示,其时间如表4 所示。

表4 不同位置检测信号的区域内时间Tab.4 Time in region of different position detection signals

图11 不同位置检测信号Fig.11 Different position detection signals

图12 选取区域内检测信号Fig.12 Detection signals in region

由表4 所示,检测信号的区域内的时钟数低于参考信号17 个时钟数,超出所设阈值,视作检测到缺陷,系统在该位置进行报警,并将该组数据存入RAM 中。

4 结语

通过设计一套带包覆层管道脉冲涡流在役检测系统,对管道局部腐蚀缺陷进行监测,检测到缺陷时自动报警,节省定检时的人力物力,可以通过根据不同要求设置不同阈值以达到检测效果。

本设计使用FPGA 作为主控芯片,能达到更高的运算速度,比使用PC 机运算快120 倍,节省了数据传输的时间。FPGA 方便改变芯片内部逻辑,从而灵活更改识别检测方法,因此可通过修改逻辑实现不同算法,减少对上位机的需求,微型化系统,应对其他不同结构或材质金属构件缺陷厚度检测。仪器可接入多个探头,根据改写ADC 寄存器控制采集通道,同时FPGA 充足的引脚数量允许使用更多通道的采集卡。