基于FPGA的差分延迟时间测量电路设计

杨 仪,周 严

(南京理工大学机械工程学院,江苏南京 210094)

0 引言

时间数字转换器TDC是微小时间间隔测量的专用电路结构[1],在高分辨率时间间隔测量、频率测量和相位信号分析等高精度、高分辨率测量领域有着重要的应用[2]。等精度同步的频率测量法,由于其计数闸门和基准时钟信号不同步,使基准信号的脉冲上升沿与计数闸门的边沿不重合,导致计数闸门的微小起始误差Δt1和微小终止误差Δt2,进而降低了频率测量的精度及分辨率。精确测量起始误差Δt1和终止误差Δt2是实现频率高精度、高分辨率测量的关键。

目前,实现微小时间数字化的方法主要包括高频计数法、游标法、抽头延迟线法以及差分延迟线法等[3-5]。随着集成电路工艺的不断成熟,抽头延迟线法和差分延迟线法因具有成本较小、集成度高的优点被越来越多的使用。其中,抽头延迟线法的分辨率由延迟线中单个延迟单元的时延决定,这就受制于CMOS(complementary metal oxide semiconductor)的工艺水平。但是差分延迟线法只需要标准的CMOS工艺,在同样的工艺水平下它可以实现更高的分辨率[6]。

在众多TDC架构中,基于FPGA的TDC近年来变得越来越重要,因为它们具有高性能、更高的灵活性以适应应用程序的特殊需求,与ASIC(application specific integrated circuit)TDC相比,开发时间更短[7-8]。因此,利用FPGA上的逻辑单元阵列来搭建TDC已经成了近年来的主流方法。

本文提出了一种基于差分延迟线法的TDC电路,可在FPGA平台上实现对微小时间的高精度测量及数字校准。

1 电路原理及系统设计

1.1 差分延迟线原理

差分延迟线的基本结构如图1所示,由2条时延不同的延迟线和一组触发器组成,开始信号START与停止信号STOP上升沿之间的延迟即待测时间Δt。上延迟链的时延为τ1,下延迟链的时延为τ2,τ1略大于τ2。开始信号上升沿沿着上延迟线传播,每延迟τ1到达一级触发器的数据出入D端。同理,停止信号经过τ2延迟到达触发器的时钟输入CLK端。触发器在停止信号上升沿到来时对此刻的开始信号进行采样,输出“1”。每经过一级延时,两信号上升沿之间的时间差减少τ1-τ2。直到经过m级延迟后,停止信号的上升沿赶上并超前于开始信号,此时触发器输出“0”。触发器组将产生低m位全1高位全0形式的温度计结构输出,经过译码后可以得到其中“1”的个数,即m的值。从而得到微小时间差为

图1 差分延迟线结构图

Δt=m(τ1-τ2)

(1)

测量分辨率σ为

σ=τ1-τ2

(2)

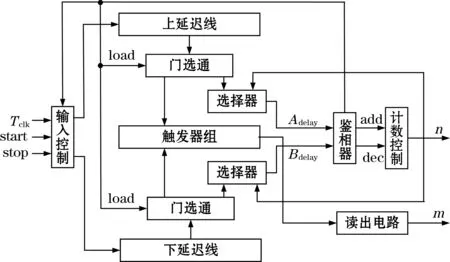

1.2 数字校准电路

采用差分延迟线法尤其是采用ASIC实现的TDC,大多数采用PLL(phase locked loop)或DLL(delay locked loop)进行校准[3]。PLL的压控振荡器会引入固有的不稳定性,并会引入相位误差和积累,但无条件稳定的延时锁定环(DLL)结构则不会累积相位误差。而就DLL的实现方式而言,用数字电路实现在噪声敏感度方面优于用模拟电路实现,且具有较低的功耗和抖动性能。因此,在时延补偿和时钟调整的应用中,全数字 DLL结构具有优势[8]。电路使用DLL对延迟链校准的基本思路是鉴相器比较两个信号的相位关系,通过电荷泵充放电改变压控延时单元的电压,将2条延迟链的总延时差锁定到1个参考时钟周期。

图2给出了本文设计的数字DLL校准电路。它由两条N级延迟链,两个N输入选择器,鉴相器和计数控制单元组成。A、B端输入的信号上升沿之间的时间差为一个参考时钟周期Tclk。首先控制选择器都只输入一个延迟单元,A、B信号分别经过一个延迟单元后得到Adelay、Bdelay信号,鉴相器比较这两个信号的到达先后。如果Adelay信号先到达,则说明延迟时间太小,B信号不足以赶超A信号,需要增加延时单元,计数控制模块使选择器的输入递增;反之,则说明延迟时间太大,控制选择器输入递减;当两信号同时到达时,鉴相器输出锁定信号load锁定选择器的输入,标志校准完成。计数器输出此时选择器的输入个数n,即每条延迟链的级数。那么每一级延时的时延为Tclk/n。因此,TDC分辨率为

图2 数字DLL结构图

σ=Tclk/n

(3)

σ值根据环境变化而变化,可以有效避免温度、电压以及不同电路元件工艺误差带来的影响,使TDC具有更高的通用性和更小的误差。

鉴相器的设计采取图3结构。复位信号RST高电平有效,低电平时鉴相器开始比较Adelay和Bdelay输入的先后顺序。在Bdelay信号的上升沿时由第1个触发器对Adelay采样,输出Q1;2个信号分别延时τ1和τ2之后,输入第2个触发器,此时是Adelay上升沿对Bdelay采样,输出Q2。Q1和Q2和输入信号的相位关系如表1所示,可以通过查表确定计数模块的状态,递加时add信号高电平,递减时dec高电平,一旦锁定load信号高电平。

表1 鉴相器输入相位关系

图3 鉴相器

1.3 TDC总体结构

TDC的整体结构如图4所示。首先,输入控制模块基于参考时钟产生2个信号用于校准,其上升沿的时差为1个参考周期Tclk。此时鉴相器未锁定,load信号低电平,输入图5所示的选通门电路控制延时线处于校准状态。延迟线中前一级信号从A1端输入,从A2端输出到下一级延迟单元。load信号低电平时,下三态门工作,每级延迟之后的信号从AMUX输入多路选择器,开始校准;校准完成之后load高电平,输出延迟级数n,上三态门工作,延迟链的各级信号从Adff进入触发器组,开始测量。测量完成后,将温度计结构数据送入译码电路读出测量级数m。

图4 TDC整体结构图

图5 选通门电路

最终通过该TDC测量的时间间隔为

(4)

2 试验及结果分析

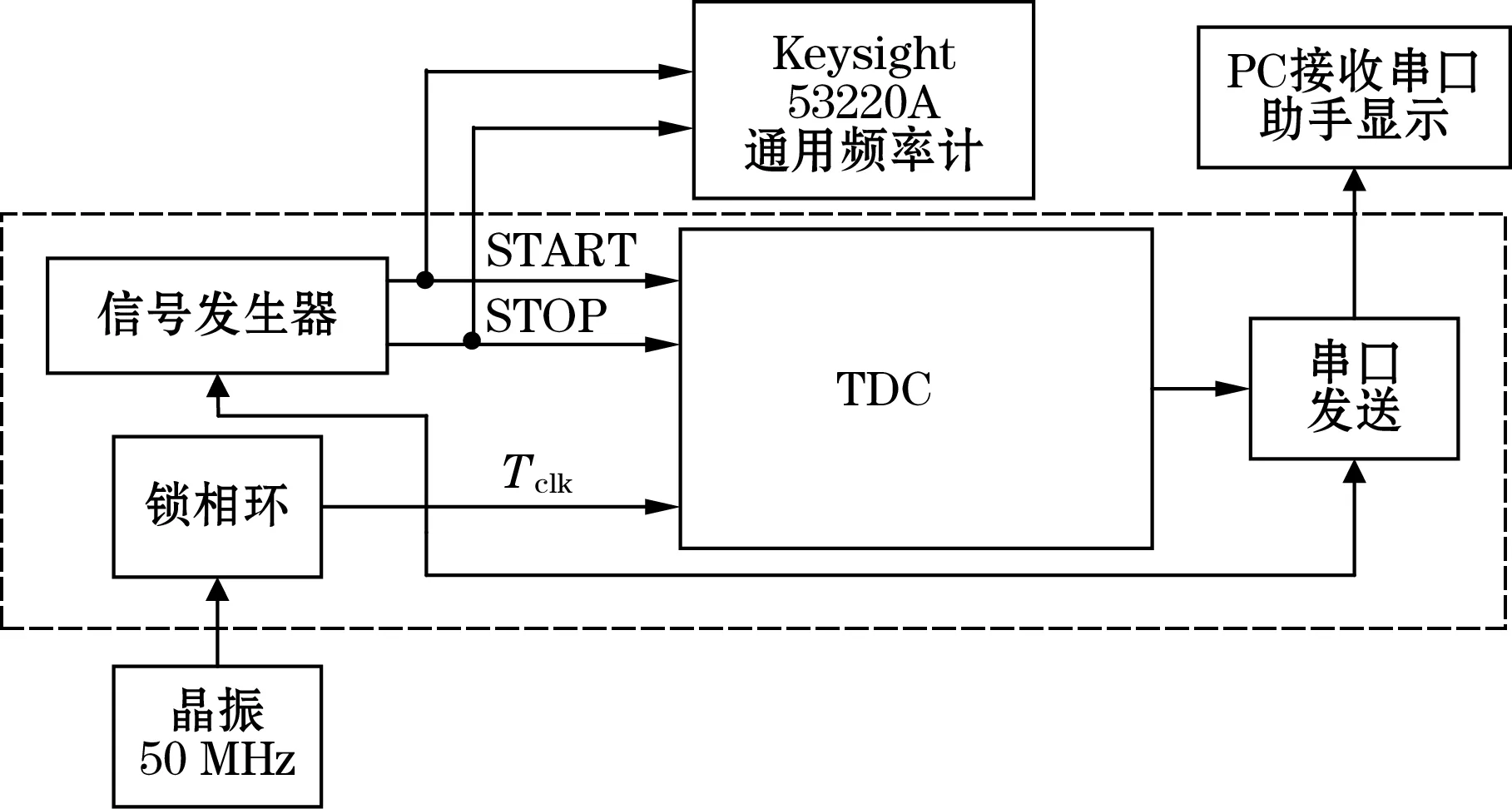

2.1 电路实现及测试平台搭建

本文设计的电路在Xilinx公司的开发板上搭建并进行测试。2条延迟线中的上延迟线使用逻辑非门串联,每2个逻辑非门组成一级延迟单元。由于FPGA中的简单逻辑关系都是通过查找表实现,因此2个逻辑非门通过调用LUT的原语实现;下延迟线使用快速进位链,其中的每个CARRY4作为一级延迟单元。CARRY4固有的级联特性使多个CARRY4单元在底层呈现链状分布,只需要约束第一个的位置,就可以自动形成如图6所示相对均匀的链状。布局布线之后,对电路进行时序仿真,上延迟线的单级时延在240~260 ps之间,下延迟线的单级时延在80~90 ps之间。根据式(2),TDC的分辨率σ可以达到150~180 ps。

图6 超前进位链布局结果

该TDC是对小于等于频率计1个参考时钟周期的时间进行测量,本设计的参考时钟频率为250 MHz,因此延迟线的最大延时需要大于4 ns,即

σ·N>4 ns

(5)

考虑到极端情况下σ=150 ps,N取27。

试验所用的TDC测试平台如图7,外部晶振的频率50 MHZ,调用FPGA内部的锁相环IP核,将晶振信号倍频4倍后产生频率为250 MHz的Tclk,作为TDC电路的参考时钟以及串口发送模块的系统时钟。同时,利用CARRY4和和计数器搭建一个简易的芯片内部信号发生器。高频的参考时钟信号输入信号发生器之后先经过计数器分频成低频信号START,再经过快速进位链延时产生STOP信号。通过改变快速进位链中CARRY4的个数即延时级数,就可以产生多个延时不同时间间隔的待测信号。START和STOP信号一方面输入TDC电路中进行测量,一方面经FPGA开发板的扩展口输出,由Keysight 53220A 350 MHz通用频率计进行测量。TDC的测量结果由串口传输至计算机,与频率计的测量结果进行对比。

图7 测试平台结构

2.2 TDC测试数据

测试平台搭建完成之后,测量9组时间间隔不同的待测信号。在25 ℃室温下进行测量,测试结果如表2所示。

表2 TDC时间测量数据 ps

分析数据可以得到单次测量绝对误差最小小于3.5 ps,最大小于90 ps。

保持信号发生器中超前进位链的延迟级数不变。在-10~30 ℃对延时单元时延进行测量。从图8可以得到,-10 ℃下延时单元的时延为154 ps,30 ℃时延为173 ps,在此范围内分辨率较稳定。

图8 延时单元时延温变情况

3 结束语

本文提出一种基于FPGA的全数字差分延迟TDC补偿电路并针对其精度误差和稳定度进行了相关测试。经测试,在动态测量范围以及分辨率方面都具有较好表现,且在0~30 ℃之间有较高的稳定性。该电路已经在高精度频率计中使用,并为高精度TDC的ASIC集成化提供了设计思路及经验。