基于EBAPS 的全国产成像电路研制

杨婧薇,钱芸生,柳 磊,卢 杰

(南京理工大学 电子工程与光电技术学院,江苏 南京 210094)

引言

电子轰击型有源像素传感器(electron bombarded active pixel sensor,EBAPS)是一种高性能的真空-半导体混合器件,具有高灵敏度、快响应度、低成本、低功耗等优点,广泛应用于军事装备、遥感测绘、空间探测等领域,研究EBAPS 已成为数字微光夜视技术研究领域的重点方向[1]。EBAPS 是减薄后的互补金属氧化物半导体(complementary metal oxide semiconductor,CMOS)芯片在像增强器荧光屏位置进行耦合,通过采用光电子转换成高能倍增电子的方式,使低照度光电图像得以倍增的[1]。其工作过程如下:微弱的光信号透过入射窗到达光阴极,在光阴极表面发生外光电效应并产生微弱的光电子信号;在光阴极与电子敏感CMOS 负高压的作用下,电子加速撞击有源像素传感器(active pixel sensor,APS)表面的电子倍增层以实现电子数目的倍增;产生的二次电子被传感器结区收集后经过光电二极管输出,实现微弱信号的探测与采集,以方便后续信号的处理[2]。

EBAPS 技术属于高科技军事领域,美国和法国在这方面的研究成果最为突出。1999 年,美国Intevac 公司率先发布了电子轰击有源像素传感器混合型光电探测器的相关发明专利[3];2005 年,美国Intevac 公司发布了ISIE6 和ISIE10,相对于Night Vista 帧频提升,读出噪声减小,低照度性能更优[4-5];2009 年,法国核物理研究所研制的EBAPS 器件的灵敏度探测下限达到了单光子量级[6];2013 年法国Photonis 公司推出名为EBNOCTURN 的EBAPS 相机[5-7];2020 年,Intervac 公司为美国海军提供ISIE19型EBAPS 传感器,便于海军陆战飞行员在微光环境下正常执行任务[5]。在国内,以北方夜视技术股份有限公司和微光夜视技术国防科学重点实验室为代表的研发团队已在EBAPS 的理论研究、器件制备等方面取得一定成果[2,8-9],但其成像电路所采用的多数芯片主要依赖于进口。由于美国在半导体行业对中国的制裁,使得芯片供不应求,阻碍了我国EBAPS 成像系统的发展,因此,本文基于EBAPS的国产成像电路研制展开了深入研究。

本文拟设计一套基于EBAPS 的全国产成像电路评估板。该系统全部采用国产芯片,以FPGA 芯片作为核心处理器,针对我国自主研发的电子轰击型有源像素传感器的特点设计成像电路;其电路对CMOS 图像传感器输出的图像信号进行实时采集,并通过数字图像处理算法提高成像质量;采用Cameralink 接口实现1 280×1 024 pixel@30 f/s 视频输出。该成像系统可实现3×10-3lx 环境照度下目标物体的成像,对微光夜视技术和国内集成电路产业的发展具有重要意义,对低照度环境下的探测工作有一定的应用价值。

1 整体方案设计

1.1 EBAPS 选型

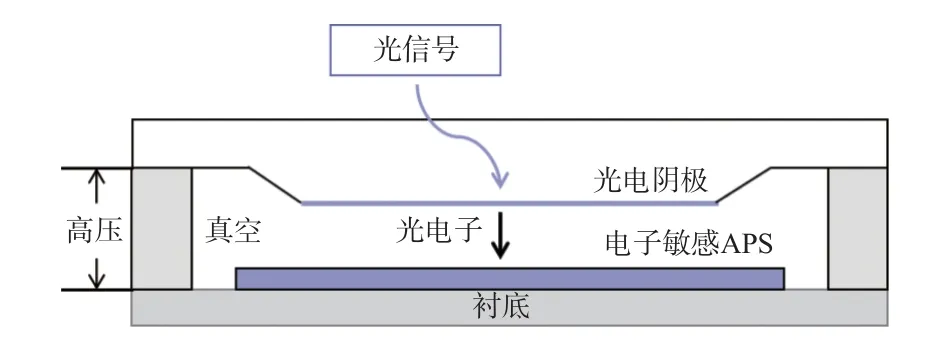

本文选定了国内某公司用国产APS 芯片完成封装的正照式EBAPS 器件,其基本结构[1-2]如图1所示。该APS 芯片分辨率为1 280(H)×1 024(V)像素,像素时钟最大不超过80 MHz,主要工作波段为0.3 μm~0.97 μm,卷帘门式曝光,由9 路外部信号控制,分别是VSYNC、HCLK、HSYNC、VCLK、RD1、RD2、RST、SEL、T,其中VSYNC 信号的占空比设置决定有效曝光时间,且采用模拟差分输出方式。APS 芯片的主要技术参数在一定程度上会影响其他器件的选型与硬件电路的设计,芯片主要技术参数如表1 所示。

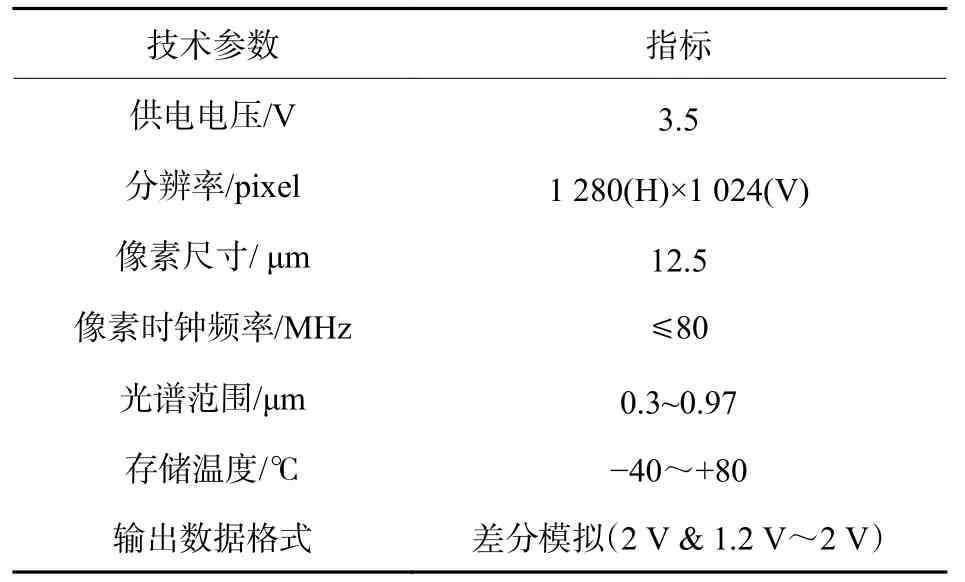

表1 APS 芯片主要技术参数Table 1 Main technical parameters of APS chip

图1 EBAPS 基本结构示意图Fig.1 Schematic diagram of basic structure of EBAPS

1.2 硬件设计框架

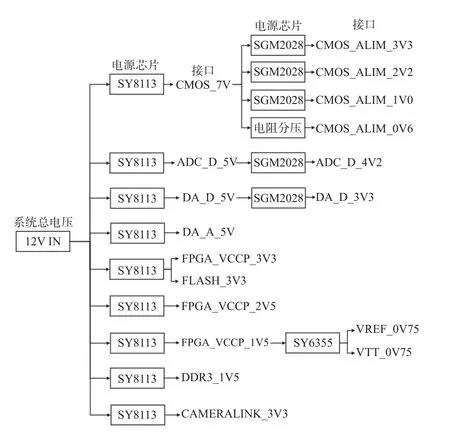

本系统将复旦微电子FMK50t 系列FPGA(field programmable gate array)芯片作为核心处理器,含CMOS 图像传感器模块、模数信号转换模块、FPGA核心板模块、视频输出模块以及系统供电模块5 个模块。其中,CMOS 图像传感器模块由FPGA控制,在高压电子轰击模式下,器件表面的光阴极接收到光学镜头汇聚的光信号,光阴极发生光电效应产生光电子,在高压电场的作用下,光电子加速撞击APS 芯片实现电子倍增,最终以一对差分模拟信号输出;模数信号转换模块完成模拟信号到数字信号的转换,在接收CMOS 图像传感器模块输出的模拟信号时,先通过具有缓冲作用的电压跟随器,随后经过可平衡差分输入的全差分运算放大器,从AD(analog digital)转换器输出16 bit的数字信号至FPGA 核心板模块中;FPGA 核心板模块对数字信号进行有效地缓存与处理后,在视频输出模块将数字信号通过Cameralink 采集卡传输到上位机,实现Cameralink 接口输出。整个系统的总电源幅值为12 V,系统供电模块则是通过电源芯片的转换以满足各个模块的供电需求,整个成像系统结构框图如图2 所示。

2 硬件电路设计

本项目硬件电路围绕EBAPS 传感器、FPGA核心处理器开展系统的硬件设计。依据模块化的设计理念,硬件电路设计主要包括系统电源板、探测器驱动板、FPGA 核心板、视频输出板,通过合理的器件选型、外围电路设计、PCB 绘制和调试完成各电路板的预设功能。

2.1 系统电源板

系统电源模块负责各个模块的供电工作,是设计电路能否正常工作的基础与保障。根据DCDC(direct current-direct current)电源芯片转换效率高、输入电压范围宽,LDO(low drop-out)电源芯片稳定性好、负载响应快、效率低等特点,结合各模块供电需求,本设计采用矽力杰的DC-DC 开关电源SY8113 和圣邦微LDO 电阻分压电源芯片SGM2028。在原理图设计时,为避免供电电源引起串扰,电路采用单独供电的方式;为减小电压波动,芯片输出端采用串联钽电容的方式稳定信号。系统电源模块供电方案如图3 所示。

图3 系统电源模块供电方案Fig.3 Power supply scheme of system power module

2.2 探测器驱动板

探测器驱动板包含图像传感器模块和模数信号转换模块。UV1280 芯片是图像传感器模块的核心器件,该芯片有9 路数字驱动信号线、2 路模拟差分信号线;模数信号转换模块核心芯片为AD转换器。本设计中,AD 选择的是芯佰微的16 位模数转换器CBM92AD68-80,其采样率为80 MSPS。为了保证图像信号的稳定,本设计采用杭州瑞盟的MS8617M 电压跟随器和华芯微的HRF8138M差分放大器完成信号的缓冲和放大。

2.3 国产FPGA 核心板

现场可编程门阵列(FPGA)是一种可编程的半定制电路,可通过编写硬件逻辑语言完成数据信息存储与处理。本系统选用复旦微电子FMK50 系列FPGA 的芯片,该芯片具有52 k 逻辑单元、120 个计算单元、250 个User I/O、4 个通用高速收发器,与市面上具有相同可编程逻辑资源的主流FPGA相对比,该芯片功耗更低,性价比更高。在数据存储方面,为稳定数据信号以及提高图像质量,FPGA核心板模块设有西安紫光国芯半导体的DDR(double data rate)芯片HXI15H4G160AF-13K 用于图像缓存,兆易创新的FLASH 芯片GD25S512MD 用于数据存储。根据设计要求,本项目基于复旦微FMK50T4-FPGA 芯片完成核心板设计,该核心板上设有主、从FPGA,为保证两片FPGA 芯片之间可进行高速无损数据通信,在PCB(printed circuit board)设计时,着重确保信号线等长、等间距。

2.4 视频输出板

视频输出模块使用Cameralink 视频输出方式[10],采用85 MHz 时钟频率。Cameralink 芯片采用成都振芯科技的接口控制芯片GM8283,该芯片具有宽时钟频率范围10 MHz~90 MHz,可将并行输入的28 bits LVCMOS(low-voltage CMOS)数据和1 bit 时钟信号转为5 路串行通道输出。电路中信号线多为差分信号,为解决输出差分信号极性相反、差分阻抗不变且抑制共模干扰等问题,在PCB 设计中遵循等长、等间距的设计原则。硬件电路实物如图4 所示。

图4 关键硬件电路实物图Fig.4 Physical drawing of key hardware circuits

3 逻辑设计

3.1 逻辑设计框架

FPGA 逻辑设计含CMOS 驱动模块、AD 配置模块、数据处理模块、视频输出模块。逻辑设计框图如图5 所示。

图5 逻辑设计框图Fig.5 Block diagram of logic design

CMOS 驱动模块是整个逻辑设计中的起始端,该模块使用Verilog 语言编写传感器9 路数字驱动信号的方式完成驱动,CMOS 输出的差分数据通过电压跟随器和差分运算放大器后进入AD 芯片进行模数转换。在AD 配置模块,信号在FPGA 内部进行对齐测试训练后方可进入正常工作模式,AD 芯片将2 路差分模拟信号转换成16 路并行数字信号,传输至FPGA 芯片进行数据处理。根据硬件电路设计和数据流的流向,主FPGA负责与前端CMOS 进行交互,从FPGA 负责后端显示模块的输出,主、从FPGA 则通过握手机制完成信息交互。在数据处理模块,数字信号先进入写FIFO(first input first output)完成位宽转换、跨时钟域的操作,然后使用AXI4 总线协议配置MIG(memory interface generators) 核的方式,使数字信号在DDR 中完成缓存和图像处理算法复现的读写操作。视频输出模块,即Cameralink 显示模块,通过GM8283 芯片完成并串转换操作,实现上位机与FPGA 之间的通信。

3.2 自适应曝光算法

曝光程度是相机能否呈现清晰图像的重要影响因素。曝光是由光圈大小、曝光时间、ISO 感光度三者共同决定,其中,光圈大小影响进光量,曝光时间是光到达的时间长度,ISO 感光度是增益大小[11]。自动曝光的宗旨是通过调整这三者以改变图像亮度。图像亮度Y组成如(1)式所示:

式中:k为常数;E为环境照度;(D/f)2为相对孔径,是光圈系数的倒数;T为曝光时间;G为感光度。

在FPGA 硬件实现时,考虑到环境因素、相对孔径、探测器内信号增益大小等不宜使用FPGA实现控制,故设计了一种调整曝光时间T的自适应曝光算法。结合EBAPS UV1280 的芯片手册,有效曝光时间由9 路驱动信号中的VSYNC 信号的占空比设置,故探测器最大曝光时间为一帧图像的时间。该算法以平均亮度算法为参考完成自动曝光操作,因系统输出为黑白图像,故图像灰度和图像亮度两者数值相同,利用当前帧的平均像素信息,并结合恒定步长搜索法以调节下一帧的曝光时间,经过不断优化后使得最终输出的图像平均灰度处于最佳亮度范围[Ymin,Ymax]。通过大量的实验测试,得出本系统在低照度环境下的最佳亮度范围为[24 000,25 600]。设置初始曝光时间为Tdefault,如果平均灰度数值正处于最佳亮度范围,则曝光时间将保持初始值;如果平均灰度值超过最佳亮度,则曝光时间将自动减少标准步长;如果平均灰度值不足最佳亮度,则曝光时间将自动增加标准步长。曝光时间T的计算公式如下:

最大曝光时间Tmax的计算公式如下:

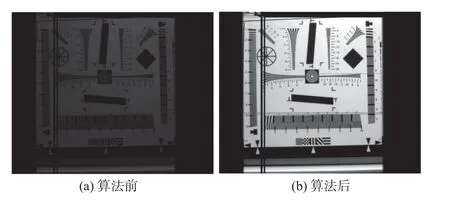

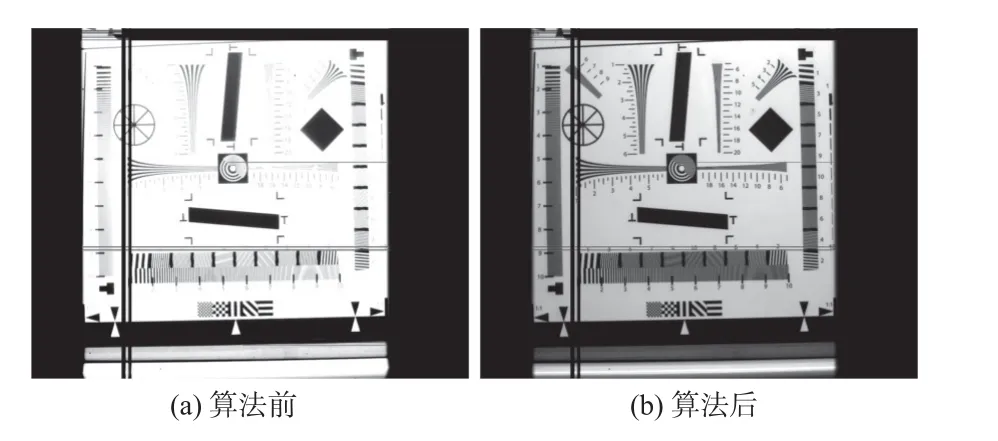

式中:s表示标准步长;m表 示横向像素数;n表示纵向像素数;f表示像素时钟频率。像素时钟频率为40 MHz,标准步长为640 000 ns,根据计算,该系统的最大曝光时间Tmax为32 768 000 ns,最小曝光时间Tmin为1 000 000 ns,初始曝光时间Tdefault为16 384 000 ns。若增加步长后的曝光时间超出曝光范围,最终的曝光时间将设为最大曝光时间;若减少步长后的曝光时间不足曝光范围,最终的曝光时间将设为最小曝光时间。图6、图7 为自动曝光算法前后EBAPS 成像效果图。

图6 不足曝光时算法效果图Fig.6 Algorithm effect diagram when underexposed

图7 过度曝光时算法效果图Fig.7 Algorithm effect diagram when overexposed

3.3 帧间噪声抑制算法

噪声是影响图像质量水平的重要因素。CMOS图像传感器噪声主要分为固定模式噪声(fixed pattern noise,FPN)和随机噪声两类[12-18]。固定模式噪声是CMOS 传感器自身结构特点所产生的。CMOS 输出图像信息如(4)式:

式中:CMOS_OUT为采样的真实图样信息;Ori_ph为不含噪声的理想图像信息;Temp_n为像素随机噪声;FPN_n为暗电流FPN[15-18]。

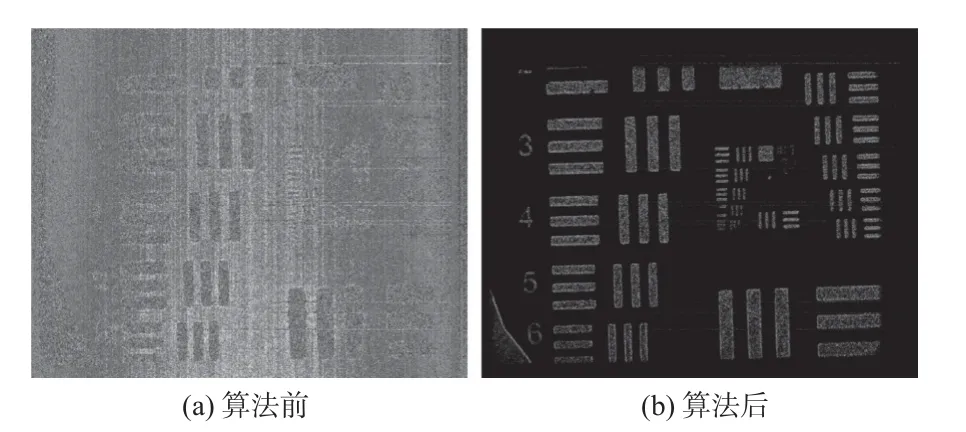

根据EBAPS 的成像特点提出帧间噪声抑制算法,该算法主要是去除低照度环境下图像的固定模式噪声FPN_n,采用实时图像与暗背景图像线性相减的方式实现。本算法采用AXI4 总线协议控制MIG 核的方式,在DDR 中开辟了5 片大小为1 280×1 024×2 Bytes 地址空间,前4 片地址用于存放4 张连续的无光照环境下的暗背景图像,最后1 片地址用于存放实时图像,通过对“KEY=1”的判断来进行写入地址的选择。将前4 片地址中的4 帧图像进行对应图像位置的像素值求平均计算,得到最接近真实的暗背景图像信息,实时图像中固定模式噪声的去除,采用前4 片平均像素值的暗背景图像与第5 片地址的实时图像之间进行线性相减的方式完成,由此可近似得到固定模式噪声去除后的图像。去噪算法逻辑设计框架如图8所示。算法实现中的重点是对DDR 地址跳变的控制和数据对齐的把控。在DDR 地址控制方面,需先配置好读写文件中的地址与数据通道相关参数设定,控制好5 片地址的起始地址AXI4_AWADDR,以及每次数据传输的突发长度。

图8 去噪算法逻辑设计框架Fig.8 Logic design framework of denoising algorithm

在S2MM 写操作时,数据在进入DDR 前,会先进入FIFO 进行跨时钟域变换与位宽转换,当FIFO 的prog_empty 信号为拉低状态时,即可继续进行突发式写操作,同时拉高地址通道的AXI4_AWVAILD 信号;等待MIG 核反馈的AXI4_AWREADY信号,如果该信号同时处于拉高状态,即可完成一次地址握手。每完成一次地址握手,地址位将增加一个BRUST 的长度,等待下一次地址握手。当地址握手和数据握手均完成时,即可完成一个地址的突发式数据写入。以此类推,直至一幅图完全写入DDR 地址中。使用以上方式完成5 片地址的图像写入,其中通过判断“KEY=1”真假选择写入的地址信息,“KEY=1”为真,则写入前4 片地址;“KEY=1”为假,则写入第5 片地址。式(5)为AXI4 总线中地址位的表达式:

式中:ADDR_BIAS为基地址;ADDR_offset为偏移地址,用以控制写入不同图像的起始地址;address_r表示一次BRUST 的长度。

在MM2S 读操作时,数据需要通过FIFO 进行跨时钟域与位宽转换后进入显示模块。其中,将4 片地址上平均黑图像素值black_data与图像像素值normal_data作差之前,需要先通过设置相同的FIFO 读出信号rd_en,使两个像素值一一对应。至此完成图像算法的全部内容,图9 为帧间噪声抑制算法前后EBAPS 成像对比图。

图9 算法前后EBAPS 成像对比结果Fig.9 Comparison results of EBAPS imaging before and after algorithm

4 测试结果分析与讨论

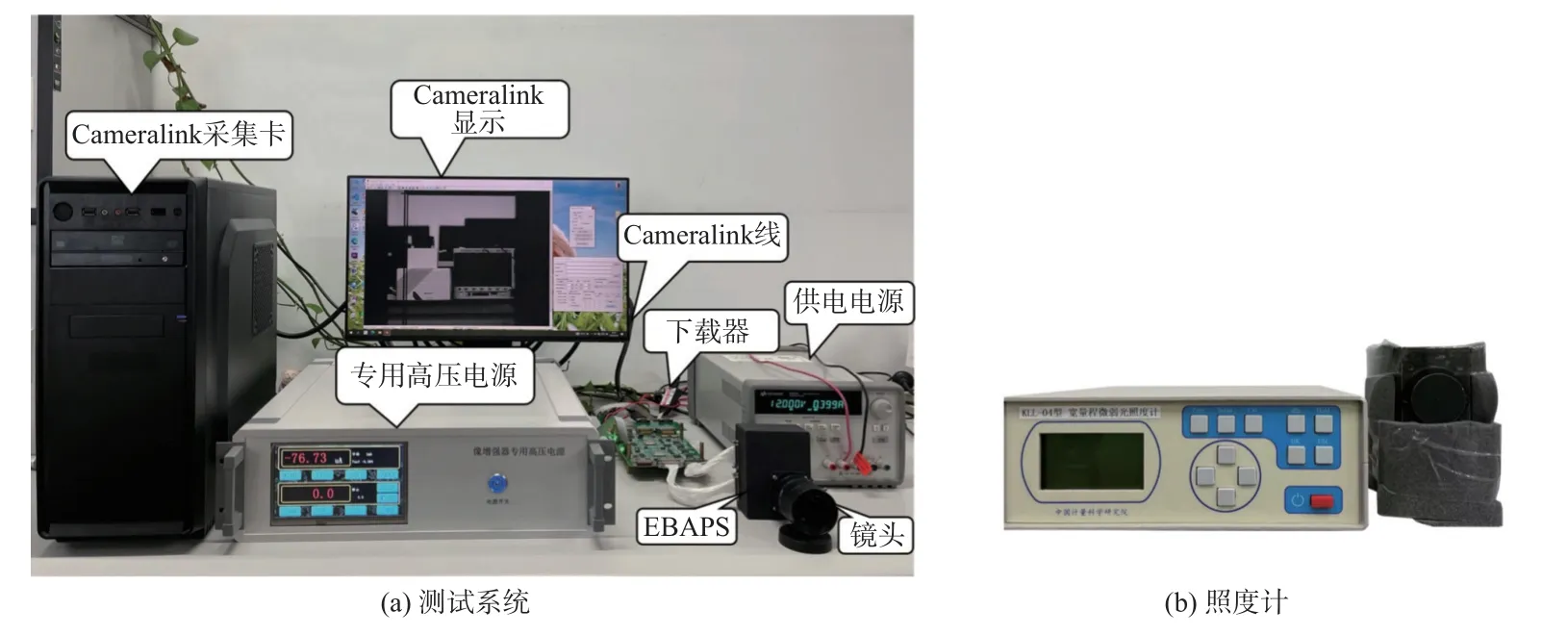

基于上文所述硬件电路与逻辑电路设计,完成EBAPS 国产成像电路的设计与组建。为测试该成像电路的成像效果,组建了与之功能配套的成像检测系统,设计了EBAPS 高压轰击测试方案,图10 给出了实验测试设备系统实物图,该系统包含光学镜头、成像电路、可调式恒流源、微弱光照度计、Cameralink 采集卡、专用上位机等。EBAPS是电子轰击型有源像素传感器,需在光阴极和APS 芯片之间加一个负高压以实现电子倍增,测试系统为其准备了专用高压电源。实验中的环境照度、轰击电压均可进行调节。在整机正常工作情况下,硬件电路功耗为4.8 W,逻辑设计电路片上功耗为1.261 W,其中,动态功耗1.185 W、静态功耗0.076 W。

图10 测试系统结构组成实物图Fig.10 Physical drawing of structure composition for test system

为进一步提高EBAPS 成像系统的成像效果,感光器件获得合适的曝光量,使所摄物体呈现正常亮度,增设自动曝光算法,对不同高压、环境照度条件下的图像进行采集和对比。实验采集0~1 500 V 范围内的EBAPS 成像图,为方便结果对比,选取0 V、-500 V、-1 000 V、-1 500 V 作为代表性结果。图11 所示图像为自动曝光算法和帧间噪声抑制算法综合后的效果图。

图11 可变高压下的EBAPS 成像图Fig.11 EBAPS imaging images under variable high voltages

从图11 中可以看出,除了因EBAPS 器件工艺原因形成的明显横条纹存在以外,在自动曝光算法和帧间噪声抑制算法下,已可以呈现出较清晰的图像。图11 中横向对比是环境照度的变化,纵向对比是高压伏值的变化,展示了在不同环境照度和高压值时,国产EBAPS 成像电路的成像效果。其中,在不加高压、3×10-1lx 照度下,图像已基本无物体的轮廓特征。根据图11 中第3、4 行前两幅图可看出:在相同高压的情况下,自动曝光算法在调节不同环境照度下图像亮度时,有一定成效;EBAPS 器件加以合适的高压后,即使在低照度环境下仍可识别图像,并且在轰击电压设为-1 500 V时,3×10-3lx 环境照度下仍可成像。根据实验结果,可以得出,本系统已实现了EBAPS 的国产电路成像的基本功能。

5 结论

为加快EBAPS 器件成像电路的国产化进程,本文设计了一套基于EBAPS 的国产成像电路评估板。首先,以国产复旦微FMK50t 系列的FPGA 芯片为核心,通过器件选型、外围电路设计、PCB 绘制搭建了系统的硬件平台;其次,通过逻辑设计完成探测器驱动、图像缓存、Cameralink 显示,初步完成EBAPS 图像显示功能;最后,设计了自适应曝光算法、帧间噪声抑制算法改善图像质量,实现了EBAPS 图像传感器在3×10-3lx 低照度环境下的实时显示。实验证明,该成像电路整机功耗4.8 W,可以有效去除固定模式噪声,改善成像质量。下一步工作将从低功耗、小型化角度对电路进行优化。本文设计的EBAPS 国产成像系统,可为EBAPS器件的国产成像电路设计提供参考。