印制电路板弯曲绕线对信号传输时延影响的研究

毛忠宇 叶 子

(1.深圳市电巢科技有限公司,广东 深圳 518057; 2.威凯检测技术有限公司,广东 广州 510663)

0 引言

印制电路板(printed circuit board,PCB)高速并行总线通常是由多根数据信号基于同一个时钟进行采样。对于双倍数据速率(double data rate,DDR)类的数据,在每个时钟周期可能要采样2 次或以上,从DDR1 到DDR6,随着芯片数据采样频率越来越高,数据信号采样时所需要建立及保持的时间窗口越来越小。在PCB 设计中,信号传输延迟部分对时序余量影响的比重越来越大。为保证在数据采样点能正确采集到所有信号的值,采用了多种不同技术,如斜率补偿技术、PCB 走线等长等。其中,使用PCB 走线物理等长的设计以控制信号传输的延迟,是PCB 设计中最常见的方法。将1 组总线设计成物理等长的目的是为了尽可能减少所有相关信号在PCB 上传输延迟的差异,获得最大建立与保持时间,最终使时序满足总线的要求。

在实际工程中,由于受PCB 层数及布局布线区域限制等诸多因素的影响,要实现PCB 走线等长,最常用的方式就是对PCB 走线进行绕线(又称蛇形布线)处理。蛇形走线主要是为了使1 组总线的物理走线中,将较短的线在有限空间中通过绕线方式实现等长。高速电路设计时需要考虑信号完整性(signal integrity,SI),蛇形线之间有距离要求,如距离过近,因耦合较强会导致蛇形线的时延达不到要求,使信号的质量变差。即使在PCB 上的布线实现了物理等长,如绕线的方式不一样,实际时延也不一样。

本文通过仿真与测试比较的方式,证明PCB上蛇形绕线的方式不一样时,实际的时延结果也不一样,同时还发现SI 仿真的时延结果与实际的测量结果较为一致,说明SI 仿真结果可用来指导PCB设计时信号的绕线。

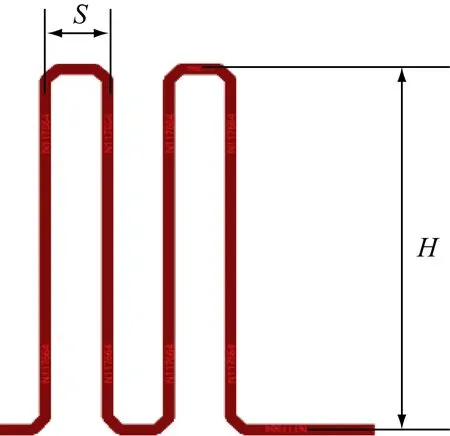

典型的PCB 蛇形绕线如图1所示。蛇形走线对信号传输影响的因素中最关键的参数有2 个,分别为平行耦合高度(H)和耦合距离(S)。

图1 蛇形绕线形状中的长度H与线间距S示意

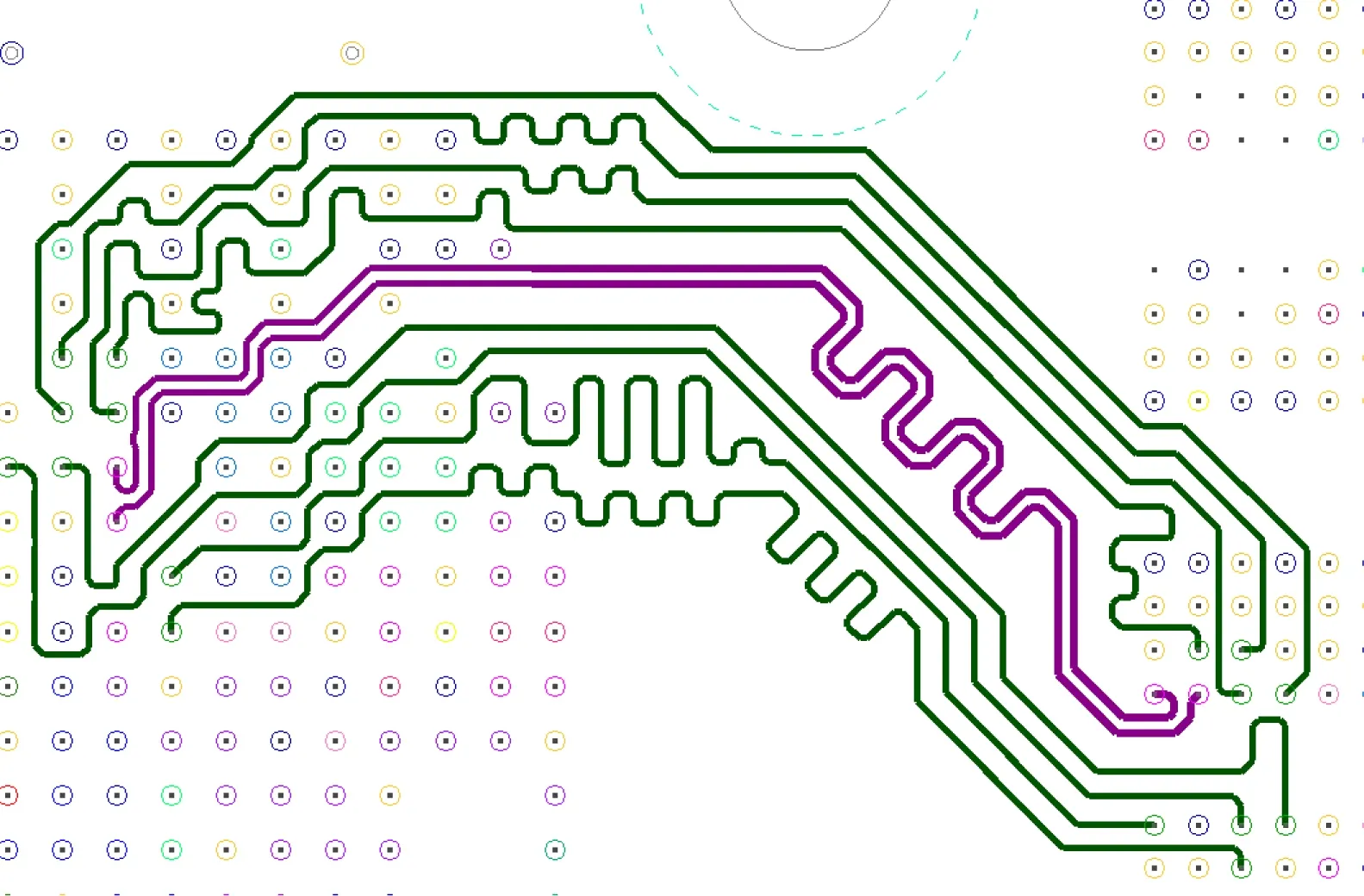

某 产 品DDR5 数 据 信 号(DATA0~DATA7)PCB 布线如图2所示,最终效果受PCB 层数及布局布线区域限制等诸多因素影响。由图2 可知,此类弯曲绕线的高度间距差别较大,但网络总PCB 走线长度一样。本文将研究这类不同高度及间距的弯曲绕线对实际信号时延的影响。

图2 DATA0~DATA7的PCB弯曲绕线效果

2 理论分析

数字信号在PCB 布线间存在能量相互耦合的现象非常普遍,这种能量耦合也称之为串扰。如在数字信号链路中的芯片内部走线、封装的接合线及基板布线、连接器以及PCB 布线间由于能量的耦合都会产生串扰。

串扰会对信号传输造成一定的影响,如:① 使传输线的有效特性阻抗和传播速度发生改变,这些改变会影响系统时序及SI;② 在其他传输线上感应出噪声,会影响SI,使信号的电平裕量减少。

传输线链路中串扰的影响因素主要有信号码形、布线长度、布线间距、信号沿等。本文主要研究蛇形走线区域线段间串扰引起的时延影响。

2.1 互容与互感

2 根传输线的简单模型如图3所示,上面1 根是加了脉冲源的攻击线,下面1 根则是两边加了匹配的静止线。它们间的互容及互感分别用Cm及Lm表示。

2.1.1 互容Cm

2根导线通过电场产生的耦合即为互容,互容是引起串扰的其中一个原因。驱动传输线由于电场激发,通过互容在受害传输线上感应出电流,该电流与驱动传输线上的电压变化率成正比,互容感应到的噪电流表示为

式中:Inoise,Cm为受害线上产生的噪声电流;Cm为相邻2 根导线间的互容;dVdriver为攻击线上电压的跳变幅度;dt为攻击线上电压由低电平到高电平跳变所用的时间。

2.1.2 互感Lm

驱动传输线通过磁场耦合为互感Lm,Lm是引起串扰的另一个原因。Lm由驱动传输线通过磁场会在受害线上感应出电压,引起电压噪声,电压噪声与驱动传输线上的电流变化率成正比,互感感应到的噪电压表示为

2.1.3 电感矩阵和电容矩阵

对于多根平行的传输线,互感与互容间的关系会变得非常复杂,此时要完全评估传输线的电气特性,需分别计算表示传输线间的互感与互容,电感矩阵表示为

式中:LNN为传输线N自身的电感;LMN为传输线M与传输线N之间的互感。

电容矩阵表示为

式中:CNN为从导线N看过去的总电容,该电容值等于导线N的接地电容,再加上导线N对其他导线的总互容。

2.1.4 串扰导致的时延

当多根传输线在较强耦合范围内高低电平转换时,传输线之间的电场和磁场的影响将变得更加复杂,其信号高低电平转换决定了它们会以何种模式传输,这些特定的数据码模式能够有效地减少或增加传输线上的有效寄生电感和电容。不同的传播模式会改变传输线有效的特性阻抗和传输速率,特别是当很多靠近的传输线同时切换时,这种现象尤为严重,会使总线出现特性阻抗和延迟时间产生变化,影响总线的电性能。传播主要分为奇模及偶模。

(1)奇模。当2 根耦合传输线由幅度相同、相位相反的信号驱动时,其传播模式为奇模。传输线的有效互容将在传输线接地电容的基础上加上互容;传输线的等效电感将在传输线自感的基础上减去互感。此时传输线的等效电容增大,但等效电感变小。2 相邻传输线在奇模传输模式下,传输线特征阻抗和传输速率的变化情况如图4所示。

图4 奇模下电感与电容的等效电路

利用基尔霍夫电流定律(kirchhoff’s current law,KCL)与基尔霍夫电压定律(kirchhoff’s voltage law,KVL)导出等效公式,从走线1 看到的等效电容表示为

式中:Codd为奇模下2根导线间的等效电容;Cm为2 根导线间的互容;C1g为导线1 对地的电容;C11为导线1的自容。

等效电感表示为

式中:Lodd为奇模下2 根导线间的等效电感;Lm为两根导线间的互感;L12为导线1 对导线2 的互感;L11为导线1的自感。

奇模模式中1对耦合传输线的等效阻抗为

式中:Zodd为奇模下传输线的等效阻抗;Lodd为传输线奇模等效电感;Codd为传输线奇模等效电容;C11为导线1的自容。

奇模时延表示为

式中:TD为奇模下传输线延时。

(2)偶模。当2 根耦合传输线由幅度、相位相同的信号驱动时,其传播模式为偶模。传输线的有效电容将在传输线自身电容的基础上减去互容;传输线的等效电感将在传输线自感的基础上加上互感。2相邻传输线在偶模传输模式下,传输线特性阻抗和传输速率的变化情况如图5所示。

图5 偶模下电感与电容的等效电路

再利用KCL 与KVL 导出等效公式,走线1 的等效电容表示为

式中:Ceven为偶模下2 根导线间的等效电容;C12为导线1对导线2的互容。

等效电感表示为

式中:Leven为偶模下2根导线间的等效电感。

偶模模式中1 对耦合传输线的等效阻抗和传播时延表示为

式中:Zeven为偶模下传输线的等效阻抗。

偶模时延表示为

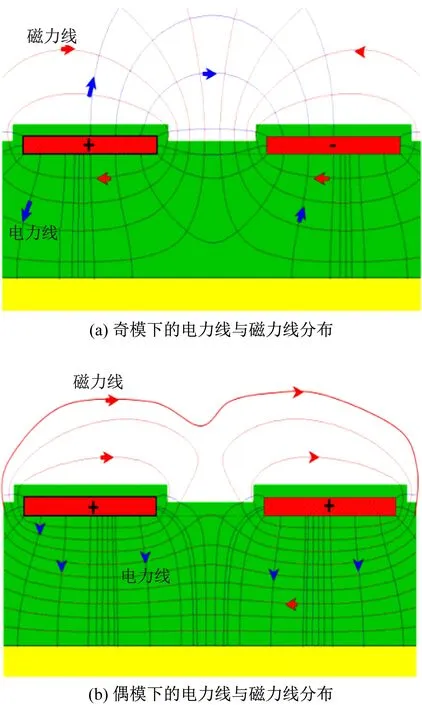

(3)奇、偶模电磁场磁力线状态。简单双导线系统中的奇、偶模的磁力线及电力线分布状态如图6所示。

图6 奇、偶模电力线及磁力线的分布

磁力线和电力线总是正交,即电磁波的电场和磁场都是垂直于传播方向的平面上的一种电磁波(transverse electric and magnetic field,TEM)。偶模传播时,2条导线的电势相同,由于两者之间没有电势差,因此传输线间不会产生电容效应,偶模时要从总电容中减去互容;奇模传播时,2条导线的电势相反,因此传输线间存在电容效应,奇模中要加上互容。

奇、偶模会使传输线的阻抗和传播速度发生变化,影响传输线上信号传播。以3 根耦合平行传输线建立一个模型,使用SI仿真工具(如ADS/Hspice软件)进行仿真并观察结果。

仿真原理图由3 根耦合平行传输线组成,分别使用3 个幅度及上沿相同的脉冲激励接发送端,在传输线2 端分别接入50 Ω 电阻,测量点在中间传输线的V-Probe 处,如图7所示。仿真时分3 种情况:①V1,V3没有激励,分别接到地,V2处使用激励,在V-Probe 处测到波形为Far_n。②V1,V3使用偶模激励,V2处使用原激励不变,在VProbe 处测到波形为Far_e。③V1,V3使用奇模激励,V2处使用原激励不变,在V-Probe处测到波形为Far_0。仿真结果如图8所示。

图7 奇、偶激励对传输线影响的仿真原理结构

图8 奇、偶模型对同一信号传输时延的影响仿真

在图8 中,Odd mode 所指的图形为受两边相邻的导线为奇模激励时,中间信号线受到影响,在远端测到信号波形。Even mode所指的图形为受两边相邻的导线为偶模激励时,中间信号线受到影响在远端测到的信号波形。Single trace 信号线是指两边相邻的导线不设激励而接地时,中间信号线受到影响在远端测到的信号波形。

由中间信号在远端测试的时延得知,SI 和传播速度到奇、偶模式的串扰影响较明显,因此使用奇、偶模模式激励时,对同一信号传播时延会不同。

对于同一网络使用蛇形布线的情况如图9所示。图中,虚线内截取的部分区域为多根传输线的情况,使用以上的分析方法,结论完全一致,由于同一网络的蛇形走线区域的传输线段电流方向组成了复杂的奇偶模型,时延会受到一定影响。

图9 蛇形走线局部等效奇、偶模式示意

3 测试与仿真比较

3.1 实验样板

测试使用的PCB 实验样板参数:4 层;板厚1.54 mm;完成板厚(1.6±0.2)mm;阻抗为 50 Ω。叠层与材料参数见表1。

表1 层叠与材料信息

实验样板的设计如图10所示,共设计4 个网络,分别命名为T1、T2、T3、T4。经过弯曲绕线后它们的总长度相等,长度均为127 mm。其中,T1 为直线布线;T2 为类似于三角形的布线;T3线宽为0.31 mm,弯曲部分间距S为0.62 mm,线高为12.7 mm;T4线宽为0.31 mm,弯曲部分的间距S为0.93 mm,线高为12.7 mm。

图10 PCB测试样板布线

对以上4 根PCB 布线,通过时域传输测试(time domain transmission,TDT)法进行测量且读取时延数值。为了比较的一致性,测试环境如下:设置1 个100 ps、200 mV 的上升脉冲,在接收处测量100 mV 电压时对应的时间是信号在PCB走线上的时延数据,如图11所示。

图11 测试时延示意

为了后面的测试与仿真比较,同时还测试了4 根网络的S参数,所用仪器为E5071C,扫描范围为300 kHz~20 GHz。

3.2 样板仿真

以上数据可通过对样板的测试获得,但在实际工程中,由于弯曲绕线时的情况太多,设计及测试每种弯曲绕线情况需要大量的资金、人力及时间的投入,无法对每种情况都投一块板进行测试,因此需要一种预测的方法对实际的弯曲绕线等长进行评估,指导PCB 弯曲绕线,在最短时间内进行成本最小的迭代优化。

最常用的做法是通过对测试板使用3D 电磁场仿真软件建模仿真,将仿真结果与测试的结果进行比较,再对仿真设置条件及被仿真对象的材料参数进行修改,获取1 组有效的工程数据及仿真方法。在后期工程设计时,通过调用前面实验得到的经验参数仿真,便可得到与实际PCB 后测试时相近的结果或趋势。

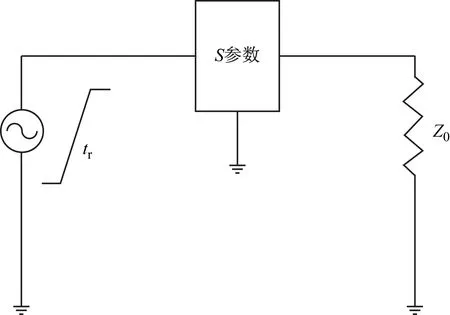

通过3D 电磁场仿真软件对4 根网络进行仿真,分别提取出4 根网络的S参数,得到的S参数与前面测试样品的S参数,最后放在一起加入与TDT 测试时相同的上升沿信号作为激励,比较实测数据与仿真数据的时延情况。仿真时的网络连接方法如图12所示。

图12 使用S参数仿真获取信号经布线后时延连接

3.3 结果比较分析

对4 根网络的测试结果与仿真结果时延进行比较,具体数据见表2。

表2 测试与仿真时延比较

由表2 可知,当PCB 布线做弯曲绕线处理时造成的时延情况为:测试数据T1>T2>T4>T3,仿真数据T1>T2>T4>T3。没有弯曲绕线的PCB 布线时延最长,当出现部分弯曲绕线时使时延变小(并非4 个不同网络同时加激励使用奇偶模式,而是同一个网络由自绕弯曲在弯曲处自形成的复杂奇、偶情况),变小的情况与弯曲绕线时的间距S、高度H及形状有关。从弯曲绕线的形状及测试的时延值来看,弯曲绕线部分平行距离越大影响越小。仿真与测试的数据差值相对稳定,因此仿真结果对指导以后的设计有参考价值。

4 结论

本文对PCB 布线弯曲绕线等长进行研究,通过对4 个样本的实测数据验证,确认信号在弯曲绕线时,由于存在弯曲绕线的自耦合,对信号时延会产生影响,不同的弯曲绕线形状及弯绕部分间距S、高度H等影响也不同;趋势是弯曲绕线部分越靠近,自耦合越大造成的影响越大。

为指导以后的PCB 等长线设计,本文还对以上同一网络蛇形走线的网络建3D 电磁场仿真模型,进行参数提取及仿真,时延仿真的结果与测试的结果数据接近,趋势相同。因此,有时延严格要求的信号在PCB 布线时,如发生较多弯曲绕线,不能只看物理布线等长就认为时延相等,需进行SI 仿真,在工程实践中进行等长弯曲绕线处理,规则总结如下。

(1)如布线空间足够,对时序较为严格的高速总线应尽量避免通过蛇形走线的方式达到走线的等长。

(2)绕线时尽量增加平行线段的距离S(如常用的经验法测3W),可将相互的耦合效应降到最低程度。

(3)采用任意角度的蛇形走线,如图13所示的梯形结构,使布线不平行以有效减少相互间的耦合。

图13 梯形走线方式

(4)蛇形线总线设计成带状线(strip-line)结构时,其上的信号传输延时大于微带线(microstrip)结构。

(5)减小信号线间耦合长度,使耦合长度小于0.5倍上升时间的空间延伸(使近端串扰没有达到饱和)。

(6)尽量使上升沿快的信号靠近地平面或电源平面,这样可以使信号路径与平面紧密耦合,减少对相邻信号线的干扰,最好使高速信号夹在2个地平面之间。