基于HDL/FPGA 的步进电机驱动控制器设计*

段 简,张奕婷,郑晓峰,陈 磊,周 颖,钱 敏,2

(1.苏州城市学院电子信息工程系,江苏 苏州 215104;2.苏州大学电子信息学院电子科学与技术系,江苏 苏州 215006)

步进电机是一种应用范围广泛的驱动控制装置,其工作原理是将输入的电脉冲信号进行转换,使自身产生相对应的角位移或者线位移[1-2]。步进电机的角位移量或线位移量与步进电机接收到的脉冲数成正比,即输入的脉冲信号越多,步进电机的角位移或线位移就越多。而步进电机的转速则由输入脉冲的频率控制,输入的电脉冲信号的频率越高,步进电机的转速就越快。

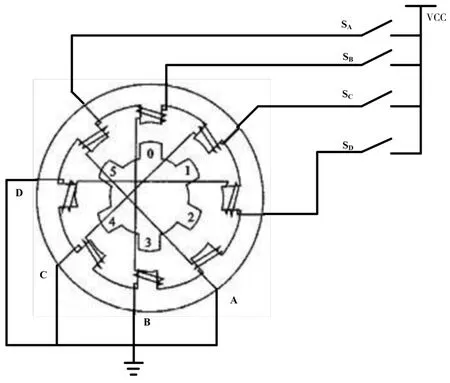

步进电机根据结构的不同,主要可以分为3 种类型,即反应式(VR)、永磁式(PM)和混合式(HS)[3]。本次设计所采用的步进电机是四相反应式步进电机,其示意图如图1 所示。

图1 四相反应式步进电机

与传统设计方法相比,采用基于硬件描述语言/现场可编程门阵列HDL/FPGA(Hardware Description Language,Field Programmable Gate Array)的EDA(Electronic Design Automation)设计方法设计数字系统有巨大的优越性,且已成为大规模集成电路设计中使用最广泛的一种方法。在控制驱动步进电机时,由于步进电机能直接接收数字量的输入来控制电脉冲,且电路设计比较简单,适宜采用HDL/FPGA 实现;通过FPGA 开发工具Quartus Ⅱ可以高效地进行编译综合、波形仿真、下载测试,从而能够简化设计、提升效率、实现功能模块化[3-4]。

1 步进电机的工作原理和驱动方式

如图1 所示,步进电机主要由2 部分组成:一个是定子,上面有几组缠绕着线圈的齿;另一部分是可自由转动的转子。定子有4 相绕组,转子上一共有6个齿。以电机的四相单四拍的通电模式为例,反应式步进电机的工作原理是利用了物理上的“磁通总是力图使自己通过的路径的磁阻最小”所产生的磁阻转矩,驱动电机发生转动。开始时,只有B 相绕组通电,由于电流在步进电机中产生一个穿过转子的磁场,而这个磁场将转子磁化,此时距离B 相最近的齿会被吸引,直到与B 相绕组对齐。由于图中0、3 号齿本就与B相绕组对齐,所以此时转子不发生转动。只有当C 相绕组通电时,因为距离C 相绕组最近的1、4 号齿未与C 相绕组对齐,所以此时在磁场的作用下,C 相绕组会产生一个吸引转矩,吸引距离C 相绕组最近的1、4号齿向C 相绕组靠近,即在磁场作用下,转子逆时针转动。当转子转动至1、4 号齿与C 相绕组对齐时停止。当只有D 相绕组通电时,因为磁场作用,2、5 号齿被吸引,转子发生转动。以此类推,通过不断切换通电的相,电机就能不停地转动。

除了电机每次单相通电的供电方式,即四相单四拍的通电方式之外,电机的四相绕组的供电方式还有四相双四拍和四相单、双八拍的通电方式。

四相双四拍的通电方式为:每次有两相相邻绕组接通电源,如A、B 相绕组通电而C、D 相绕组不通电。若初始状态如图1 所示,那么A、B 相绕组通电时,因为磁场作用产生的转动力矩,会吸引0、3 号齿与A、B 相绕组磁极的中间线对齐。当只有B、C 相绕组通电时,同理0、3 号齿应该与B、C 相绕组磁极的中间线对齐。以此类推可得到供电方式为四相双四拍时电机的转动状态。

本次设计采用的四相单、双八拍的通电方式为单相通电和双相通电交替进行的模式。这种模式将步进电机转动1 圈的拍数从4 拍变为8 拍,使步进电机每次转动的角度变为四拍状况下的1/2,即四相单、双八拍的步距角是单四拍或双四拍步距角的1/2。

当控制电机反转时,只需要将四相绕组的通电顺序改为与电机正转时的通电顺序相反即可。步进电机的步距角就是步进电机每转一次时转子转过的角度。步距角的计算公式为:

式(1)中:m为步进电机径向相对的绕组数,也就是相数;C为步进电机工作的拍数和相数的比值,即步进电机以单四拍和双四拍的通电模式工作时,C=1,而当步进电机以单八拍和双八拍的通电模式工作时,C=2;Zk为转子的小齿数,本次设计所使用的四相步进电机的转子小齿数为64。

因为步进电机经过一个1/8 的减速器引出,所以本次设计所使用的四相步进电机实际的步距角是=0.0879°。

2 步进电机驱动控制的实现

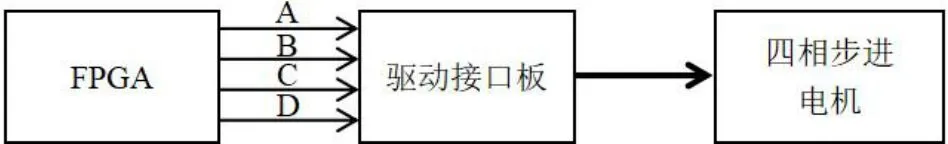

本次设计采用四相单、双八拍的通电模式来控制四相步进电机的转动,A、B、C、D 这4 个相的通电与否由4 路I/O 信号并行控制,即由FPGA 的四位I/O口输出4 路脉冲信号,分别控制四相步进电机的4 个相。FPGA 输出的脉冲信号经过功率放大之后,进入步进电机的各相绕组[5],由此便实现了由FPGA 输出的脉冲信号直接控制步进电机的驱动,而不再需要脉冲分配器来对输入的电脉冲信号进行分配。图2 为四相步进电机与FPGA 板的连接示意图。

图2 四相步进电机在开发板中的接法

按照四相单、双八拍的控制方法来驱动四相步进电机进行正转时,电机四相绕组的通电顺序依次为A→AB→B→BC→C→CD→D→DA。高电平为接通电源,低电平为不接通电源,容易得到在控制电机正转时,FPGA 四位I/O 口的值,如表1 所示。当电机反转时,4 个相的通电顺序与电机正转时的通电顺序相反,即通电相序为A→DA→D→CD→C→BC→B→AB,此时FPGA 四位I/O 口的值应与电机正转时四位I/O 口输出值的顺序相反。

表1 电机正转时FPGA 四位I/O 口的值

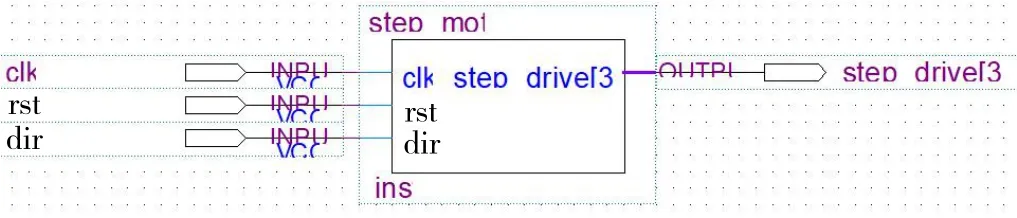

因为步进电机需要完成正转和反转2 种工作,所以控制四相步进电机不仅需要能驱动电机转动的电脉冲信号clk,还需要复位信号rst 和控制电机正反转的方向信号dir。步进电机的原理图如图3 所示。

图3 设计原理框图

本设计采用Ve r i l o g H D L 的编程方法,在Quartus II 9.1 软件中实现步进电机驱动控制电路的搭建、编译和波形仿真等工作。其中,实现主要功能部分的代码如下:

if((clk==1” b1))

begin

StepCounter<=StepCounter+31” b1;

if(StepEnable==1” b1)

begin InternalStepEnable<=1” b1; end

if(StepCounter>=StepLockOut)

begin

StepCounter<=32” b0;

if(InternalStepEnable==1” b1)

begin

InternalStepEnable<=StepEnable;

if(Dir==1” b1)

begin state<=state+3” b001; end

if(Dir==1” b0)

begin state<=state-3” b001; end

case(state)

3” b000: begin StepDrive<=4” b0001;end

3” b001: begin StepDrive<=4” b0011;end

3” b010: begin StepDrive<=4” b0010;end

3” b011: begin StepDrive<=4” b0110;end

3” b100: begin StepDrive<=4” b0100;end

3” b101: begin StepDrive<=4” b1100;end

3” b110: begin StepDrive<=4” b1000;end

3” b111: begin StepDrive<=4” b1001;end

endcase

end

end

end

代码主要实现了驱动电机时四位I/O 口的8 种输出状态,以及通过方向控制变量dir 来控制电机的正转和反转。当通过使用条件语句时,state 的值为000~111,分别对输出变量step_drive 进行赋值。state 的值一共有8 个,每个值对应着步进电机4 个相的不同通电状态,当控制方向的变量dir 为1 时,电机正转,state的值按照上面代码所展示的从上到下的顺序依次变化;而控制方向的变量dir 为0 时,电机反转,state 的值按照从下到上的顺序依次变化。

3 波形仿真与下载测试

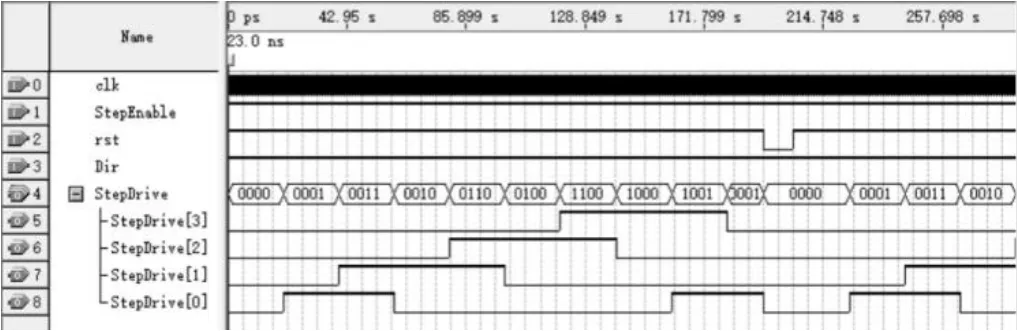

利用Quartus II 9.1 软件对整个步进电机驱动控制器设计HDL 代码并进行波形仿真。

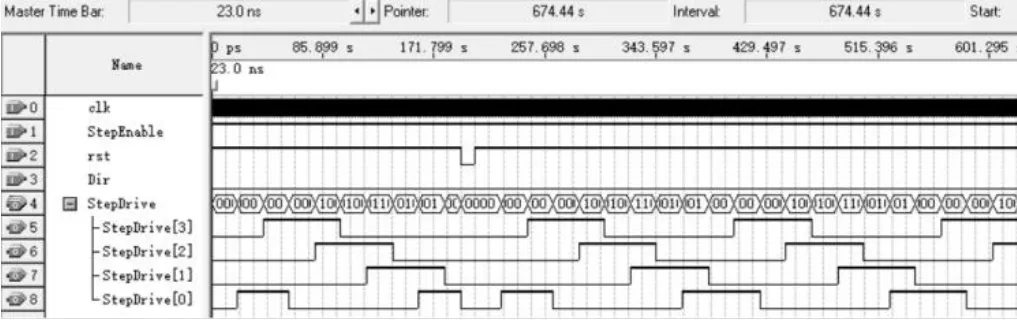

图4 为电机正转时FPGA 四路I/O 口的输出波形及接收到复位信号后的输出波形。其中clk 为控制电机转动的电脉冲信号;StepEnable 为控制电机是否工作的使能端,在进行波形仿真时,StepEnable 一直处于置1 状态;rst 为复位信号,置1 时电机正常运转,置0 时电机复位;dir 为方向信号,当dir 的值为1 时,电机正转(逆时针旋转),当dir 的值为0 时,电机反转(逆时针旋转)。

图4 电机正转时输出波形及复位后波形

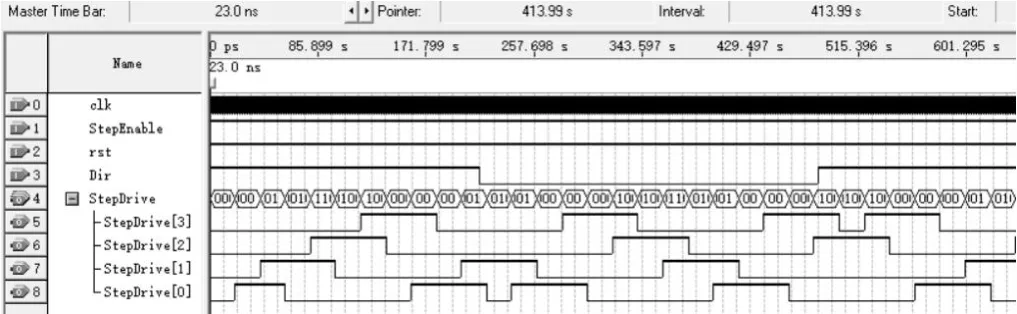

电机反转时的FPGA 的四路I/O 口的输出波形如图5 所示,FPGA 四路I/O 口数值为0001,即步进电机反转时第一个状态为A 相通电,随后四路I/O 口输出波形和表1 所描述的相反。当接收到复位信号时,四路I/O 口的值变为0000,然后重新从0001 开始。即当步进电机接收到复位信号以后,步进电机的4 个相均不通电,然后重新从A 相通电的状态开始,步进电机重新开始旋转。

图5 电机反转时的输出波形及复位后波形

当实现控制步进电机进行正反转状态切换的功能时,FPGA 的四路I/O 口的输出波形如图6 所示。当方向信号dir 的值由1 变为0 时,四路I/O 口的值为0011,在下一个使电机旋转的电脉冲信号到达后,四位I/O输出的值变为0010,即电机由正转变为反转的状态。所以在控制电机在从正转变为反转(或反转变为正转)时,电机保持现有的状态,等下一个控制电机旋转的脉冲信号到来时,电机变为反转状态(正转状态)。

图6 电机正反转切换时的输出波形

通过波形仿真结果,验证了步进电机驱动控制器设计程序的功能,即能够控制电机进行正转、反转、复位及正反转状态的切换。经过下载测试,与仿真结果相符,达到了设计要求。

4 结束语

本文介绍了使用Verilog HDL 对步进电机的驱动电路进行描述,利用Quartus II 软件对Verilog HDL 设计程序进行逻辑功能的验证,最终通过FPGA 开发板下载测试,完成了对步进电机驱动控制的实际功能的验证。

本次设计主要围绕控制步进电机进行正转、反转、在正反转时进行复位和切换及控制转速等功能进行研究,充分利用了硬件描述语言HDL 较传统方法设计简单、易于验证、自上而下的优点,在实际应用中可根据要求灵活改变,以适用于不同场合。