面向系统能力的数字逻辑与数字系统课程实践教学改革

魏继增,王建荣,李幼萌,于永新,王 立,罗 韬

(天津大学智能与计算学部,天津 300354)

0 引言

自2018 年4 月以来持续发酵的“华为/中兴事件”再次表明以处理器为核心的各类芯片是构建整个IT产业的核心基础,是影响“自主可控”国家信息产业战略实施的关键[1-3]。但目前我国高校的计算机相关专业在学生培养上往往更加关注的是算法和应用的研究,而真正的计算机系统设计创新人才极度匮乏,其原因是缺乏对学生进行系统能力的培养。所谓系统能力,是指能够理解计算机系统的整体性、关联性、层次性、动态性和开放性,掌握计算机硬软件协同工作及相互作用机制,并综合运用多种知识与技术完成全系统开发的能力。可以说,系统能力培养将关乎我国整个自主可控信息产业的人才培养质量、自主创新能力、核心竞争力[4-5]。为此,计算机专业教指委启动了系统统能力培养专项[6],我校智能与计算学部于2016 年获批第二批系统能力培养示范校,启动对多门课程的综合改革,其目标是以现场可编程逻辑门阵列(FPGA)为实验平台载体,利用软硬件协同设计方法学,围绕面向MIPS32 指令集设计一台功能完备的计算机系统这一复杂工程问题,培养学生对系统的认知、设计、集成、开发和优化能力,实现对数字逻辑与数字系统、计算机组成与体系结构、操作系统等核心课程知识点的有效贯穿,使学生能够深入地理解计算机系统的运行机理,培养掌握自主可控技术信息产业创新型人才。

1 计算机类专业数字电路课程教学中的问题分析

在推进系统能力培养综合改革的过程中,发现数字逻辑与数字系统课程是从事处理器等高端芯片设计的重要基石。目前国内很多高校计算机类专业的数字电路类课程的实验主要采用①使用分立器件设计中小规模集成电路;②采用画原理图方式设计数字电路和系统,再通过仿真验证结果[7-8];③利用硬件描述语言(HDL)和电子设计自动化(EDA)工具设计电路,然后通过FPGA进行验证[9-11]这几种方式。但由于计算机专业的数字电路类课程在教学内容与电子信息类专业十分相近,缺乏面向本专业的优化设计,故这些方式均没有体现出系统能力培养所要求的整体性、关联性和层次性,无法对后续课程形成有力的知识和能力支撑,集中表现为以下一些问题:

(1)知识陈旧冗繁,与有序课程重叠或脱节。多数高校的数字电路类课程与现代超大规模集成电路设计的理念相距甚远,很多知识点过于陈旧冗繁,造成了该课程与后续课程的知识脱节,使学生在遇到处理器及片上系统(SoC)设计问题时,显得力不从心,现代数字系统设计流程和方法学的知识严重匮乏。

(2)实践教学多验证性实验,缺少综合性实验。实践教学多以验证性实验为主,造成学生缺少主动思考空间,使其体验和获得感不强,从而缺乏从事计算机系统设计的信心和决心。虽然采用HDL和EDA工具有助于开展高难度、高挑战性的综合性实验,但由于HDL门槛高,调试难度大,造成学生学习情况差异性大,老师难于评判等问题,也是制约综合性实验难以实施的原因。

(3)实验平台使用受限,实践教学质量难以保障。EDA工具是现代数字设计的基石,但需要学校投入大量资金购置设备;硬件实验调试难度大,需要学生花费大量时间,但实验室受管理制度制约,无法满足学生个性化学习需要,从而造成学生学习投入不足的问题。此外,综合性实验教学质量控制困难、协助学习成本高、教师难以掌握学生的学习进展,不利于持续改进。

2 计算机类专业数字电路课程改革思路

针对上述问题,课程组从计算机专业对于系统能力培养的实际需求出发,以单周期处理器设计为主线,重新梳理了数字逻辑与数字系统课程的核心知识和能力要求,包括:删除了CMOS 管、电平标准、数/模转换等过于底层知识点,而更加关注如何使用基本数字电路模块构建复杂数字系统;删除了布尔表达式化简、卡诺图、J-K触发器、T触发器等陈旧冗余知识点,而将重点放在基于HDL和EDA工具的现代数字电路设计方法和流程上;此外,课程还特别强调同步电路的时序分析,增加了处理器指令集和设计方法的讲解。进而,基于头歌(www.educoder.net)[12-13]和远程FPGA硬件云打造虚实结合实践教学平台,以32 位单周期MIPS 处理器设计这一复杂工程问题为终极任务,为学生提供一套以能力提升驱动知识获取的“点-线-面”三层递进式实践教学体系,实现对课程核心知识点的纵向衔接贯穿,使学生掌握现代数字电路和系统的设计方法、设计流程和验证手段。最终为后续课程完成流水线处理器设计、SoC系统集成、系统软件开发奠定坚实基础。

3 虚实结合的“点-线-面”三层递进式实践教学体系

“点-线-面”三层递进式实践教学体系面向课后练习、实验教学和综合实践3 个层次展开。其中课后练习依托头歌在线实践平台,实验教学和综合实践依托远程FPGA硬件云完成。

3.1 “点”实验

HDL是现代数字电路设计的基石,它并不是一门简单的编程语言,需要与电路结构紧密结合,这无疑增加了学习难度和复杂度,需要课后进行大量练习,才能很好掌握。但HDL 门槛高,调试难度大,教师评判困难,从而导致学生基础训练不足。为此,基于头歌平台设计了由一系列的知识点实验(简称点实验)构成在线实验,如图1 所示。整个“点”实验由两大部分,15个模块,共计46 个实验组成,用以对应课程中的核心知识点,实验规模小,难度较低,但均是基于HDL数字电路设计中的经典问题。

图1 基于头歌平台的点实验

头歌平台为多种编程语言提供了虚拟化实验教学环境,并提供了基于实验结果的自动评测功能,学生可自主完成实验,并进行自动评测和反复练习(见图2)。如图中左侧所示,每个实验均为学生提供了详细知识点讲解,学生按要求在右侧完成编程实验,并点击右下角评测按钮即可完成自动评测。这样,传统纸面作业被全部搬到线上,学生通过课后大量的自主练习掌握HDL的设计方法。此外,自动评测使老师能够走出编程类作业评判困难的窘境,将精力集中到分析头歌所提供的丰富学情数据之上(见图3),实时准确地掌握学生的学习情况,及时发现学生在实验过程中存在的问题,从而高效地进行教学反思和持续改进。

图2 “点实验”自动评测界面

图3 “点实验”学情数据统计界面

3.2 “线”实验

在“点”实验的基础之上,通过将若干知识点进行贯穿衔接,形成具有较高难度和挑战度的综合性设计实验,即知识线实验,简称“线”实验。“线”实验将基于EDA工具完成现代数字电路设计的完整流程,并在FPGA之上完成验证。在4 个“线”实验中,前两个针对组合逻辑设计,后两个针对时序逻辑设计。每个线实验都覆盖多个课程知识点,并为单周期MIPS 处理器设计提供支撑。

实验1多数表决器的设计与实现

(1)知识要求。①熟练使用HDL的行为建模方法对组合电路进行描述;②熟练使用HDL 的结构建模方法对组合电路进行描述。

(2)能力要求。①能够使用HDL对数字逻辑电路进行描述;②能够基于Vivado完成数字逻辑电路的设计;③能够基于Vivado 对数字电路进行仿真和验证。

(3)实验内容。采用行为建模设计两款74 系列芯片,分别是74LS138 和74LS139,然后,采用结构化建模方式对所设计的两款芯片进行集成,实现5 输入多数表决器功能。注意,虽然在课程讲授中删除了74芯片的内容,但在第1 个实验中直接给出74 芯片的描述,让学生采用HDL 完成建模和集成,其目的是使学生能够将高层次的HDL描述与底层电路相对应,做到“心中有电路”,而不是将HDL当成一门高级语言。

实验2算术逻辑单元(ALU)的设计与实现

(1)知识要求。①掌握全加器和行波进位加法器的结构;②掌握计算机内标准算术逻辑单元(ALU)的结构;③熟悉加减法运算溢出的判断方法。

(2)能力要求。熟练使用HDL 对ALU 进行建模,为单周期处理器中的运算部件设计奠定基础。

(3)实验内容。实现8 位算术逻辑运算单元,支持常见16 种算术逻辑运算,支持溢出、零、负数和进位/借位等状态信息位的判断。其中输入均为补码使用,只能使用一个加法器(不能使用减法器),加法器需要使用全加器通过结构化建模方式实现。

实验3分秒数字中的设计与实现

(1)知识要求。①掌握基于HDL的时序逻辑电路建模方法;②掌握利用计数器设计使能时钟,用于时钟分频;③掌握利用移位寄存器设计按键去抖和边沿检测;④掌握7 段数码管的动态显示。

(3)实验内容。实现分秒数字钟功能,支持复位、暂停、启动等功能。

实验4自动贩售机的设计与实现

(1)知识要求。①掌握有限状态机(FSM)的设计方法;②掌握通用异步收发(UART)传输协议和设计方法;③掌握存储器映射的寄存器的使用方法。

(2)能力要求。①能够熟练使用HDL进行三段式状态机的建模;②掌握通过接口寄存器控制外设的方法;③掌握块存储器(BRAM)IP核的使用方法。

(3)实验内容。实现自动贩售机的功能,采用块存储器存储货物信息,采用数码管显示已支付金额和找零金额,通过串口打印货物基本信息和库存量。

上述线实验均通过智能与计算学部搭建的虚实结合远程FPGA硬件云完成,如图4 所示。FPGA硬件云通过虚拟机和容器机制可以使多位同学分时共享一块真实的FPGA开发板,同时基于Web 提供大量虚拟外设,通过原理图方式完成验证平台的搭建,并将真实FPGA上的实验结果返回给设计者,使得学生获得真实的实验体验[14-15]。该FPGA 硬件云配备100 块Xilinx FPGA板卡,可并发支持400 名学生进行上述线实验,为学生提供全共享、全开放、不受时空限制的实验环境,满足学生个性化学习需求,同时降低了实验室的管理成本。

图4 虚实结合的远程FPGA硬件云

3.3 “面”实验

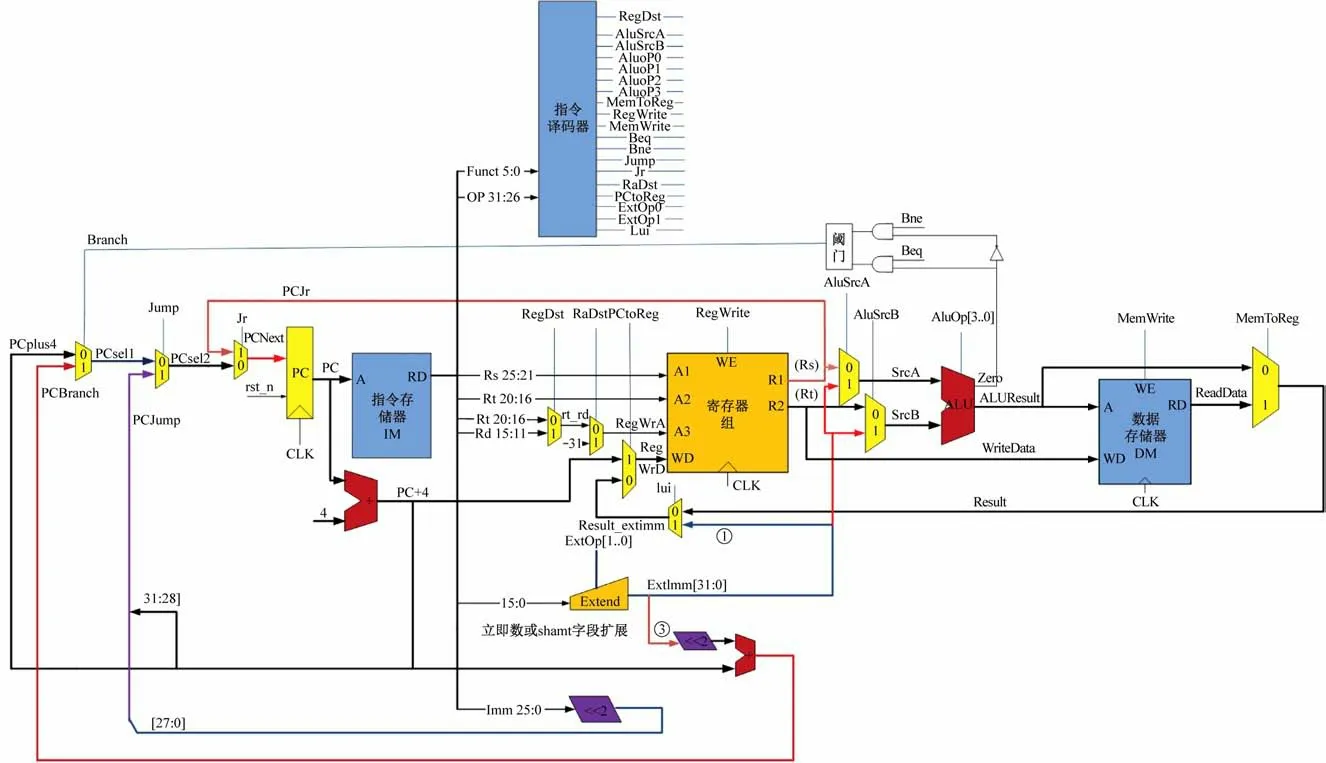

在“点”实验和“线”实验的基础之上,综合利用课程所学的识点,围绕32 位MIPS 指令集,以单周期处理器设计作为最后综合的“面”实验。“面”实验仍然在远程FPGA硬件云之上完成。所设计的处理器如图5 所示。

图5 单周期32位MIPS处理器原理图

处理器设计属于典型复杂工程问题,需要熟练掌握数字逻辑电路基本知识,并结合较强的数字电路设计能力才能完成,符合“两性一度”的金课标准。相比之前的“点”实验和“线”实验强调学生单兵作战能力,“面”实验需要分组完成,强调学生的团队协作能力。整个实验分为原理图设计、HDL 设计和测试验证3 个组。3 个组构成一个设计团队。原理图设计组采用数字电路仿真工具Logisim,通过画图方式完成处理器设计;HDL设计组基于HDL 和EDA 工具完成处理器设计;测试验证组提供测试用例。前两组进行交叉验证,均通过了所有测试用例,才可达到处理器设计要求。

此外,“面”实验对于学生采用分层评价,针对每组同学的能力设定不同的评价层次,力争使每组同学都能从实验中获得成就感和从事计算机系统设计的信心。“面”实验的评价分为3 个层次,如表1 所示。

表1 “面”实验分层评价标准

4 细粒度实践教学指令监控和分层评价机制

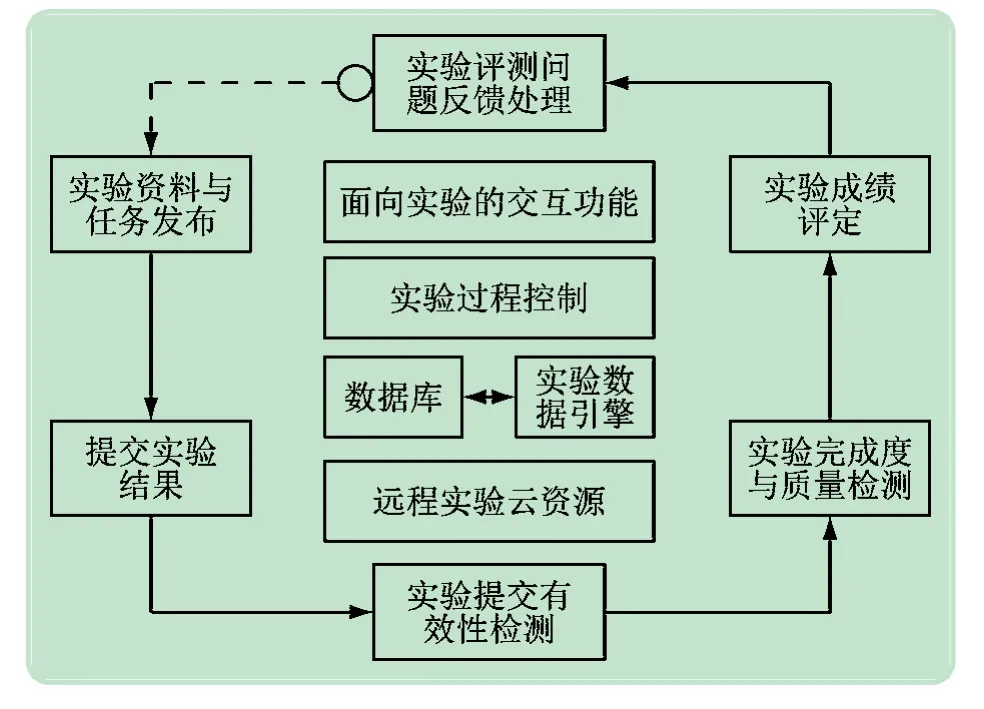

由于硬件实验本身难度高,挑战性大,调试成本高,致使实验过程控制粒度过大,教师往往只能在宏观层面管理实验活动,难以全面掌握每个学生的学习进度,“抱大腿”现象广泛存在,最终致使教学目标达成度的有效性难以保障。为此,制定了一整套细粒度的在线实验全程监控机制,实现对学生实验全过程的留痕。拟将实验过程细化为实验任务发布、提交实验结果、有效性检测、完成度和质量检查、成绩评定和问题反馈处理6 个阶段。借助虚实结合实践环境提供的数据留痕功能,按该6 个阶段监控学生的实验全过程,每轮实验均对学生实验完成情况进行分析,为下轮次实验提供指导和反馈,形成闭环,如图6 所示。

图6 基于虚实结合实验环境的细粒度全程监控机制

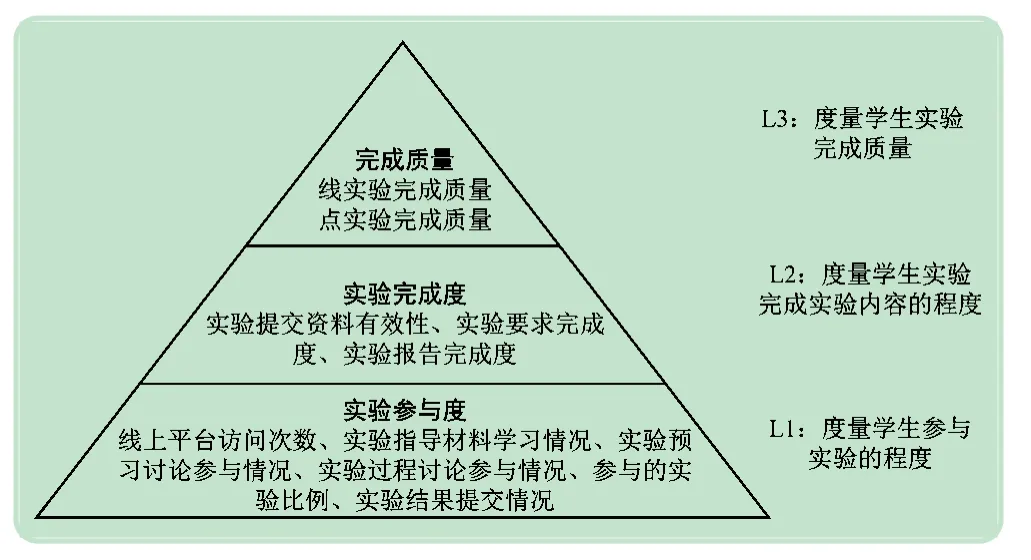

此外,在传统数字逻辑与数字系统课程的实践教学过程中,实验成效评价较为粗糙,教学设计改进欠缺科学依据。其原因是缺乏细粒度的过程性数据,通常只能依赖单一的成绩指标,难以精确定位学生在实验过程中遭遇的学习难点,难以精确量化学习效果,难以及时反馈给教学设计。为此,基于虚实结合实践环境提供的丰富学情数据,建立一套金字塔结构的3 层在线实验评价指标体系,用于对学生的实验作业进行多角度评价。如图7 所示,分为实验参与度、实验完成度和实验完成质量3 个层次。每个层面均由在线平台提供的大数据进行支撑,覆盖了实验各个阶段活动。对于学生,为学习和提升明确了能力层级。对于教师,可多层次分析学生能力分布情况,以改进教学设计。

图7 基于金字塔结构的3层在线实验评价指标体系

5 改革成效

实践教学改革自2018 年已推行4 年,学生的计算机系统能力得到提升,为后续计算机系统类课程奠定了坚实的知识和能力基础,在一定程度上扭转了计算机专业学生普遍存在的“欺软怕硬”现象。数字逻辑与数字系统课程的学生评教成绩从2019 年前的91 分提升到97 分以上,学生普遍反映实验虽然挑战性高,但内容和资源丰富,知识点之间逻辑关系清晰,任务设置合理。学生还反映本课程有利于能力提升,使系统思维得到了充分训练,同时激发了学习积极性。此外,后续课程的授课教师反映,“点-线-面”3 层递进式实践教学体系为学生后续课程打下坚实基础,学生可以相对轻松地过渡到更高阶的计算机系统类实验。以该实践教学体系为依托,学部已有多支队伍参加“全国大学生系统能力培养大赛——CPU 设计赛道”的比赛,并获得1 次二等奖,2 次三等奖的好成绩。多位毕业生进入海思、龙芯、飞腾、中科院计算所、清华、北大等企业、高校从事计算机基础软硬件的研发和科研工作。整个教学团队共撰写相关教材2 本,其中《计算机系统设计》获首届天津大学优秀教材建设二等奖,已被30 余所高校选定为相关课程的指定教材或参考教材。基于智慧树平台建设了MOOC课程,已为10所高校,4 000 余名学生提供服务。此外,教学团队已与2 家企业签署了4 项教育部产学合作协同育人项目,承担了3 项校教改项目。课程组教师多次受邀参加各类教学研讨会,并报告分享课程建设经验。

6 结语

一直以来,计算机专业的数字电路类课程的教学内容与现代超大规模集成电路设计理念严重脱节,无法形成对后续计算机组成与体系结构等课程的有力支撑,学生学习兴趣低、积极性差,使得系统能力培养不到位,制约了对我国自主可控信息类人才的培养水准。通过重新梳理该课程的知识点,设计了适应系统能力培养需求的“点-线-面”三层递进式实践教学体系,经过多年实践,取得了良好的教学效果。该实践教学体系的创新点表现在:①以“单周期处理器设计”这一复杂工程问题为主线,针对课后练习、实验教学和综合实践3 个层次,设计一系列纵向贯通、环环相扣、逐步推进的实验任务,形成对后续课程的有力支撑;②“虚-实结合”的实践平台为学生提供开放、共享、无时间/地域限制的全天候实验环境,提高了实验教学的效率和效果,同时,也将教师从繁重的实验作业批改中解放出来,使其将更多的精力放在对学情的分析和持续改进工作中;③细粒度实践教学质量监控和分层评价机制使得学生能够从高挑战度的实践中获得认同感,激发其未来从事计算机系统研究和开发工作的兴趣,增强其信心和决心。

下一步,拟从以下三方面入手继续完善相关工作:①充实“点实验”和“线实验”,形成实践教学案例库,通过头歌、智慧树平台进行共享;②将所设计的单周期处理器从MIPS指令集转换为当前主流的开源指令集RISC-V,从而与国家自主可控信息产业发展战略更契合;③将目前在业界迅速发展的集成电路敏捷开发方法引入到实践教学中,紧跟产业发展步伐,使学生掌握最前沿的数字系统设计流程和方法。