基于FPGA的宽带线性调频信号产生技术

郭露 骆守峰

(中国电子科技集团公司第十四研究所 江苏省南京市 210039)

1 引言

在传统雷达系统中,受限于微波器件的性能和数字处理芯片的处理能力,一般使用窄带线性调频信号作为雷达信号。为了适应电磁环境日益复杂的现代战场,雷达距离分辨力和抗干扰能力的要求不断提高,宽带雷达的研制也随之迅猛发展。宽带线性调频信号产生作为宽带雷达的一项关键技术,受到了广泛地研究[1]。

使用数字方法产生窄带线性调频信号,再通过模拟倍频的方式可以产生宽带线性调频信号[2],但是这种方式对线性调频信号的频率和带宽限制很多,并且实现过程需要很多模拟器件进行配合,导致所产生的信号幅相特性较差,为了满足雷达的性能需求,还需要使用额外的资源对信号幅相特性进行补偿[3]。另一种产生方法是结合可编程逻辑器件(FPGA)和高速数模(D/A)转换器,传统方式是使用非易失性存储器对波形数据进行存储,然后FPGA在接收指令后通过访问存储器的对应地址来加载波形,这种方法的缺点是宽带线性调频信号的数据量较大,使用存储器存储波形的能力有限,在实际应用中灵活性很差。目前发展的另一种方法是利用FPGA完成DDS(直接数字合成)的功能,在指令的控制下实时计算线性调频信号对应的幅度数据,再将数据送往D/A转换器产生模拟信号。根据奈奎斯特定律,FPGA所产生的数据率应大于信号带宽的2倍,然而,受限于FPGA较低的工作频率,可以采用多相DDS结构来产生线性调频数字信号[4]。

多相DDS结构的示意图如图1所示,不同相路由各自的频率字和相位字控制,在相同系统时钟的作用下,输出对应相路的线性调频数字信号,最后经并串转换器输出合成后的线性调频数字信号。在多相DDS结构中,研究的关键在于不同相路频率字和相位字的构建方法。文献[5][6]报道了多种频率字和相位字构建方法,然而这些方法较为复杂,同时也没有对该方法的脉冲宽度、带宽、起始频率和调频斜率等信号关键指标的精度进行分析。

图1:多相DDS结构示意图

本文提出了一种基于FPGA的宽带线性调频信号产生技术,对该技术产生的线性调频信号的基本原理进行了理论推导,并对线性调频信号脉冲宽度、带宽、起始频率和调频斜率的精度进行了分析,最后通过仿真计算和实验对该技术进行了验证。

2 宽带线性调频信号产生原理

2.1 宽带线性调频信号产生技术基本理论

连续的线性调频信号可表示为:

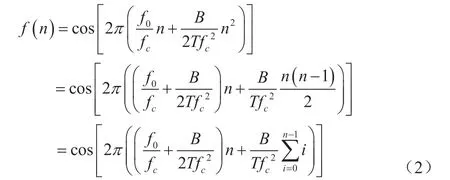

其中f0为起始频率,B为带宽,T为脉冲宽度。将连续信号转换到数字域,用nTc代替t,离散的线性调频信号可表示为:

定义:

式中,L为DDS结构中相位累加器的位数。从式(3)中可以看出,S的物理含义是数字域的起始频率,R的物理含义是数字域的调频斜率。将式(3)代入式(2)中,可以得到:

对于多相结构DDS生成线性调频信号,式(4)可转换为:

式中,M为多相结构的总相数,m为不同的相路(m= 1,2,3,...,M)。

对于单个DDS结构而言,输入端包含频率字和相位字,输出端包含瞬时相位和相位对应的幅度值,输出端的瞬时相位等于频率字的累加和再与实时相位字相加[7]。为了得到多相结构的线性调频数字信号,根据式(5),我们需要构建频率字Fm(n)和相位字Pm(n),使其满足瞬时相位:

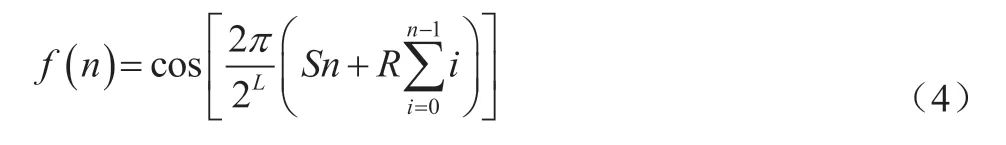

根据瞬时相位的规律,我们可以得到,当频率字和相位字满足式(7)时,式(6)成立。

利用式(7)可以得到,频率字的步进满足:

当总相数M=2k时,只需要简单的加法器配合移位操作即可完成频率字的计算。

从式(7)中可以看出,相位字不随时间变化,因此只需要计算初始相位字即可。从以上分析可以看出,当初始频率字和初始相位字确定,且总相数M=2k时,只需要M个简单的加法器即可计算出所有的频率字和相位字。

2.2 宽带线性调频信号产生技术精度分析

对于线性调频信号而言,关键参数包含4个,分别为脉冲宽度、带宽、起始频率和调频斜率,接下来对这4个参数的精度进行分析。

信号脉冲宽度与FPGA工作频率、总相数和时钟周期数有关,在线性调频数字信号产生方法中,相数和时钟周期数为整数值可控,当脉冲宽度为FPGA工作时钟周期整数倍时,相数和时钟周期数引入的误差为0。FPGA工作频率来源于晶振的振荡频率,晶振的频率偏差会导致信号的绝对脉冲宽度出现偏差,但是由于信号产生模块和接收采样模块使用的时钟为同源时钟,在数据处理过程中工作频率引入的频率误差可以完全抵消。因此利用本文提出的方案产生线性调频信号,受限于晶振的振荡频率误差,存在绝对脉冲宽度误差,但是由于整个射频链路使用同一晶振作为参考源,所以该绝对脉冲宽度误差不会导致雷达性能恶化。

根据式(3)可以计算带宽的精度。由于R必须为整数,所以R的最大误差为0.5。将R的最大误差值代入式(3),可以得到带宽的最大误差值为:

根据式(3)计算起始频率的精度,起始频率的最大误差值为:

线性调频信号调频斜率的最大误差值为:

从式(9)-式(11)可以看出,带宽、起始频率和调频斜率的最大误差值取决于信号脉冲宽度、D/A工作频率和相位累加器位数,与信号带宽无关。D/A工作频率越高,带宽、起始频率和调频斜率的误差越大。信号脉冲宽度越大,带宽的误差越大。当雷达系统架构和雷达波形确定后,信号脉冲宽度和D/A工作频率也随之确定,此时只能通过调整相位累加器的位数来改变信号精度。相位累加器的位数每增加1bit,带宽、起始频率和调频斜率的误差减少50%。由于相位累加器的位数增加会导致FPGA的资源利用量增加,在实际雷达信号产生模块设计中,需要根据总体提供的指标来计算所需要的相位累加器位数,在资源和性能两方面进行折中考虑。

典型地,设脉冲宽度为100μs,D/A的工作频率为1600MHz,当相位累加器的位数为32bit时,带宽、起始频率和调频斜率的最大误差值分别为29.8kHz、0.19Hz、298 Hz/μs。当相位累加器的位数为40bit时,带宽、起始频率和调频斜率的最大误差值分别为0.12kHz、0.74mHz、1.2 Hz/

μs。

从上述典型值可以看出,起始频率的误差一般远小于带宽的误差,这是因为线性调频信号的时间带宽积一般很大。此外,由于带宽的误差值为绝对误差,因此带宽的误差对宽带线性调频信号的影响会远小于窄带线性调频信号,在采用该技术同时产生宽带和窄带线性调频信号时,需要对窄带线性调频信号的性能指标进行重点关注。

3 仿真计算

假设所需要产生的信号中心频率为200MHz,带宽为200MHz,脉冲宽度为100μs,D/A的工作频率为1600MHz,相位累加器的位数设置为32bit。根据FPGA一般的工作速率,选择总相数为8相,此时FPGA的工作速率为200MHz。根据式(7),8相DDS的频率字和相位字如表1所示。

表1:不同相路的频率字与相位字(8相结构)

根据式(3)计算,得到R=3355,S=268437134。将其代入表1,可以计算8相DDS对应的实际频率字和相位字。在软件中搭建图1所示的多相DDS结构,并代入计算好的频率字和相位字,最后提取输出信号的幅度信息。所得到的线性调频信号的时域波形如图2 (a)所示,从图中可以看出信号的脉冲宽度为100μs,脉冲前沿为低频信号,脉冲后沿为高频信号。对该信号进行傅里叶变换,得到信号的频谱,如图2 (b)所示,从图中可以看出输出信号的频率范围约为100-300MHz,与仿真设置值一致。

图2:线性调频信号仿真结果图

4 实验验证

我们在硬件上使用FPGA和D/A转换器实现了线性调频信号的产生,FPGA使用Xilinx公司的XC4VSX55-10FF1148I,D/A转换器选择ADI公司的位宽为14bit的AD9739,系统架构如图3所示。

图3:基于FPGA+D/A的线性调频产生方案系统架构图

AD9739的工作时钟设置为1.6GHz,AD9739内部进行4分频,返回FPGA的时钟频率为400MHz。在FPGA内部,400MHz输入时钟进入数字时钟管理(DCM)模块进行分频,得到200MHz时钟作为FPGA的工作时钟。该工作时钟驱动8路DDS模块,每路DDS模块产生对应相路的14bit线性调频数字信号,其中第一、三、五、七路数据通过OSERDES合成后送往D/A转换器的数据总线0(DB0)接口,第二、四、六、八路数据通过OSERDES合成后送往D/A转换器的数据总线1(DB1)接口,DB0接口和DB1接口的数据率均为11.2Gbps。AD9739在接收到线性调频数字信号后,经过内部数模转换处理,输出线性调频模拟信号。

使用示波器和频谱仪对接收到的线性调频信号进行采集,所产生的正调频斜率线性调频脉冲信号如图4(a)所示,脉冲宽度为100μs,脉冲前沿为低频信号,脉冲后沿为高频信号。信号频谱如图4(b)所示,信号频率范围为100-300MHz,带内平坦度优于1dB,其中高频段的峰为该信号在第二奈奎斯特域的镜像信号。所得到的时域信号和频域信号与仿真结果基本一致,证明了该线性调频信号产生技术的有效性。

图4:实验产生的线性调频信号

5 结论

本文提出了一种基于FPGA的宽带线性调频信号产生技术,该技术使用FPGA和高速数模转换器,并利用多相直接数字合成方法产生宽带线性调频信号。本文首先推导了该技术的基本理论,并分析了脉冲宽度、带宽、起始频率和线性调频信号调频斜率精度,提出了提高线性调频信号精度的方法。最后通过仿真分析和实验分别产生了100μs脉冲宽度、200MHz带宽的线性调频信号,验证了该技术的可行性和有效性。该技术具有通用和简单的特点,可以应用在更大带宽的雷达系统中。