AIS 与ASM 多信道实时接收解调系统

黄金磊,王建新,杨树树

(1.南京理工大学电子工程与光电技术学院,江苏南京 210094;2.南京电子设备研究所,江苏南京 210007)

2013 年,ITU-R 和IALA 共同提出了甚高频数据交换系统(VHF Data Exchange System,VDES)[1]。VDES在保留AIS 系统原有功能的基础上,引入了特殊应用报文(Application Specific Messages,ASM)和宽带甚高频数据交换(VHF Data Exchange,VDE)[2]。

为了实现对AIS 和ASM 业务的实时接收处理[3],该文设计了一种AIS 与ASM 接收机,采用8 核处理,可同时接收六个信道的信号并实时解调;采用SRIO接口实现数据传输,保证了FPGA 端和DSP 端数据传输的效率;对内存进行了规划重分配,降低了硬件资源的开销;使用了恒虚警检测算法[4],保证了噪声环境下虚警概率保持不变。

1 AIS与ASM信号概述

1.1 信道划分

国际电信联盟将海上VHF频段分配给AIS四个信道,分别是AIS1(161.975 MHz)、AIS2(162.025 MHz)、AIS3(156.775 MHz)、AIS4(156.825 MHz),信道带宽为25 kHz,比特速率为9 600 bit/s。分配给ASM 两个信道,分别是ASM1(161.950 MHz)、ASM2(162.000 MHz),信道带宽为25 kHz,符号速率为9 600 symbol/s。

1.2 信号帧格式

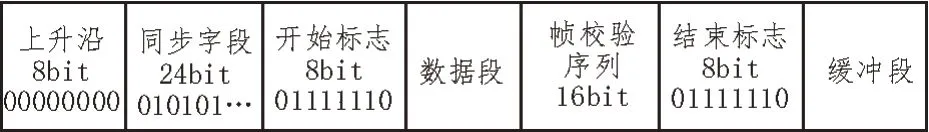

AIS 和ASM 将一分钟分成2 250 个时隙,其中每个时隙占用的时间为26.67 ms。AIS 信号分为单时隙信号和双时隙信号,其中仅有消息ID 为5 的AIS信号是双时隙信号,单时隙信号总长为256 bit,双时隙信号总长为512 bit,AIS3 和AIS4 信道是远距离AIS 信道,仅传输单时隙信号[5]。AIS 信号帧格式如图1 所示。

图1 AIS信号帧格式

上升沿的长度为8 bit(00000000);同步字段长24 bit,由交替的0 和1 组成;开始标志和结束标志的长度为8 bit(01111110);帧校验序列为16 bit,用于验证接收到的AIS 消息是否正确;AIS1 和AIS2 信道的单时隙信号数据段长度为168 bit,双时隙信号数据段长度为424 bit,其余部分两者相同,缓冲段24 bit;AIS3 和AIS4 信道的信号数据段长度为96 bit,其他部分与AIS1 和AIS2 信道的单时隙信号相同,最后由缓冲段补足256 bit。数据段中存储了消息ID、用户ID 和其他轮船相关状态信息。

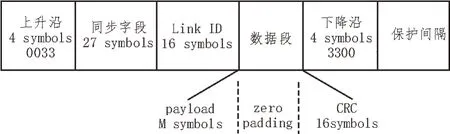

ASM 信号的帧格式与AIS 信号类似,根据Link ID 的不同会影响数据段的长度,以及是否需要Turbo编码,其通用帧格式如图2 所示。

图2 AIS信号帧格式

由图2 可得,ASM 信号由上升沿、同步字段、Link ID、数据段、下降沿和保护间隔组成,其中数据段由数据、补零以及CRC 校验码组成。Link ID 的不同会影响数据段和保护间隔的长度。

1.3 编码方式和调制方式

AIS 信号的编码方式为NRZI 编码,在NRZI 编码之前,为了防止数据段和帧校验段出现01111110 的码型,导致信号的结束标志定位出错,AIS 消息的数据段和帧校验段遵循比特填充原则:如果在待发射信号中检测到五个连续的1,则在这五个连续的1 后插入一个0,在解调时相应地也要经过去零处理。

AIS 信号采用高斯最小频移键控(Gaussian Minimum Shift Keying,GMSK)。GMSK 的调制过程就是信号在编码后先通过一个高斯低通滤波器,使得调制信号的相位连续且波形平滑,再进行最小频移键控调制。

ASM 信号的调制过程是首先对Link ID 采用一阶Reed-Muller 编码并加扰,再根据Link ID 确定是否需要对数据段进行Turbo 编码,接着对数据段进行加扰,然后对整段信号做π/4 QPSK 调制,最后对ASM 信号进行整数倍内插,再通过成形滤波器,提高数据速率[6-7]。

2 解调预处理

2.1 数字下变频及抽取滤波实现

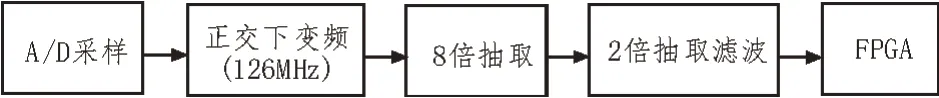

该文采用的A/D 转换器是AD9684,以采样频率fs=288 MHz 对经过前端滤波放大后的射频信号进行带通直接采样,采样后的信号先在A/D 中经过预处理,再发送到FPGA 进行后续处理[8]。A/D 预处理流程框图如图3 所示。

图3 A/D预处理流程框图

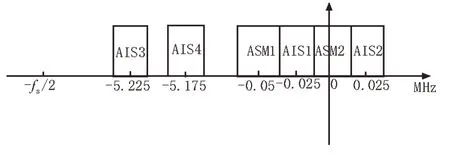

AD9684 内部直接数字频率合成器的频率控制字字长为12 位,126 MHz 本振频率对应的频率控制字取值为1 792,因此没有本振频率误差产生,得到的下变频结果更加精准。滤波抽取部分使用A/D 中自带的半带滤波器实现,16 倍的抽取用四个半带滤波器级联得到,前三级半带滤波器只对信号进行8 倍抽取而不滤波,最后一级半带滤波器进行2 倍抽取并滤波。在A/D 预处理之后,fs=288 MHz/16=18 MHz,此时信号频谱图如图4 所示。

图4 基带信号频谱图

由图4可知,在经过A/D采样、A/D预下变频及滤波抽取后,AIS的四个信道分别被搬移到了-0.025 MHz、0.025 MHz、-5.225 MHz和-5.175 MHz,ASM 的两个信道分别被搬移到了-0.05 MHz 和零频,信号速率为18 MHz,在FPGA 中对信号再分别经过正交下变频与滤波抽取即可分离得到六个信道的复基带信号。

解调系统要求送至DSP 解调的信号的数据速率为8 倍的符号速率,即76.8 kHz,因此FPGA 中的抽取倍数应为D=18 MHz/76.8 kHz=234.375,由于小数倍抽取在FPGA 实现过于复杂,这里取抽取倍数D=234,以234 倍抽取后,数据速率变为18 MHz/234=76.923 kHz。抽取可以采用级联的方式,由于D=234=39×6,所以可以第一级用CIC 滤波器实现抽取因子D1=39 的滤波抽取,第二级用FIR 滤波器实现抽取因子D2=6 倍的滤波抽取[9]。

分离出六个信道的信号以后,对六个信道的信号做帧头检测,AIS 信号和ASM 信号都有固定的同步字段,可以通过同步字段的特点来实现帧头检测。

2.2 数据接口

在信号通过帧头检测后,需要将FPGA 中的复基带信号传输到DSP 中进行后续解调,该文选择SRIO 接口实现FPGA 与DSP 之间的数据传输[10]。该文采取以下传输方案:当AIS1 和AIS2 信道检测到信号后,向DSP 传输2×2 048=4 096 个数据点;当AIS3和AIS4 信道检测到信号后,向DSP 传输2 048 个数据点;当ASM1 和ASM2 信道检测到信号后,向DSP传输3×2 048=6 144 个数据点。这样就可以保证该帧信号的信息不会有丢失。

3 多信道信号解调与DSP实现

由于解调系统的实时性要求能同时解调六个信道的信号,因此该文选择用TMS320C6678 作为DSP平台实现后续的解调工作。TMS320C6678 有八个核心子系统,每个子系统有1.0 GHz 或1.25 GHz 的c66x定/浮点CPU 核。该文使用核0 完成一系列初始化工作与算法自检,核1 至核4 分别完成一个AIS 信道的信号解调,核5 与核6 完成两个信道的ASM 信号解调,核7 完成网口信息传输,每隔1 s 将解调的信息打包发送至上位机,秒脉冲由FPGA 通过EMIF 接口发送到DSP[11]。

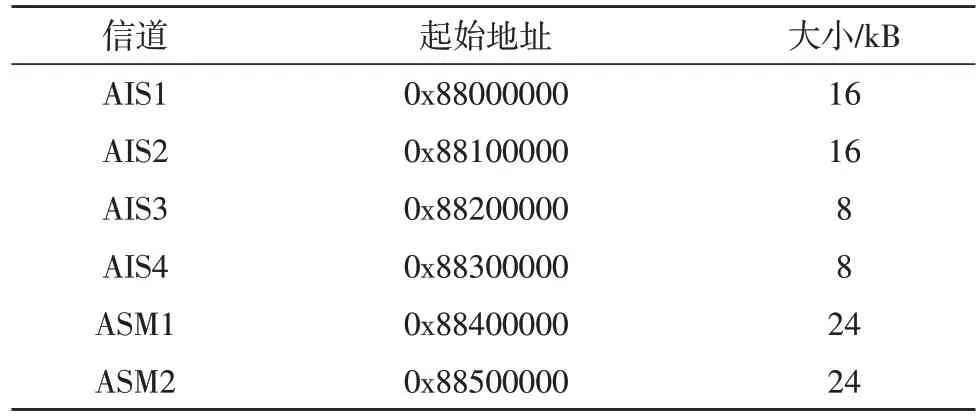

由于DDR3 的存储空间大,且六个核都可以对其进行存取操作,因此该文的设计是通过SRIO 将数据送至DDR3 存储区。出于算法实时性的考虑,FPGA和DSP之间并不采用握手,DSP在DDR3存储区开辟了六块存储空间,FPGA 将六个信道的数据分别送至该存储区的指定地址,DSP 端不断轮询该地址的值,当检测到对应地址收到数据时,DSP 的核1至核6 分别将对应存储区的数据取出处理。DSP 开辟的六个存储区的地址如表1 所示。

表1 SRIO传送数据的储存地址

下面以AIS1 和AIS2 信道的双时隙信号为例说明DSP 中AIS 信号的完整解调流程。由前文可知,当AIS1 和AIS2 信道检测到信号时,FPGA 传送4 096个数据点,但是实际上AIS 信号仅在ID=5 时是双时隙信号,大多数时候接收到的AIS 信号都是单时隙信号。因此该文的解调方案是先把所有信号当成是单时隙信号,对前2 048 个数据点进行解调,如果CRC 校验失败则去判断消息ID,当检测到消息ID 为5 时,判断为双时隙信号,先保存前面解调的结果,再取后2 048 个数据点进行解调,最后将两次解调结果拼在一起再进行CRC 校验,通过,则输出信息,不通过,则丢弃这帧信号。此处可以利用内存管理技术,在保存好第一次解调出来的256 个采样点后,前面解调过程产生的中间变量都可以被覆盖,这就能节约一半的内存空间。

DSP 中AIS 信号的解调流程如图5 所示。

图5 DSP中AIS信号的解调流程

ASM 的解调流程与AIS 类似,只不过ASM 信号是先利用同步字段估计出一个大频偏,去除这个大频偏之后就进行定时同步,降低数据速率,之后再通过M&M 算法得到残余小频偏,然后再进行相偏估计。

两者的解调流程都是分段解调,先解调一个时隙长度的数据也就是256 个符号,然后再根据解调结果中的ID 相应地进行后续时隙内容的解调。

3.1 频偏算法

常用的频偏估计方法有差分相关法、最大似然估计法、锁相环和二阶矩估计法等。差分相关法在频偏较大时,频偏估计误差很大,只能作为一种初步的频偏估计,不能达到精确估计的要求。最大似然估计法的估计误差取决于搜索步长,步长越小,估计误差越小,但耗费的时间也越多。传统的锁相环在频偏较大时的捕获时间很长,不符合解调系统实时处理的要求。综合测频精度、计算复杂度以及GMSK信号自身特征等因素,该文采用二阶循环累积量法来估计AIS 信号的频偏。

ASM 信号通过M&M[12]算法来完成数据辅助的频偏估计,接着先经过匹配滤波和定时同步去除时延并降低数据速率,然后再通过M&M算法对256个符号进行非数据辅助频偏估计来获得更加精确的结果。

3.2 定时同步算法

GMSK 是MSK 信号的特殊形式,因此,MSK 信号的符号定时同步方法也适用于GMSK 信号。该文AIS的定时同步算法采用LM定时法[13],ASM 的定时算法采用Q&M 算法[14]。

通过定时算法计算出来的时延代表信号的第一个采样点与最佳采样点距离的估计值,这个估计值一般不是整数,如果需要提高精度,可采用插值的方法获得最佳采样点的值。该文将此估计值四舍五入取整后的值作为第一个采样点与最佳采样点的距离。

同时,从前文可知,由于小数倍抽取难以实现,因此实际采样周期与理论采样周期有微小的误差,作用到单个符号上时,时间非常短,误差可以忽略,但是在一段连续时间的积累之后,误差也会慢慢累积,而上述方法估计出的时延只是参与估计符号的平均时延,并不是每个符号的实际时延,如果参与估计的符号个数过多,会导致时延估计量与实际时延相差过大。因此该文将进行符号定时的数据进行了划分,分小段进行时延估计,每段用64 个符号做一次时延估计。在进行定时同步前,需要先经过匹配滤波器提高信号的信噪比,从而提升解调性能。

3.3 相偏估计算法

在去除频偏与定时之后,ASM 信号比AIS 信号多了一个相偏估计的过程,与ASM 信号的频偏估计类似,相偏估计也是通过两步估计以得到更加精确的处理结果。首先通过同步字段作为已知信息进行基于数据辅助的相偏估计,去除掉这个大相偏之后,与定时同步的做法类似,将信号分段,每段用64 个符号通过V_V 算法进行非数据辅助相偏估计[14-15]。

3.4 解调算法

AIS的解调算法有2bit差分解调、6bit差分解调、Viterbi算法等。2 bit差分解调实现简单且受载频相位偏差的影响较小,然而当AIS 信号存在同频干扰时,2 bit 差分解调的性能就会大大降低;6 bit 差分解调算法能获得比2 bit 差分解调更好的结果,而且在时间和资源的消耗上不会有太多的增加,但是只有在较高的信噪比下才能得到正确的结果[16];Viterbi算法解调结果精确,但是耗时较长,且需要在白噪声情况下才能得到较好的解调结果,因此在进行Viterbi 解调前还需要将数据通过一个白化滤波器。

以AIS 双时隙信号为例,为了兼顾解调的速度和精度,该文的处理过程是在定时同步后先进行6 bit差分解调,解调结果无法通过CRC 校验则再对其进行Viterbi 解调,如果仍然无法通过CRC 校验则判断信号的ID,如果判断是双时隙信号,则对后2 048 个数据点做上述一系列的处理。

ASM 信号在去除频偏相偏后先对Link ID 做Reed-Muller 码的译码,得到Link ID 后就可以知道这帧信号的各种信息参数,包括调制方式、是否经过Turbo 编码、数据段长度等,接着针对得到的Link ID对数据段进行解调,最后进行CRC 校验。

4 接收机性能测试

在实现上述设计方案后,对接收机进行性能测试。在耗时方面,以AIS 单时隙信号为例,解调部分消耗总时间最长为8.9 ms,且在信噪比较高不需要经过Viterbi 译码时整个过程仅需不到3.7 ms;以ASM单时隙信号为例,解调部分各流程消耗总时间最长为10.32 ms,若该单时隙信号为非Turbo 编码的Link ID 为1 的ASM 信号,则仅需消耗6.52 ms;由此可见消耗的时间都远小于单时隙信号占用的时间26.67 ms,由此证明该文的设计方案能够满足解调系统的实时性要求。

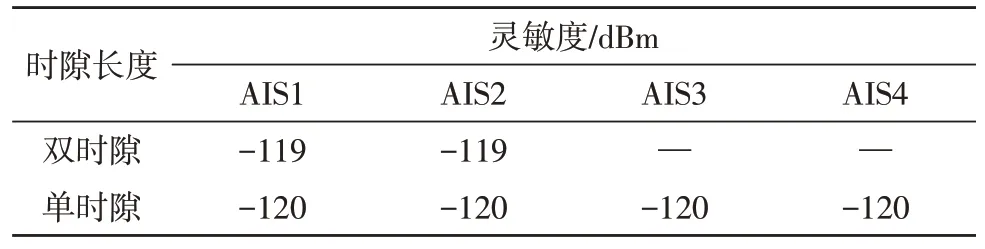

接着用信号源模拟发送报文信息,考虑到信道最拥挤的情况,AIS 的四个信道同时接连不断地收到AIS 信号,ASM 的两个信道也接连不断地收到ASM信号[17-18]。以解调正确率90%为界,得到接收机对AIS 信号的灵敏度测试结果,如表2 所示。

表2 接收机对AIS信号的灵敏度

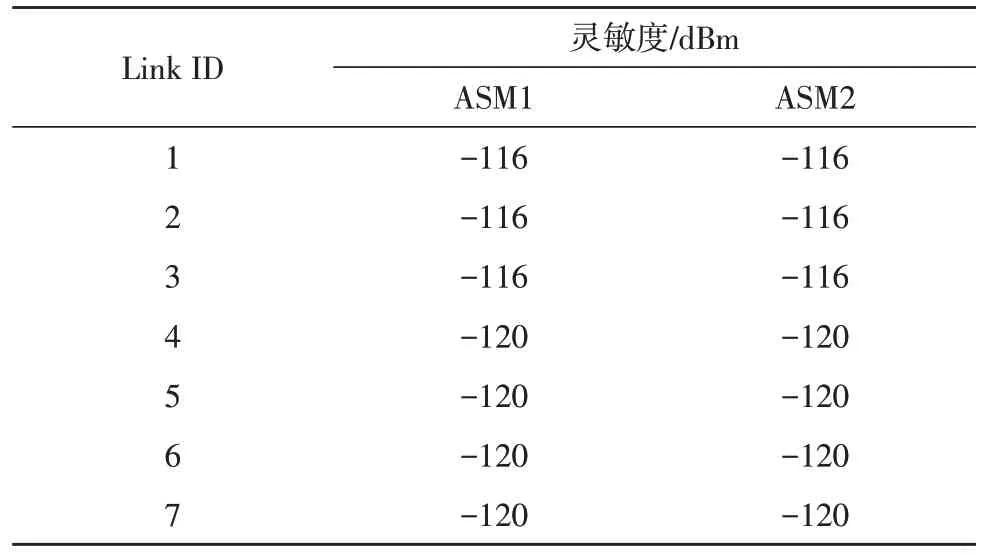

同理,以解调正确率90%为界,得到接收机对ASM 信号的灵敏度测试结果,如表3 所示。

表3 接收机对ASM信号的灵敏度

从表3 可以发现,接收机对ASM 信号的灵敏度因为Link ID 的不同而有较大区别,

这是因为Link ID 为4、5、6、7 的ASM 信号是经过Turbo 编码的,信号可靠性提高了,因此灵敏度也有了一定提升。

5 结论

该文提出了一种AIS 与ASM 多信道接收机,对接收机的设计、硬件平台、解调算法做了详细阐述,最终对工程实现产品进行了性能测试,测试结果表明,该文设计的多信道接收机可以实时处理解调四个AIS 信道和两个ASM 信道的信号,甚至能在一个时隙的时间内完成对多时隙信号的处理,并且具有较高的灵敏度,AIS 在输入信号幅度为-119 dBm 的情况下能达到90%的解调率,ASM 在输入信号幅度为-116 dBm 的情况下能达到90%的解调率,具有实际应用价值。