高速PCB信号完整性分析与设计的实验项目开发

杨 柳, 潘英茂, 马学条

(杭州电子科技大学国家级电工电子实验教学示范中心,杭州 310018)

0 引 言

高速信号[1]是频率超过100 MHz,或上升沿少于1 ns的信号。当前,印制电路板(Printed Circuit Board,PCB)信号传输速率已进入高速阶段,电路工作频率达到几百兆赫兹甚至更高。随着频率上升,信号经过互连线会显现出传输线效应,影响信号质量,破坏信号波形[2],使接收到的信号失真。

信号完整性广义上指在高速电子产品中由互连线引起的所有问题。国内外研究者对信号完整性问题进行了诸多探索。文献[3]中给出了高速数模混合PCB的设计方法和流程;文献[4]中综合了电源与信号完整性分析,讨论和仿真同步开关噪声;文献[5-10]中对高速差分传输线仿真模型建立、参数设计、信号完整性分析及应用等方面进行了研究;文献[11-12]中对高速PCB中差分过孔进行仿真分析,并做了优化;文献[13-14]中对高速互连部分的信号完整性进行了分析;文献[15]中利用Cadence软件绘制高速数据传输系统原理图及PCB图,仿真解决串扰、反射、电源完整性等问题;文献[16]中从理论及计算角度给出了信号反射现象形成的原因;文献[17]中提出新的高速信号传输线结构即电容分段传输线路;文献[18]中提出了基于ANSYS软件和IBIS 5.0模型的第4代双倍速率同步动态随机存储器(Double-Data-Rate Fourth Generation Synchronous Dynamic Random Access Memory,DDR4 SDRAM)信号完整性仿真方法。

上述研究显示,高速PCB设计中的信号完整性问题已得到广泛关注,信号传输的完整与否直接影响电子产品的性能。为使学生实验技能达到课程要求,同时提高综合设计能力,更好地适应技术发展与社会需求,开发了高速PCB信号完整性分析与设计实验项目。该项目是在传统PCB设计方法的基础上,结合信号完整性理论,建立模型运用SIwave、Design和HFSS工具进行仿真,总结出新型PCB设计方法,完成电子产品的设计、开发,实现缩短电子产品研发周期,优化产品性能,降低成本等目的。

1 信号完整性问题

1.1 信号完整性问题产生的原因

信号完整性问题产生的原因主要归结为:

(1)工作频率提高导致信号上升时间变短;

(2)不断降低的工作电压导致噪声容限变小;

(3)密度越来越大的PCB布局,使寄生效应增强,串扰加大;

(4)信号源噪声带来的信号高低电平阈值范围缩小,导致逻辑电平的传输错误。

解决信号完整性问题就是要保证信号传输波形和信号时序的完整。在PCB设计的过程中,把器件之间互连线的设计和阻抗联系起来,从根本上对信号完整性问题进行量化分析,可以消除许多潜在的信号完整性问题。

1.2 传输线建模

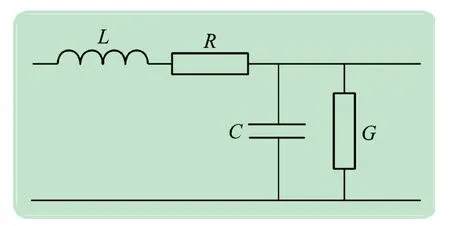

随着时钟信号频率的升高,PCB的连接线必须认为是带有电阻、电容、电感的传输线。信号频率越高,电流越趋于在导体表面流动,即趋肤效应。当时钟频率大于100 MHz或上升时间小于1 ns且互连线长度大于25.4 mm时,即出现传输线效应。分析时把传输线建模为RLGC集总模型,如图1所示。

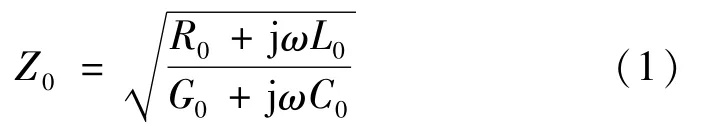

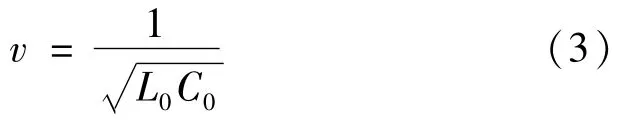

用特性阻抗Z0和传输延时Td描述传输线特性。图1中传输线模型的特性阻抗

图1 传输线RLCG模型

式中:R0为单位长度电阻;L0为单位长度电感;G0为单位长度电导;C0为单位长度电容;ω为角频率。

当频率高于10 MHz时:jωL0远大于R0;jωC0远大于G0。传输线近似为无耗线,则

此时信号传播速度为

传输延时为传输线的长度与传播速度之比

1.3 反 射

信号的反射与互连线的特性阻抗密切相关,反射形成的直接原因是互连线中阻抗发生了突变,即阻抗不匹配。

用反射系数表示反射程度

式中:Z1为阻抗突变前的区域特性阻抗;Z2为阻抗突变后的区域特性阻抗。Г越接近零,表明反射幅度越小。

用传输系数T表示信号传输质量

T越接近1,信号质量越好,衰减程度越低。

反射现象极大地影响信号传输质量,常采用端接方式使阻抗匹配以减小反射。

1.4 串 扰

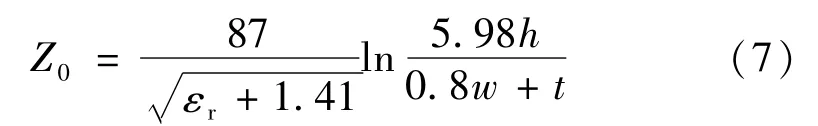

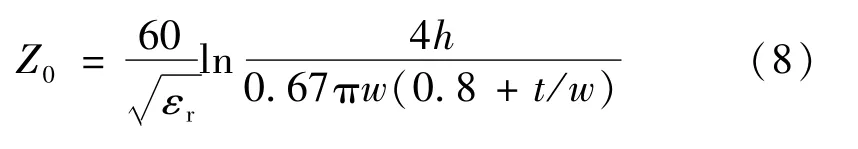

当传输线的线距较近时,激励线在静态线[16]上引起的噪声即为串扰。PCB上的串扰由耦合产生的互容、互感引起,容性耦合引起的电流分别向近端和远端流动,感性耦合引起的电流从远端流向近端。耦合的长度和信号线间的距离都会影响线与线之间信号的耦合,这也是改善串扰的两个方向。两种串扰表现不同,远端串扰是一个积累后瞬间爆发的过程,时间短、幅度大;近端串扰则是一个连续影响的过程,持续而幅值小。为研究串扰对PCB设计的影响,建立了微带线和带状线模型。微带线特性阻抗

式中:εr为PCB相对介电常数;w为导线线宽;h为介质厚度;t为导线中铜箔的厚度。

带状线特性阻抗

2 新型PCB设计方法

传统PCB设计办法周期长、成本高、依赖设计者的经验,流程越走,手段越少,时间越长。

新型PCB设计方法是在传统PCB设计办法的基础上,在布局布线前进行仿真,分析仿真结果后,结合设计要求总结出约束规则,在规则指导下进行布局布线,提前规避错误。新型PCB设计方法如图2所示。

图2 新型PCB设计方法

新方法相比传统方法,提前规避了一些错误,使得出样板后调试时间大为减少且提高了一版成功率。

3 高速高频系统设计与仿真实例

3.1 U盘系统设计

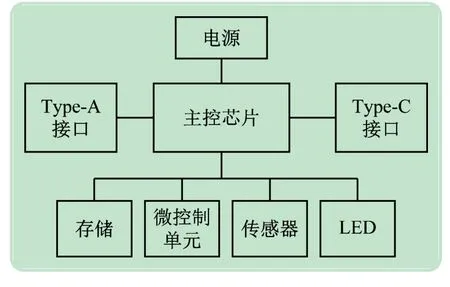

高速高频U盘的设计要求是满足USB3.1协议,具有Type-A和Type-C接口。设计框图如图3所示。

图3 U盘的设计框图

设计主要为3部分:

(1)电源部分用两个DC/DC8079AAC芯片将5 V转换成3.3 V和1.8 V,其他电压值由芯片自供;

(2)主控部分包含INIC3861S主控芯片及与它相关联的元器件和模块,如Type-C、Type-A、串行闪存等;

(3)存储控制部分由两颗紫光UNMEN05GC1C31AS 32G嵌入式多媒体卡(Embedded Multi Media Card,eMMC)构成。

3.2 U盘结构设计

U盘外观设计为53 mm×26 mm的长方形,板材使用环氧玻璃布层压板(FR4),铜箔厚度为360 μm,介质厚度254 μm。

3.3 U盘叠层设计

考虑到走线复杂度及电源分割难度,设置6层结构。L1~L6依次为top-gnd-s2-gnd-power-bottom,其中L3用于放置关键信号线,大部分走线在L1和L6表层完成。在线宽、间距同为152 μm时,用SI9000计算得出表层阻抗约为85 Ω,内层阻抗约为90 Ω。

3.4 前仿真

涉及到高速的两部分:

(1)从Type-A和Type-C到主控芯片的差分信号传输线共8对,因兼容两种接口,所以差分线的长度较长、横跨区域很大,几乎是从板的一边到另一边;

(2)主控与两颗eMMC进行数据交换的16根数据线。

前仿真主要针对以上两部分,其余低速信号线用经验法则布局布线即可,只须仿真得出最长布线长度、合适的线宽和线距。根据器件设定,设计的最高工作频率为5 GHz。

3.4.1 反射仿真测试

对线宽进行约束,计算不同线宽时的特征阻抗,阻抗越小越好,但也需考虑PCB尺寸大小,两者之间进行妥协。结果见表1。

表1 不同线宽的特性阻抗

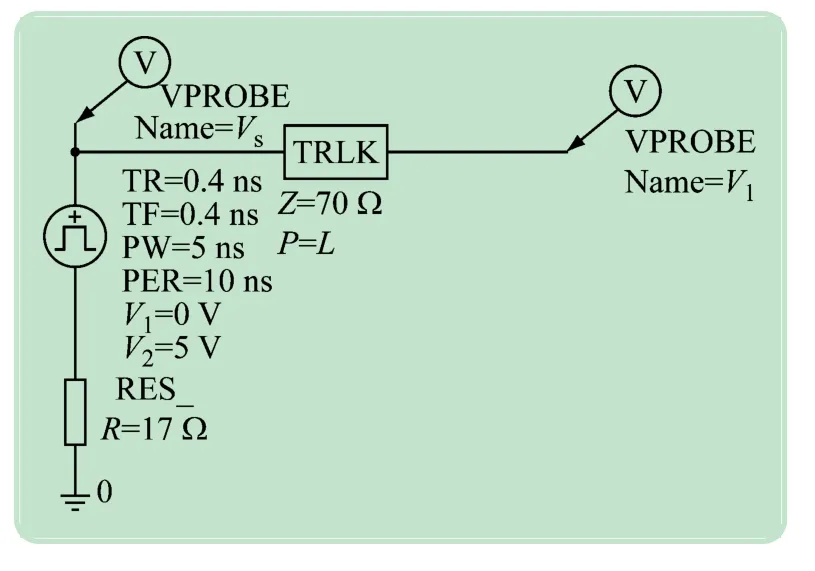

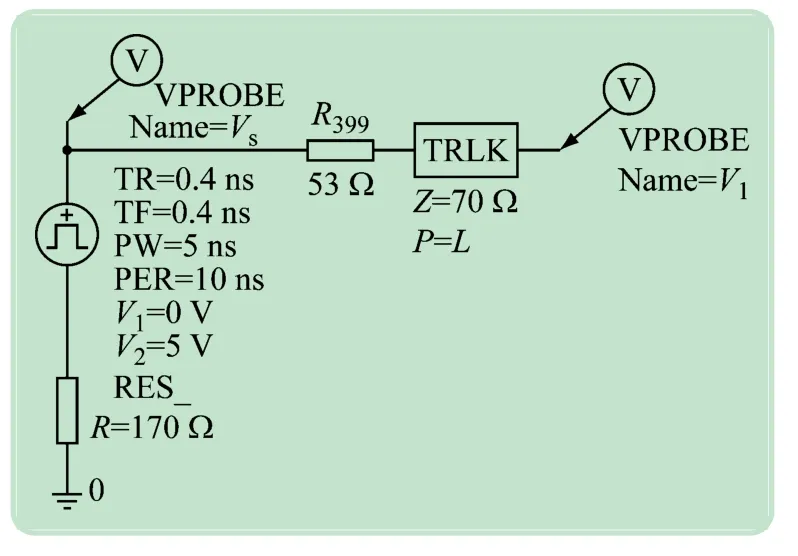

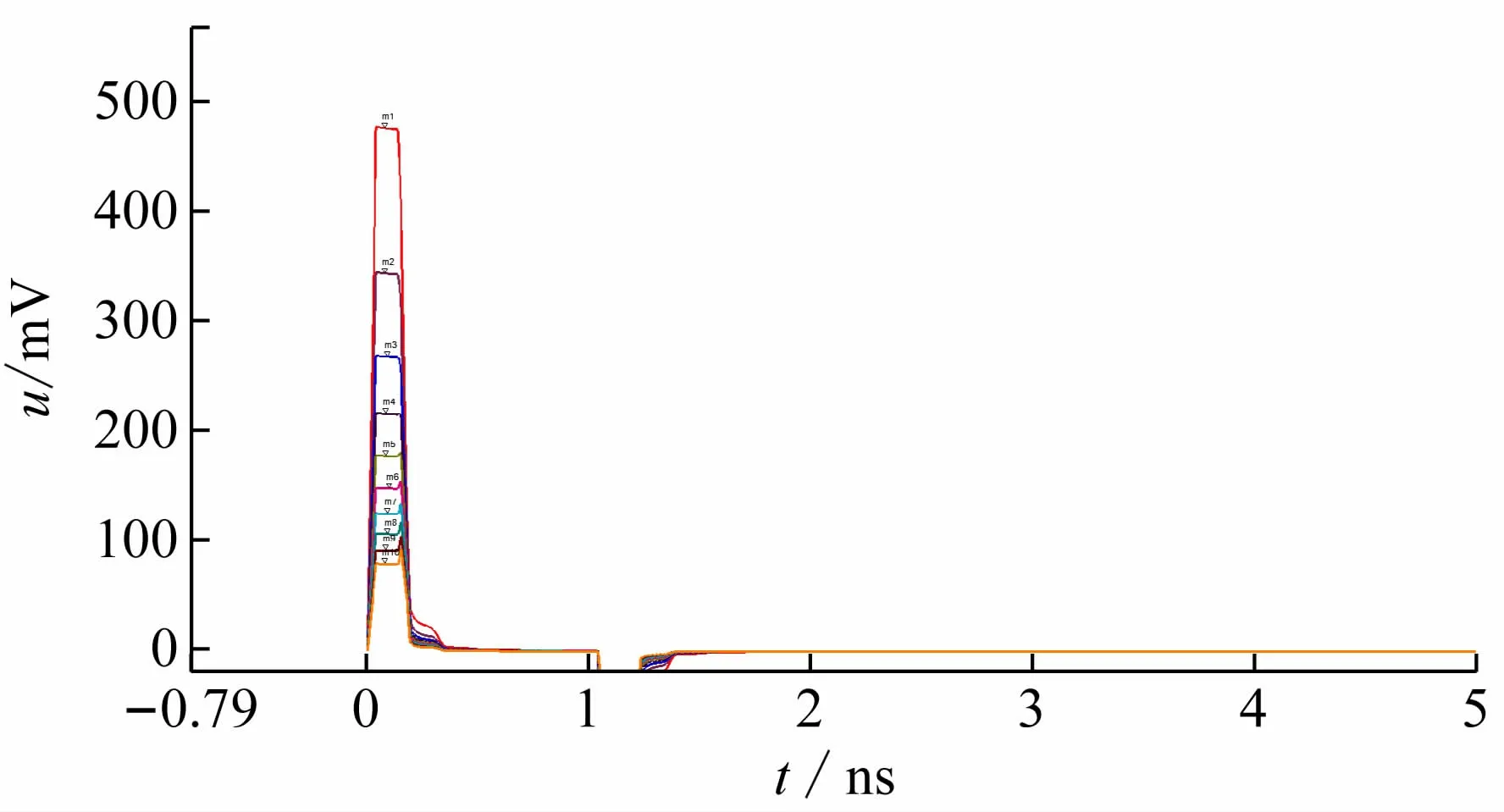

选择152.4 μm线宽,针对不同走线长度用HFSS和Designer做反射仿真测试,限制走线长度范围。图4是反射仿真模型,电源设为5 V,上升时间0.4 ns,脉宽5 ns,传输线特性阻抗设置为70 Ω。仿真传输线长度为2.54~25.4 mm的反射情况,步长2.54 mm,结果如图5所示。

图4 反射仿真模型

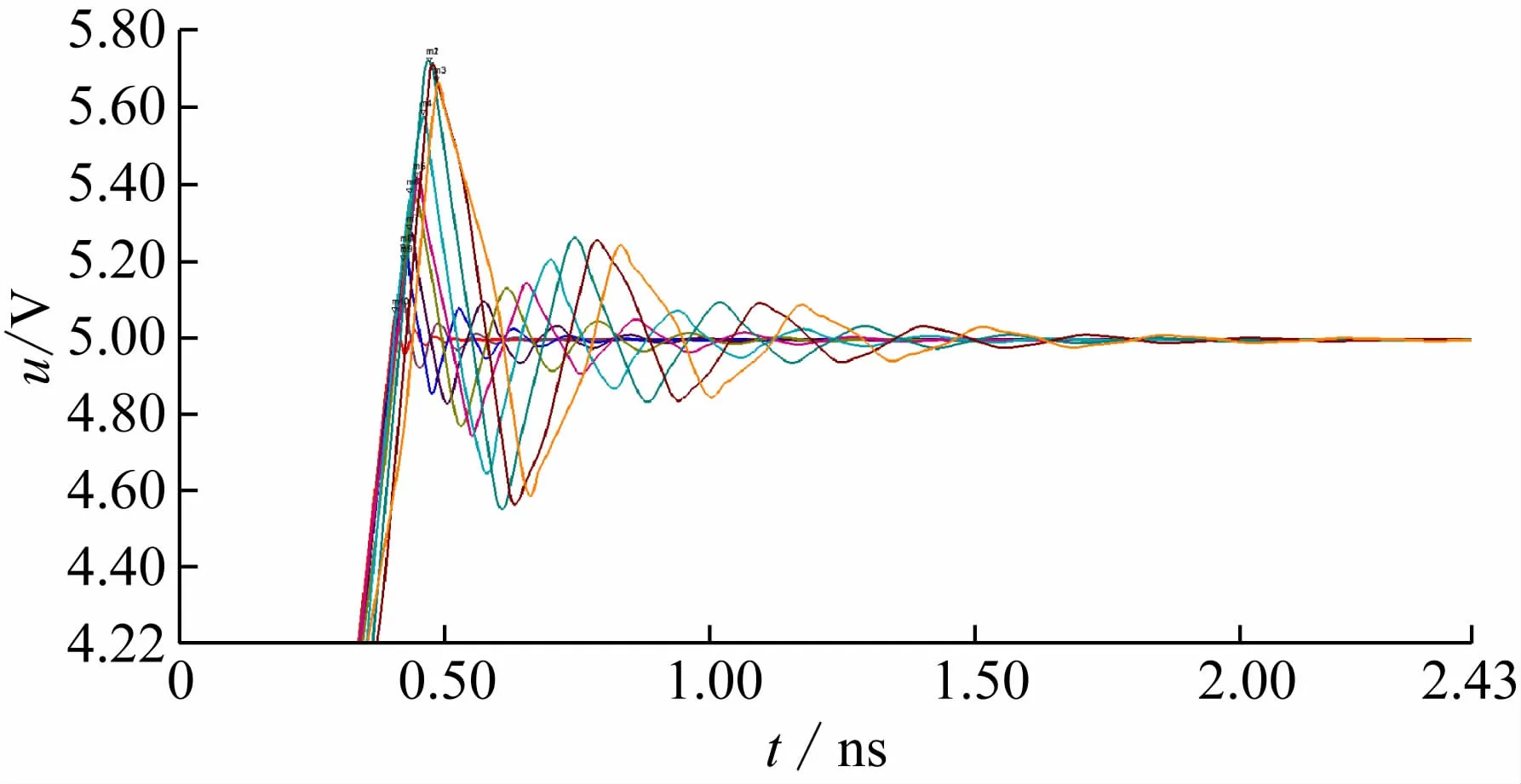

图5 反射仿真波形

由图5可见,特性阻抗70 Ω情况下,反射幅度随走线长度的增长而提高,走线长度短于7.62 mm时,反射幅度在5%以下,非常理想;走线长度在7.62~15.24 mm之间时,反射幅度在5%~10%之间;当走线长度超过15.24 mm之后,反射幅度将会超过10%。

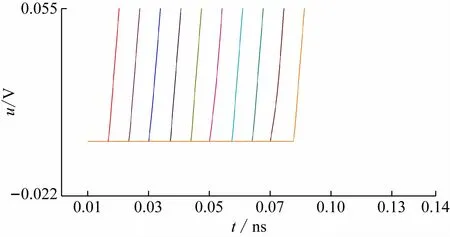

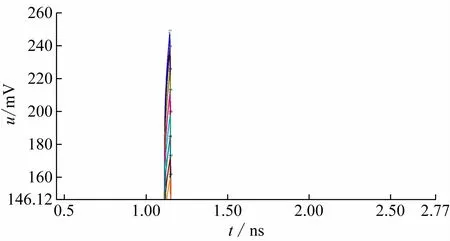

为消除反射的影响,采用串联端接法,如图6所示。仿真模型如图7所示,依据匹配原则设置端接电阻为53 Ω。仿真结果如图8、9所示,两张图是同一张仿真图的不同位置。

图6 串联端接方式

图7 串联端接模型

由图8可见,端接电阻的加入明显抑制了反射影响。经端接匹配后,反射幅度非常小。不同走线长度会影响传输时延,如图9所示,随着走线长度增加,开始跳变时间右移,传输时延增加。

图8 串联端接仿真波形1

图9 串联端接仿真波形2

3.4.2 串扰仿真测试

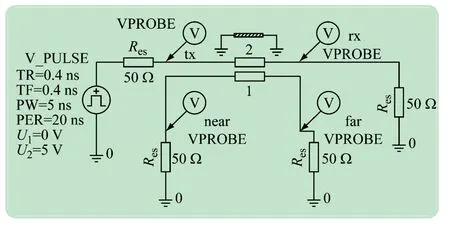

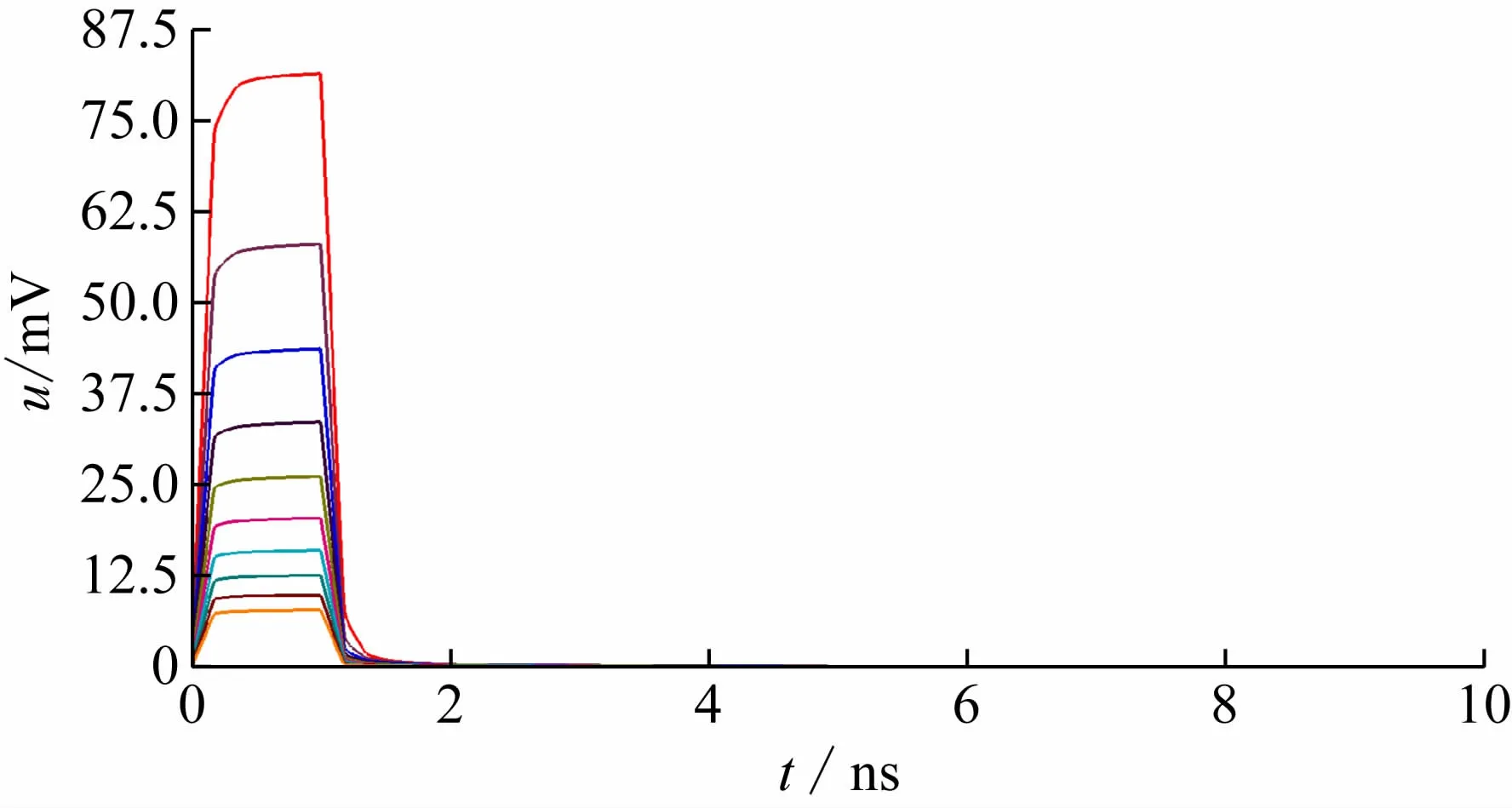

(1)微带线。设置好线宽并限制线长,再用微带线串扰仿真对线距进行约束,就能制定基本的约束规则。图10为微带线串扰仿真模型,耦合长度12.7 mm,线宽152.4 μm,电源5 V,上升时间0.04 ns,脉宽1 ns,间距为25.4~254 μm,步长25.4 μm。

图10 微带线串扰仿真模型

由图11、12可知,无论是近端串扰还是远端串扰,其幅度都随着线间距的增大而减小。当线间距大于等于101.6 μm时,串扰的幅度会小于5%。

图11 微带线近端串扰仿真波形

图12 微带线远端串扰仿真波形

(2)带状线。在Designer中选出带状线模型进行仿真。为保证结果的准确,设置参数时,将耦合长度和特性阻抗设置为与微带线仿真时相同数值,电源5 V,如图13所示。

图13 带状线串扰仿真模型图

由图14可见,线距为25.4 μm带状线远端串扰值在20 mV以下,相比于微带线,远端串扰可以忽略不计;近端串扰如图15所示,比微带线更少,只有微带线的1/6左右。由此表明,带状线更适合用于重要的信号线。

图14 带状线远端串扰仿真波形

图15 带状线近端串扰仿真波形

3.4.3 拐角走线反射仿真分析

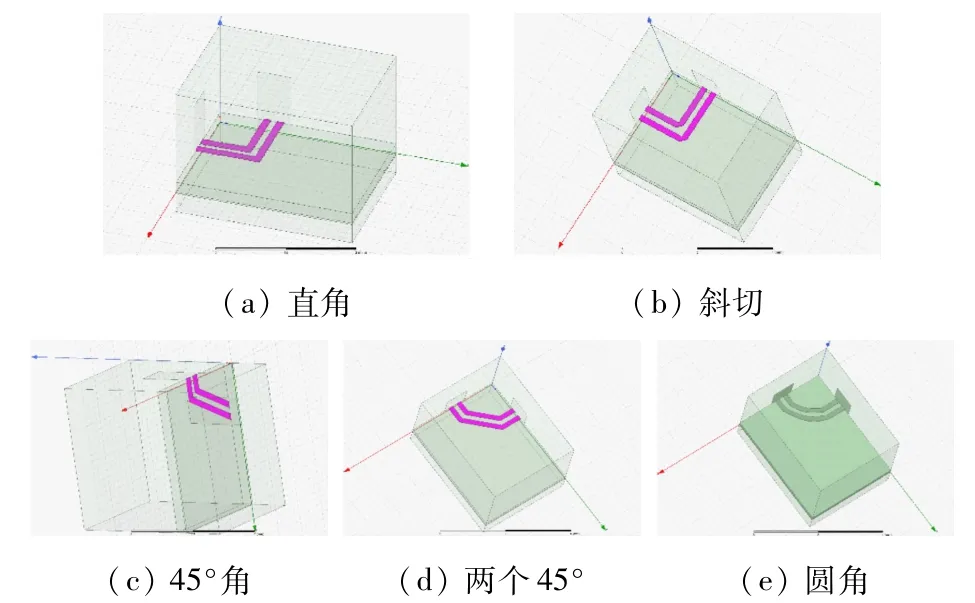

在PCB走线中,随着元器件数量和走线难度增加,拐角必然存在,拐角不同对信号产生的影响也不同。运用HFSS分别对5种不同拐角的走线进行建模,参数为参考层铜箔厚度35.56 μm、线宽152.4 μm、线距152.4 μm、厚度35.56 μm、介质厚度254 μm、材料FR4,外加空气腔体。5种拐角分别是直角、斜切、45°角、两个45°角和圆角,如图16所示。

图16 5种拐角方式

通过建模对不同频率的情况求解散射参数,表2为10 GHz时的散射参数。

表2 10 GHz时的散射参数求解

表2中,S21为正向传输系数,表示信号传输到另一端的质量,绝对值越小传输质量越好;S11为输入反射系数,表示发射端接收到的回波,绝对值越大说明反射越小。由求解数据看出,直角走线时S21绝对值最大,S11绝对值最小,有严重的反射情况;45°角走线是最理想的走线方式。另外在设置空气腔体时,不能太大,否则会增加计算量。

3.4.4 过孔参数设计

PCB的复杂度和集成度越来越高,这也意味着层数、走线难度增加,不同的过孔设计会对信号产生影响。通过设置过孔参数如焊盘大小、直径大小、长度、有无单端线(stub)、有无非功能性焊盘(non-functional pads,nfp),进行仿真对比分析。其中,stub一般指线头或歪线,nfp指过孔上没有与金属层相连的焊盘。

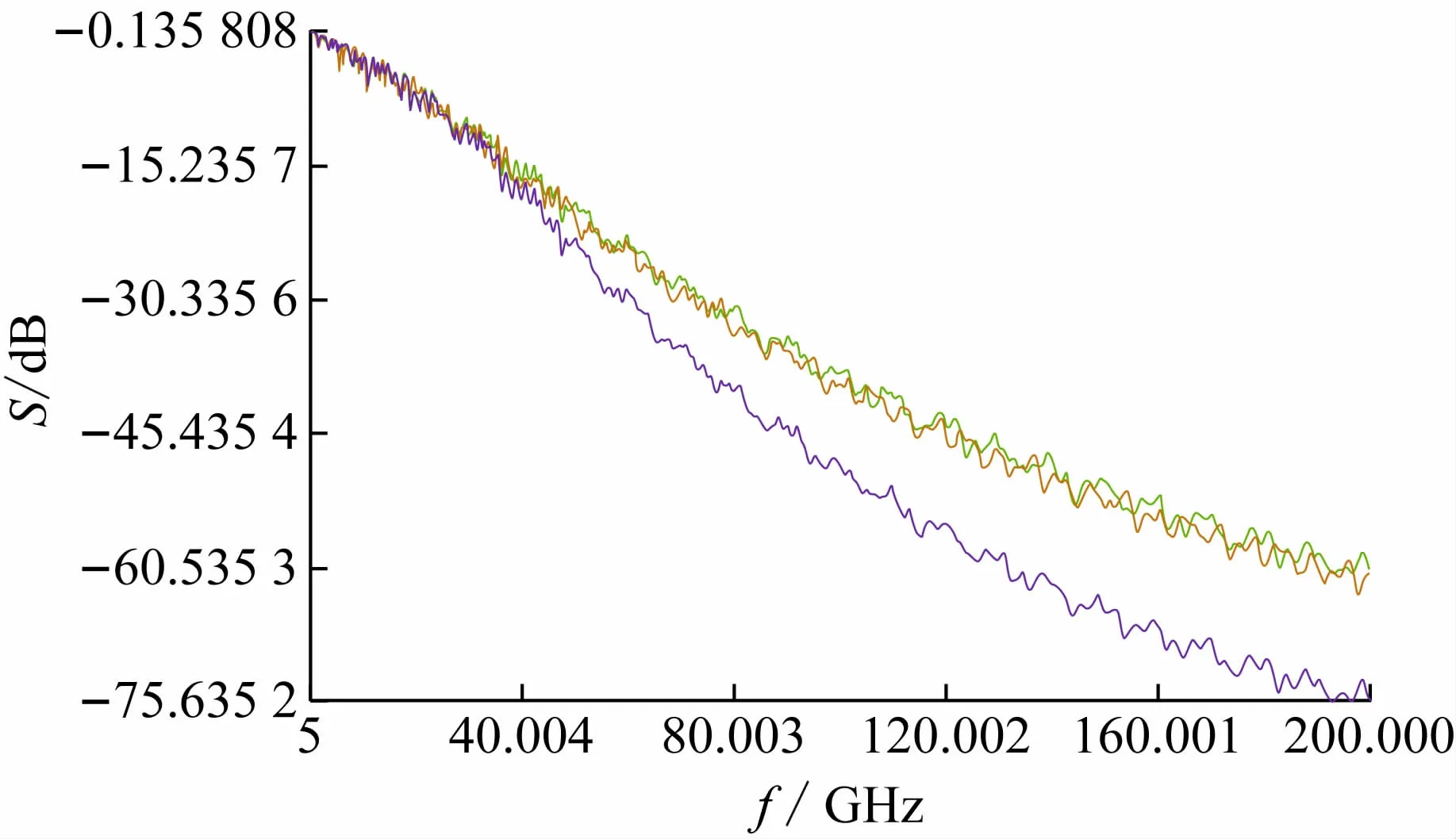

(1)过孔长度与有无stub。在SIwave软件中分别设置1~3 nostub、1~3 nfp、1~6 nfp 3种类型的过孔,比较1~3 nostub和1~3 nfp可以验证有无stub,比较1~3 nfp和1~6 nfp可以验证过孔长度。

如图17所示为过孔长度和有无stub仿真结果,由上至下,分别是1~3 nostub、1~6 nfp、1~3 nfp从一端口到另一端口的传输信号S参数波形。由图可见,如没有stub,过孔长度的增加会使线路中传输信号衰减,且随着频率越高,这种差距会拉大;而同样从第1层到第3层,无论什么频率,有stub存在都会明显出现更大的衰减。综上2项,在PCB设计中要尽量选薄的介质材料以减小过孔的长度,或在技术允许的条件下采用背钻方式在中间层走线效果更佳。

图17 传输系数

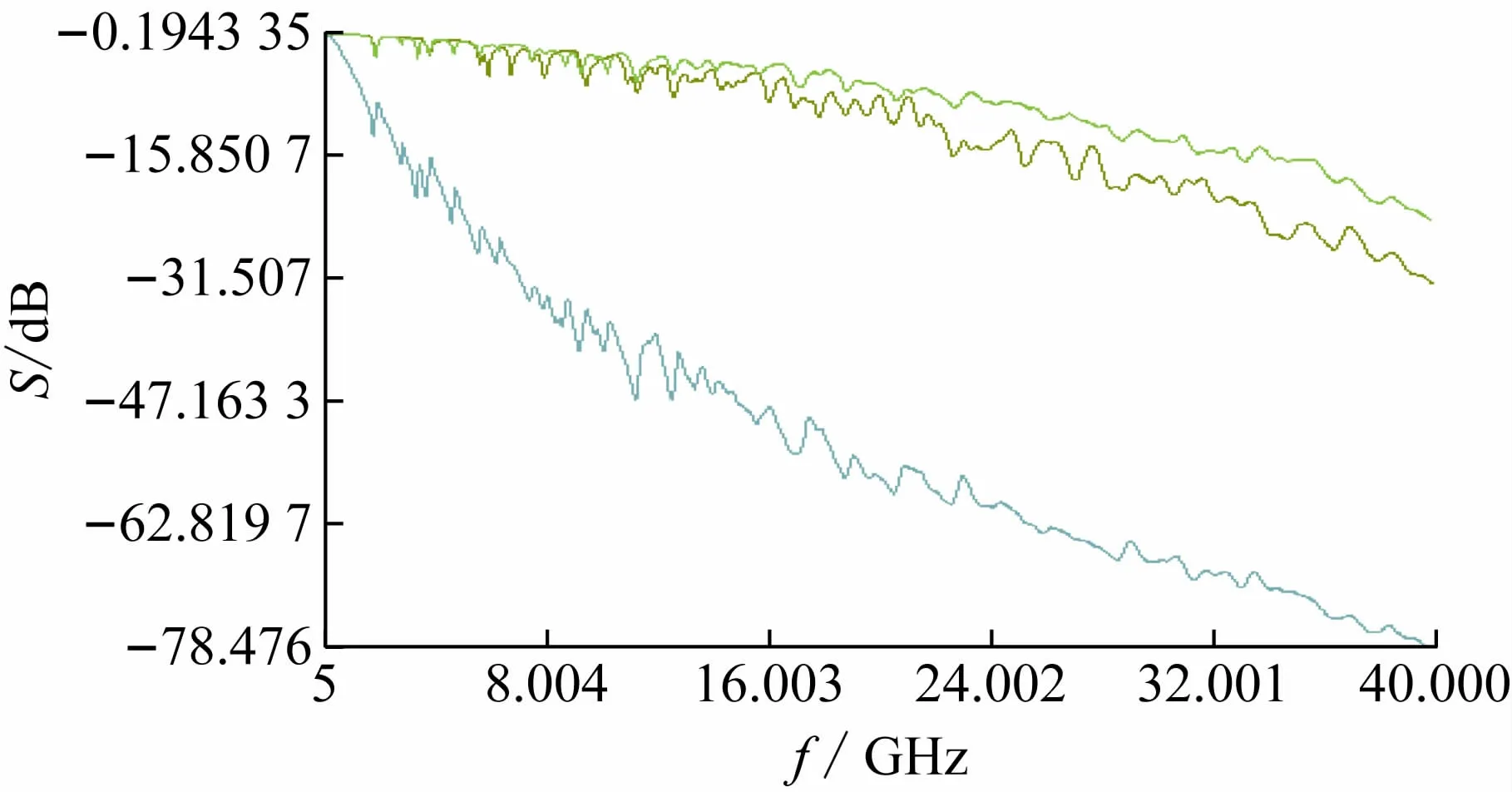

(2)不同过孔直径。在SIwave中分别设置过孔直径101.6、203.2和406.4 μm 3种过孔。通过对比不同孔直径的传输系数,得到孔直径对信号传输的影响关系。

如图18所示为不同的过孔直径仿真结果,波形由上到下分别是孔直径101.6、203.2和406.4 μm。由图可知,过孔直径越大信号衰减越大。限制过孔大小的因素有:1是工艺,要求板厚孔径比要小于5~8,否则将无法钻孔;2是载流能力,过小的孔直径无法提供足够的载流能力。比较常见的过孔直径设置有203.2和406.4 μm,并且对于203.2 μm以下的过孔,一般采用激光打孔方式,203.2 μm以上用机械打孔方式。

图18 不同过孔直径仿真结果

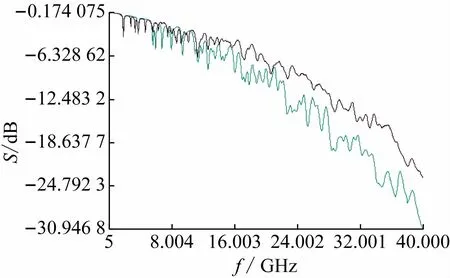

(3)不同焊盘尺寸。在SIwave中分别设置孔焊盘尺寸为127、254和508 μm 3种过孔。通过对比传输系数,得到焊盘大小对信号传输的影响关系。

如图19所示为不同焊盘大小过孔仿真结果,波形从上到下分别是焊盘大小为127、254和508 μm的过孔。平行板电容器的电容值随着板面积增大而增大,该波形显示信号随着焊盘变大而衰减得更大,可用电容理论来解释这一现象,焊盘越大则过孔的寄生电容越大,其信号衰减越大。孔焊盘的设计不能太大,满足载流和连线要求即可。

图19 不同焊盘大小过孔仿真结果

(4)反焊盘大小。在SIwave中分别设置反焊盘尺寸127、254和508 μm 3种过孔。对比传输系数,得到反焊盘大小对信号传输的影响关系。

如图20所示为不同反焊盘大小过孔仿真结果,波形从上到下分别是反焊盘尺寸大小508、254和127 μm。由图可见,反焊盘尺寸越大寄生越小,衰减越少,因此反焊盘的设计要尽量追求大一点,同时考虑反焊盘的存在会破坏参考平面,也不能无限扩大反焊盘尺寸,需要找到平衡点,甚至更多的时候要牺牲反焊盘效应,确保平面完整保证信号质量。

图20 不同反焊盘大小过孔仿真波形

(5)有无nfp。在SIwave中分别设置有无nfp 2个模型进行仿真,结果如图21所示。图中,上面是无nfp的波形,下面是有nfp的波形。结果显示无nfp的信号传输能力更好。

图21 有无nfp仿真结果

综上,在设计过孔参数时要尽量使用大反焊盘、小焊盘、短stub、短过孔长度及合适的过孔直径。

3.5 布局布线

利用PADSVX1.2软件,设定设计规则,主要是线宽线距。布线与布局同时开始,布局充分考虑布线可能出现的情况并做出预案,重要的互连线比如差分线,在主要器件布局后就先行布线,其他元器件布局时就可避开,可为差分线留出更好的环境。

3.6 后仿真验证

布线完成后对PCB覆铜,再进行设计规则检查(Design Rule Check,DRC)验证,连接无错,安全距离无错,PCB设计即完成。最后,对样板进行性能及可靠性测试。

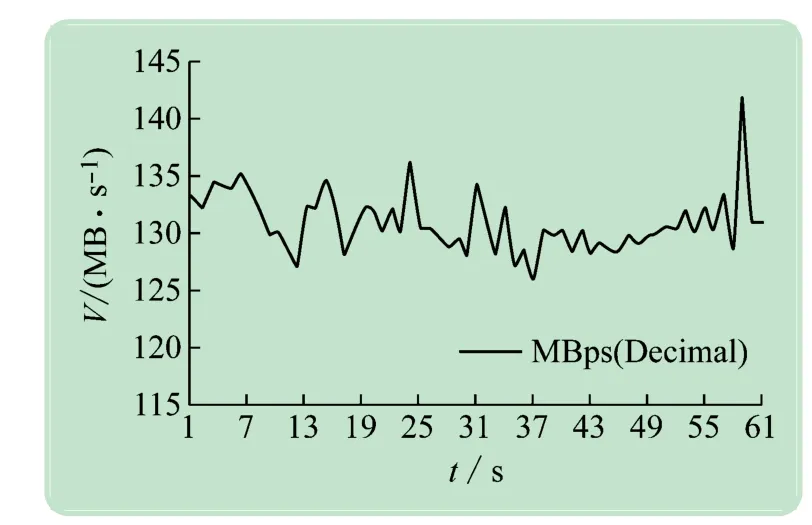

用IOmeter对输入、输出端口(Input/Output,I/O)的读写速度进行测试,分为Type-C和Type-A 2次测试,如图22、23所示。

图22 Type-C读写速度测试

图23 Type-A读写速度测试

由图22、23可知,Type-C接口读、写速度可达到150 MB/s,Type-A接口读、写速度可达到130 MB/s。

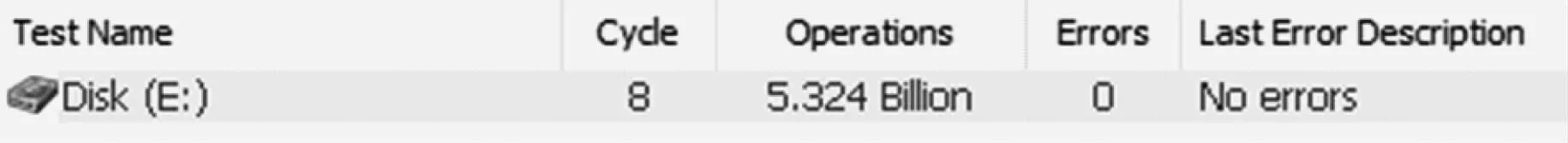

利用BurnInTest进行可靠性测试,测试内容是读、写的正确率。结果如图24所示。

图24 BurnInTest可靠性测试结果

测试结果显示无错误,正确率达到预期。

4 结 语

课程依托成果导向(Outcome based education,OBE)教育理念,以学生为中心,以成果为导向,培养学生解决复杂工程问题的能力。课程引入高速PCB信号完整性分析与设计项目,为学生充分理解“信号完整性”对产品性能的影响提供了直观、科学的分析方法,对培养学生科学工程思维和工匠精神起到积极作用。该实验项目取得了良好的教学效果:

(1)以U盘设计为载体,增强课程趣味性、培养学生的自主学习积极性,提高学生的实操实践能力和团队协作精神。

(2)从传统PCB向新型设计方法转变,运用仿真工具,培养学生的创新意识和求真务实的精神。

(3)融合多学科的知识与技能,拓展学科视野,让学生从简单的“我会”向“我能”转变,增强学生的学科素养和综合实践能力。