基本触发器、单稳态电路及多谐振荡器的统一设计和教学方法研究

沈继忠

(浙江大学 信息与电子工程学院,浙江 杭州 310027)

基本触发器、单稳态电路及多谐振荡器的统一设计和教学方法研究

沈继忠

(浙江大学 信息与电子工程学院,浙江 杭州 310027)

针对一般教科书缺乏对基本触发器、单稳态电路及多谐振荡器设计方法的论述问题,从电路存储信号需求出发,研究了基本触发器、单稳态电路及多谐振荡器间的内在联系,发现通过在基本触发器的支路中接入电容,由电容的充放电实现单稳态电路及多谐振荡器,从而提出了基本触发器、单稳态电路及多谐振荡器的统一设计方法,并在课堂上讲授。这不仅有利于学生学习和掌握这3种电路的设计方法,深入理解这3种电路的工作原理,而且可培养学生探索事物本质及其内在联系的能力。

基本触发器;单稳态电路;多谐振荡器;教学方法

基本触发器(latch)是设计各种实用触发器的基础,而触发器是数字系统中最重要的单元电路之一,在存储和计算中不可或缺;单稳态电路在脉冲波形变换中有重要作用;多谐振荡器是产生时钟信号所必需的电路,是控制与操作数字系统的关键电路之一[1-5]。

然而在一般的数字电路与系统设计的教科书中,往往只给出基本触发器、单稳态电路及多谐振荡器的电路、功能分析及参数计算,不介绍设计方法。目前尚未见对这3种电路的内在联系进行研究并提出统一设计方法的文献。

本文对基本触发器、单稳态电路及多谐振荡器的电路进行了深入研究,找到了3种电路存在的内在联系,提出了这3种电路的统一设计方法,并在大学课程教学中予以讲授,不仅帮助学生掌握这3种电路的设计方法,而且可培养学生探索电路内在联系及本质的科研思维能力。

1 基本触发器、单稳态电路及多谐振荡器设计

1.1 基本触发器设计

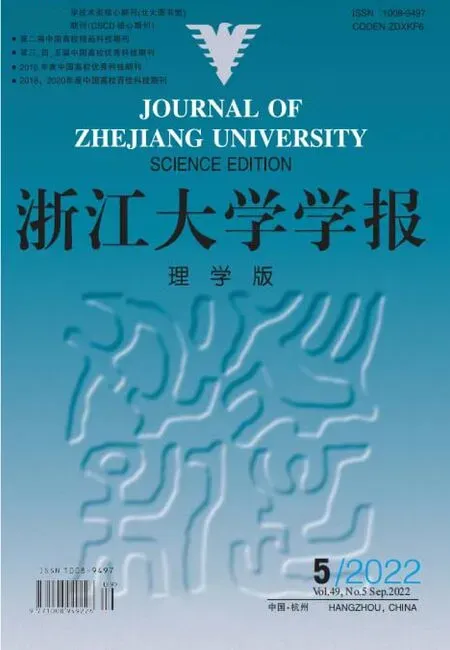

由与非门(NAND gates)组成的基本触发器如图1所示[1],表1为其逻辑功能,Q,Q*分别为触发器的现态和次态。基本触发器为双稳态电路,在外输入信号作用下,输出的Q有0或1两种逻辑值,即电路具有两种稳定的输出状态。

图1 由与非门组成的基本触发器Fig.1 Latch implemented with NAND gates

基本触发器的设计思路为,触发器的功能是保存电路的状态,即信号a(t)经过一定时间τ后保持不变:

因为电路有延迟性,即信号经过一个电路延迟后相当于保存了一段时间。所以用2个延迟时间为tpd的反相器环接,可构成存储电路,见图2。

图2 由2个反相器环接构成的存储电路Fig.2 Storage circuit composed of two inverters looped

表1 由与非门组成的基本触发器特性表Table 1 Function of latch implemented with NAND gates

注 @表示的0状态同时消失后的状态不确定。

图2所示的节点C,B与A的信号存储表达式为

由于图2中环接的反相器无法输入需要存储的信号,因此用二输入与非门代替反相器,得到如图1所示的基本触发器。当然也可用或非门代替反相器得到基本触发器。

有了基本触发器就可设计由时钟CP控制的各种电平控制触发器,进一步可设计由时钟CP跳变沿触发的各种边沿操作型触发器[1]。

1.2 单稳态电路设计

单稳态电路是一种由外界信号触发后使电路从稳定状态进入暂时稳定状态,经过一段时间后又回到稳定状态的电路。单稳态电路广泛用于脉冲电路的脉冲宽度变换、波形整形、延时等场合,具有以下特点:

(1)电路有稳定和暂稳定两种状态。

(2)在外部触发脉冲作用下,电路进入暂稳定状态,持续一段时间后,自动返回稳定状态。

(3)暂稳定状态的持续时间与电路参数有关,与触发脉冲无关。

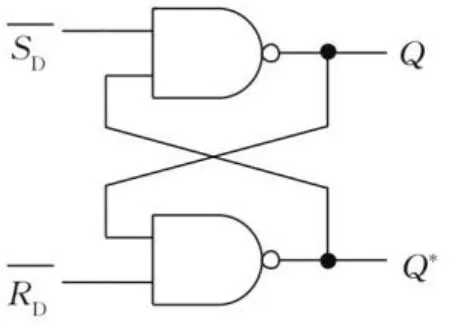

图3所示的为由TTL门构成的微分型单稳态电路,其由负脉冲触发,输出的亦为负脉冲[6]。

图3 TTL微分型单稳态电路

Fig.3 TTL differential monostable circuit

根据单稳定电路的定义,电路在外输入信号触发下,由稳定状态转变为暂稳定状态,经过一段时间后又回到原来的稳定状态,这说明电路中存在某个能使电路状态发生变化的关键节点,其电压受外输入信号触发后随时间发生变化,当该关键节点的电压变化达到某一值时,电路的输出发生翻转,使电路在经过一段时间的暂稳定状态后又回到原来的稳定状态。因电容的电压随时间的变化而变化,可在双稳态电路(基本触发器)的一条反馈支路中串接一个电容,使双稳态电路中门电路的输入端电压随电容的充放电发生变化,从而使单稳态电路自动回到稳定状态。为控制电容的充放电速度,在电容的一端连接一个电阻,使其满足电路的性能要求。同时,单稳态电路只要一个输入触发信号,双稳态电路中的一个与非门可用反相器代替,这样可得到如图4(a)所示的由负脉冲触发的单稳态电路。将图4(a)中的输入端加入微分电路,即得到图3所示的TTL微分型单稳态电路。加入微分电路后,当外部触发脉冲的宽度变化时亦不会影响单稳态电路的输出[1]。

由于图4(a)中电路所用的为与非门,与非门由逻辑0输入信号决定电路的输出,因此图4(a)中的Vi需用负脉冲触发。同时,由于图4(a)中TTL反相器G2的输入端电阻R较小且接地,当电路稳定时反相器的输入为低电平,因此电路的稳态输出为逻辑1,即稳态输出的Vo为高电平正脉冲,而暂稳态输出的Vo为负脉冲。

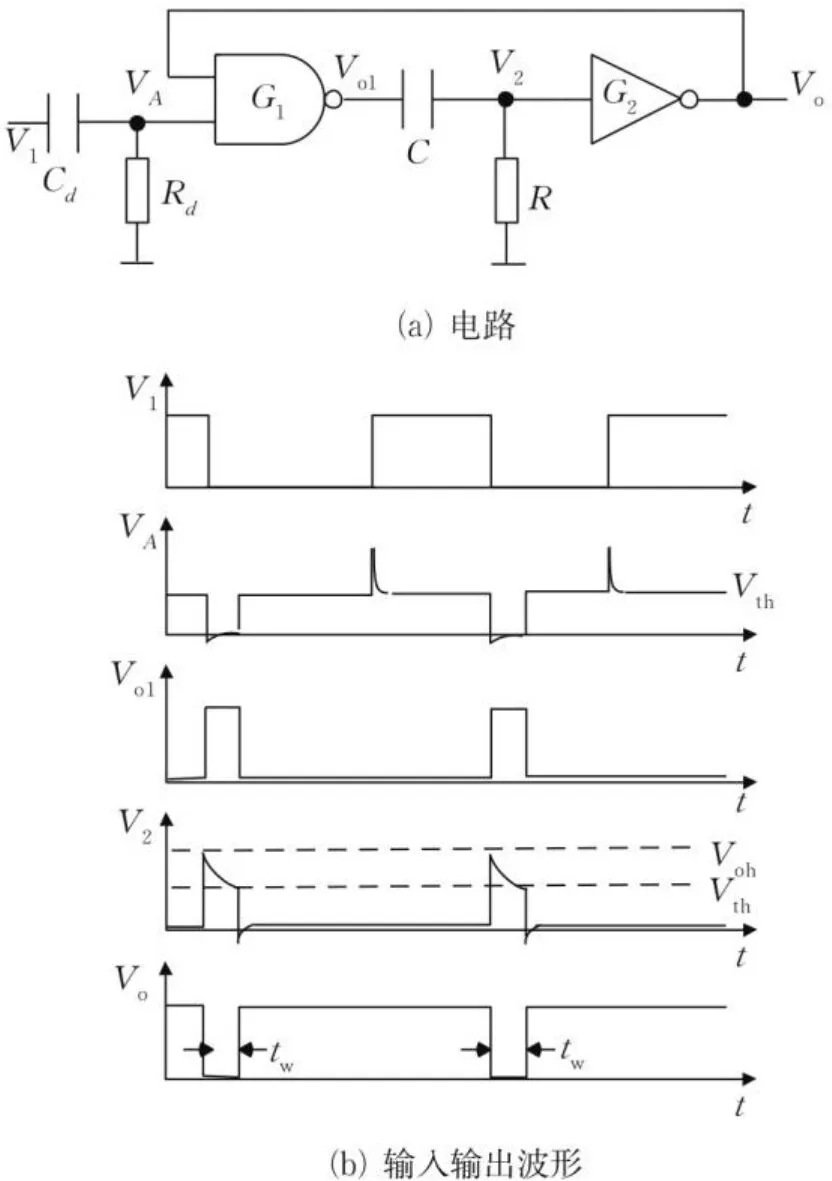

若要求电路正脉冲触发,则图4(a)的与非门用或非门代替,因为或非门由逻辑1输入信号决定电路输出。同时,若要求输出的暂稳定态为正脉冲(逻辑1),则将反相器G2输入端电阻R的一端连接电源,从而得到正脉冲触发输出为正脉冲的暂稳态电路,见图4(b)。

图4 由双稳态电路(基本触发器)设计单稳态电路

Fig.4 Monostable circuit implemented with bistable circuit (latch)

为使触发脉冲输入端Vi的宽度变化不影响单稳态电路的正常工作,需在输入端加入微分电路,由此得到实际应用中分别为负脉冲触发和正脉冲触发的微分型单稳态电路,分别见图3和图5[1, 6]。

需要说明的是,因图3中用的是TTL门,所以Rd要足够大,保证稳定状态时VA为高电平,R足够小,保证稳定状态时V2为低电平。若图3中用的是CMOS门电路,则Rd需接电源。在图5的CMOS正脉冲触发的微分型单稳态电路中,若用的是TTL门,则Rd要足够小,以保证在稳定状态时VA为低电平。

图5 CMOS正脉冲触发的微分型单稳态电路

Fig.5 CMOS differential monostable circuit triggered by positive pulse

1.3 多谐振荡器设计

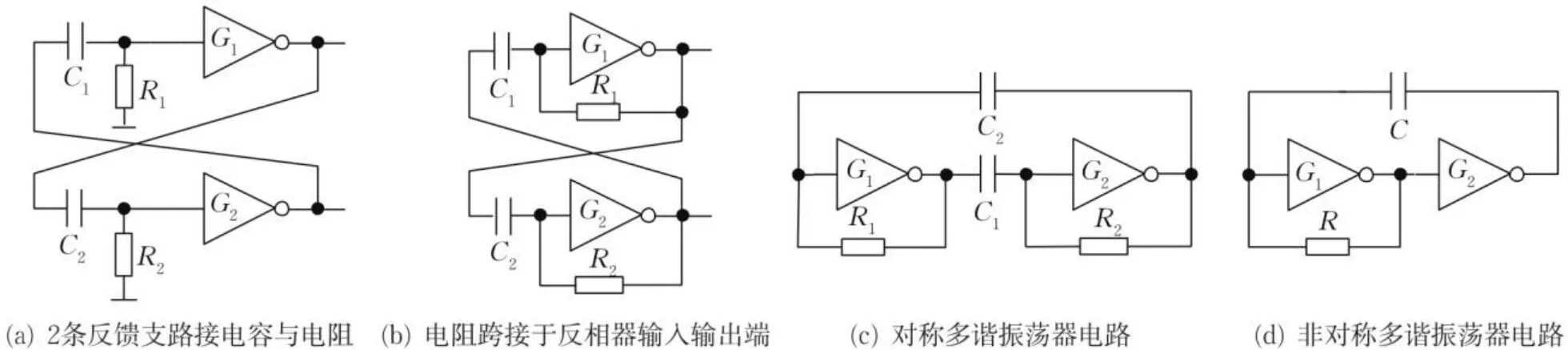

在基本触发器的一条支路上串接一个电容可形成单稳态电路,在基本触发器的2条支路上均串接电容就可形成无稳态电路,即多谐振荡器。振荡器能自己产生振荡信号,不需要输入信号。同样,为控制电容的充放电速度,即控制振荡器的振荡频率,需在反相器的输入端加接电阻,如图6(a)所示。为使多谐振荡器的输出信号在高低电平之间迅速转换,即令输出脉冲信号的边沿更陡峭,需将电阻跨接在反相器的输入输出二端,如图6(b)所示。图6(b)可转画为图6(c),即教科书上常见的对称多谐振荡器电路[1]。

图6 由双稳态电路(基本触发器)设计多谐振荡器

Fig.6 multivibrator implemented with bistable circuit (latch)

进一步,如果去掉图6(c)中一条支路上的电容与电阻,即只令一条支路不稳定,因电路无外输入,所以另一条支路也必不稳定,由此可得教科书上所介绍的非对称式多谐振荡器,如图6(d)所示[1]。

2 讨论

通过对基本触发器、单稳态电路、多谐振荡器设计过程的讨论,发现这3种电路本质上是一致的,即都以存储信息的2个首尾环接的反相器为基础,反馈支路上无电容即为双稳态电路,即基本触发器。利用电容电压随充放电变化的特性,在双稳态电路的1条或2条反馈支路上添加电容和电阻,便可形成单稳态电路或无稳态电路(多谐振荡器)。

除前面介绍的电路外,还有积分型单稳态电路、环形多谐振荡器等,本文虽没有论述这些电路的设计方法,但深入分析发现,这些电路与本文论述的电路具有相同的本质,可用同样方法予以设计。

3 结论

通过分析存储信号的原理,可知其通过2个反相器环接即可实现,而把反相器替换为具有2个输入端的与非门(或非门),便可得到能输入存储信号的基本触发器,即双稳态电路。利用电容两端的电压随充放电变化的特性,在双稳态电路的一条反馈支路上添加电容和电阻,得到单稳态电路。进一步,在双稳态电路的2条支路上均添加电容和电阻,便可得到多谐振荡器,即无稳态电路。3种电路的设计过程表明,基本触发器、单稳态电路、多谐振荡器本质上是一致的。

在教学中,按照上述思路讲解基本触发器、单稳态电路、多谐振荡器,使学生更易理解和接受,不仅帮助其掌握基本触发器、单稳态电路、多谐振荡器这3种电路的设计方法,而且通过分析,找到了这3种电路之间的内在联系,有利于培养学生探索事物本质及相互关系的能力,激发学生学习的兴趣。

[1]阎石. 数字电子技术基础[M]. 6版.北京:高等教育出版社, 2016.

YAN S. Fundamentals of Digital Electronic Technology[M]. 6 th ed. Beijing: Higher Education Press,2016.

[2]SINGH R, KHATRI R,GURJAR R C. Design of a multifunctional small digital integrated circuit (IC)using 180nm CMOS Technology[C]// 2020 4th International Conference on Electronics, Communication and Aerospace Technology (ICECA). Coimbatore: IEEE,2020: 94-98. DOI:10.1109/ICECA49313.2020.9297638

[3]TUWANUT P, KOSEEYAPORN J,WARDKEIN P. A novel monostable multivibrator circuit[C]// 2005 IEEE Region 10 International Conference TENCON. Melbourne:IEEE, 2005: 1-4.

[4]姚茂群,沈继忠,朱志刚. 单稳态触发器的结构及其开关级设计原理[J]. 电路与系统学报, 2005,10(6): 84-87. DOI:10.3969/j.issn.1007-0249. 2005.06.019

YAO M Q, SHEN J Z,ZHU Z G. The general structure and design principle of CMOS monostable multivibrator at switch-level[J]. Journal of Circuits and Systems, 2005,10(6): 84-87. DOI:10.3969/j.issn.1007-0249.2005.06.019

[5]LO Y K, CHIEN H C. Current-mode monostable multivibrators using OTRAs[J]. IEEE Transactions on Circuits and Systems II: Express Briefs,2006, 53(11):1274-1278. DOI:10.1109/TCSII.2006. 882361

[6]阎石,王红. 数字电子技术基础:学习辅导与习题解答[M]. 6版.北京:高等教育出版社, 2016.

YAN S, WANG H. Fundamentals of Digital Electronic Technology Study Guidance and Problem Solving[M]. 6 th ed. Beijing: Higher Education Press,2016.

An unified approach for designing and teaching of latch, monostable circuit and multivibrator

SHEN Jizhong

(College of Information Science and Electronic Engineering,Zhejiang University,Hangzhou310027,China)

Due to the lack of discussion on the design methods of latch, monostable circuit and multivibrator in textbooks, the internal relationship of these three kind circuits was studied from the demand of circuit storage signal. It was found that the monostable circuit and multivibrator can be realized by charging and discharging the capacitor which was connected to the latch, then the design methods of latch, monostable circuit and multivibrator were derived, and they were taught in the university courses. The new approach is conducive to studentsapos; learning on the design of these three circuits, help them to understand the performing principle of these three circuits, and train studentsapos; ability to investigate the essence and internal relationship of circuits.

latch; monostable circuit; multivibrator; teaching method

TN 78

A

1008⁃9497(2022)05⁃580⁃04

2021⁃12⁃13.

浙江大学2021年度第一批校级本科“课程思政”建设项目;浙江省2020年度省级线下一流课程项目.

沈继忠(1965—),ORCID:https://orcid.org/0000-0002-9031-2379,男,博士,教授,主要从事数字集成电路与系统设计研究, E-mail:jzshen@zju.edu.cn.

10.3785/j.issn.1008-9497.2022.05.009