自热效应下P-GaNHEMT 的阈值漂移机理*

匡维哲,周 琦,陈佳瑞,杨 凯,张 波

(电子科技大学电子薄膜与集成器件国家重点实验室,成都 610054)

1 引言

GaN HEMT 器件凭借其体积小、工作频率高、输出功率大等独特优势,现已成为半导体技术领域的研究热点。同时,P-GaN 栅增强型HEMT 器件(P-GaN HEMT)作为高频、高功率应用中的一种优选解决方案,广受国内外学术界及产业界的青睐。然而,随着高集成度、高功率密度成为P-GaN HEMT 器件的发展趋势,更显著的自热效应引发的可靠性问题已成为制约其发展的瓶颈。目前,针对GaN HEMT 器件在高环境温度下的可靠性问题,国内外已经开展了广泛研究,MILLESIMO 等[1]通过高温环境下的栅极应力实验验证了温度与栅极电压偏置是影响器件栅极经时击穿(TDGB)特性的关键因素。TALLARICO 等[2]对比了是否对栅极金属层进行刻蚀的两组器件在环境高温下的电学特性,进一步指出高温下栅极金属肖特基结的退化现象是器件特性退化的主要原因之一。尽管如此,国外针对器件温度特性的研究大多仅聚焦于外加环境高温,对于器件自热状态下的可靠性问题却鲜有文献报道,且并未对器件高温下的载流子输运机理归纳出系统的物理模型。本文提出了一种漏极电流注入技术,研究了器件在自热状态下的可靠性问题,并根据实验与Sentaurus TCAD 仿真结果建立了相应的物理机理模型。

2 器件结构及研究原理

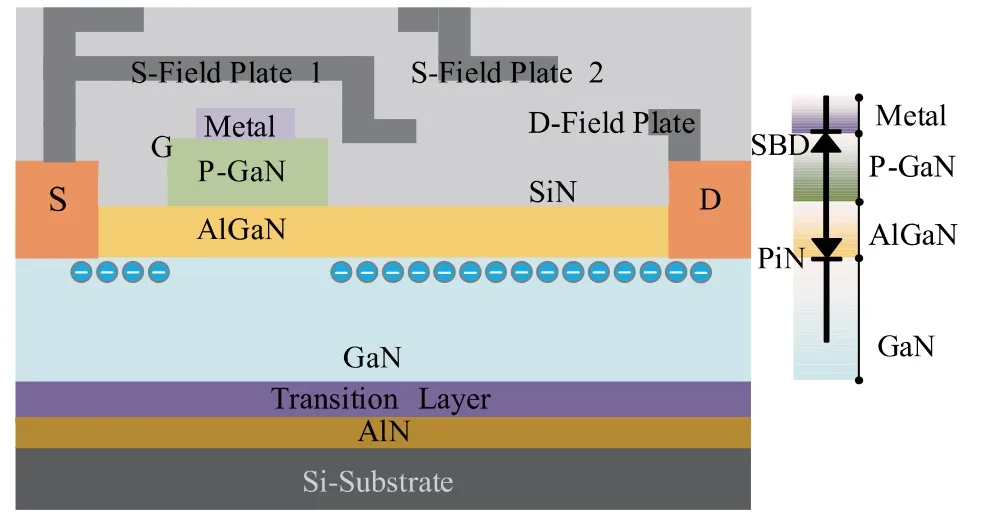

本文用于自热效应研究的器件选用商用100 V 肖特基型P-GaN HEMT,器件基本结构如图1 所示[3]。该器件的栅金属与P-GaN 层为肖特基接触,P-GaN 层与AlGaN 层接触将产生内建电势,用于提高能带并耗尽栅下沟道二维电子气(2DEG)以实现增强型,所以一般将其栅极堆叠结构等效为一个肖特基二极管(SBD)与P-i-N 二极管背靠背串联。

图1 100 V P-GaN HEMT 基本结构[3]

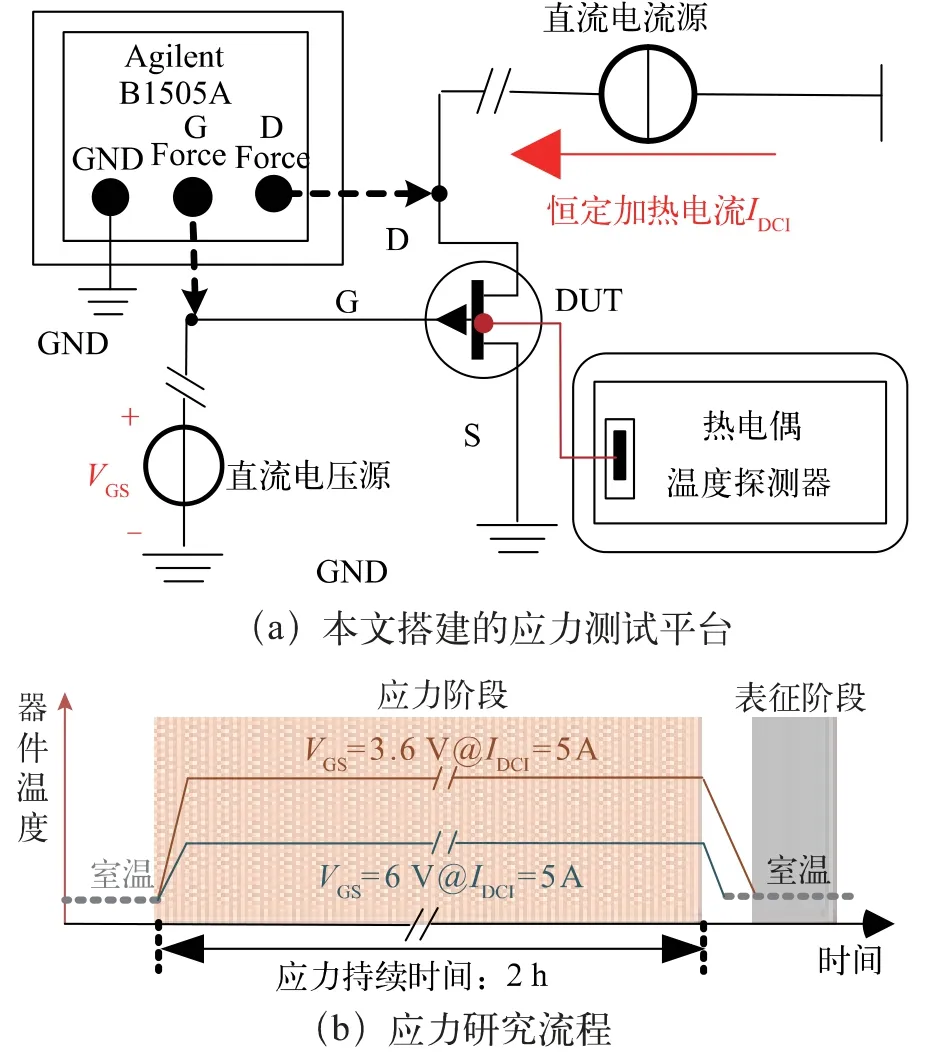

本文所搭建的测试平台如图2(a)所示,器件栅极接入一个直流电压源提供恒定栅极电压偏置,控制器件沟道开启状态;漏极接入一个直流电流源为器件注入恒定的电流,使得器件在应力阶段处于稳定的自热状态。此外,热电偶温度探测器用于监测整个应力阶段器件的温度变化;Agilent B1505A 半导体特性分析仪用于器件应力前后的典型电学特性表征。应力研究流程如图2(b)所示。首先,在室温下完成全部待测器件(DUT)的初始态电学特性表征;然后进入应力阶段,栅极电压偏置VGS先后分别设置为3.6 V 与6 V,使DUT 的沟道处于部分开启或全开启状态,用以使器件达到不同的温度状态。同时,从器件漏极注入5 A的恒定加热电流IDCI,整个应力过程共持续2 h,其目的是让器件达到热稳态并保持足够长的时间,从而产生足够的自热应力。最后,待器件温度再次冷却至室温,对器件在应力过后的电学特性进行表征。此外,整个研究过程热电偶均始终紧密贴合于器件表面,实时反馈器件温度变化。

图2 自热效应研究原理

3 研究结果

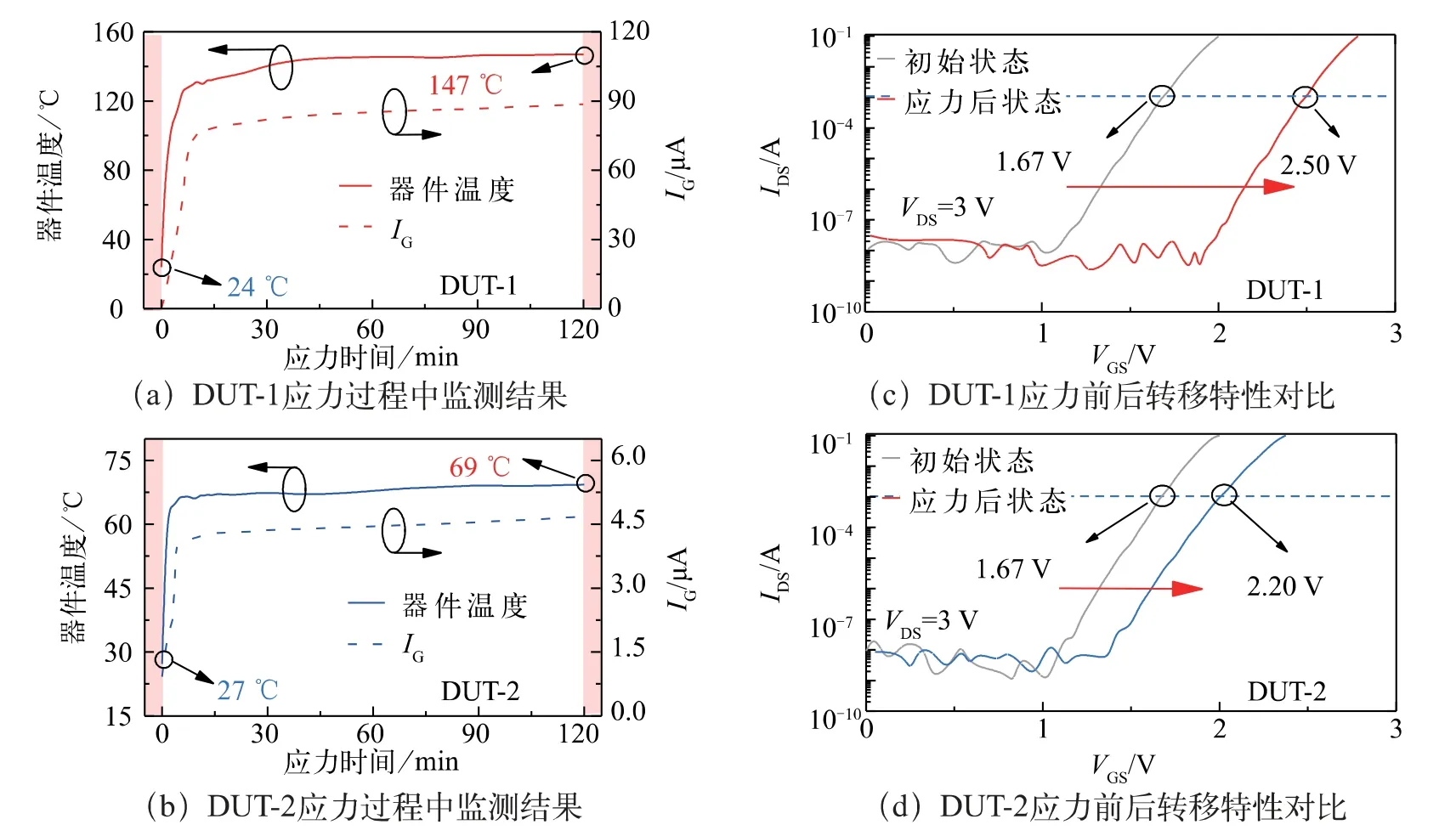

3.1 自热应力研究

第一组器件DUT-1 与DUT-2 的自热应力实验在自然环境散热条件下进行,其中DUT-1 的VGS=3.6 V,IDCI=5 A;同时,DUT-2 的VGS=6 V,IDCI与DUT-1 相同。整个应力过程中器件表面温度与栅极漏电流IG的变化如图3(a)(b)所示。器件在此测试条件下产生了显著的自热效应,且栅极漏电流随器件温度同步增大,并且在温度达到最大值时,栅极漏电流几乎同时达到最大值,且保持稳定状态。对于DUT-1,由于栅极偏置为3.6 V,2DEG 沟道处于部分开启状态,相较于DUT-2 的沟道全开启状态有更大的导通电阻,所以在漏极注入同等大小的IDCI后,DUT-1 产生的最高温度为更高的147 ℃。第一组器件应力前后的转移特性表征结果如图3(c)(d)所示,所有电学特性表征均在器件表面温度稳定到室温后再进行。两器件在应力后均呈现明显的阈值电压正向漂移现象,并且对于器件温度达到更高的DUT-1,其阈值电压的漂移量相较于温度较低的DUT-2 更大,达到了0.83 V,此程度的阈值正向漂移可能增加实际功率电路应用中额外的开关损耗,降低工作效率,甚至导致电路因工作点异常而失效。

图3 自然环境散热条件下器件特性表征结果

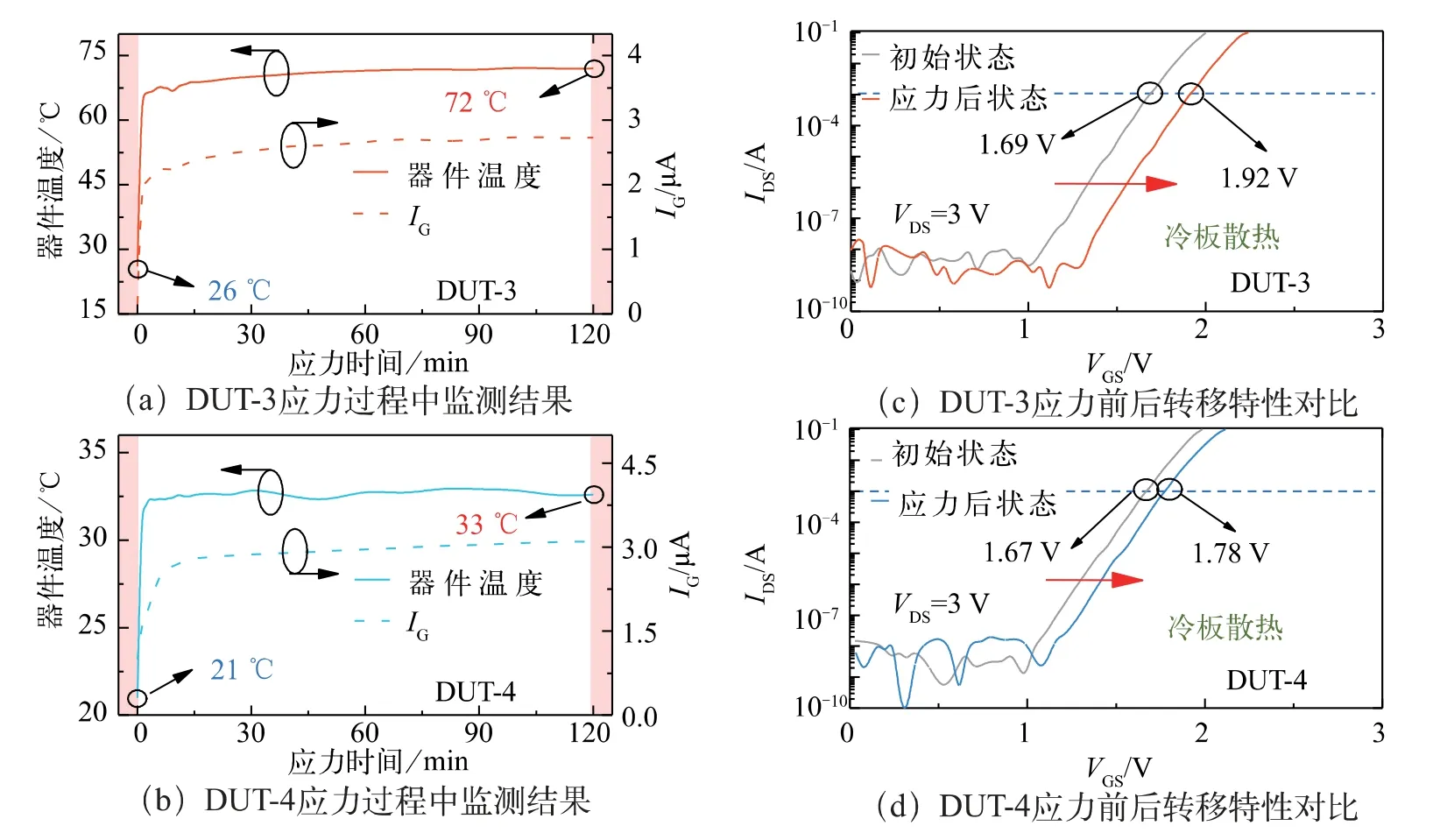

从图3 可知,器件阈值电压的正向漂移量可能与器件应力过程中能达到的最高温度密切相关,且温度越高,阈值电压漂移现象越明显。为进一步验证此猜想,改变第二组器件DUT-3 和DUT-4 的散热环境,进行第二组自热应力实验研究。第二组实验将DUT-3 和DUT-4 置于恒温冷板的散热环境下,以降低在自热过程中器件所能到达的最高温度,其余电学偏置条件均与第一组实验保持一致。冷板散热条件下的器件特性表征结果如图4 所示。相较于DUT-1 与DUT-2,器件在应力过程中的最高温度降低了约50%。冷板散热下,DUT-3 与DUT-4 的阈值电压漂移量分别为0.23 V与0.11 V。相同电学偏置条件下应力过程中能达到的最高温度更低后,器件的阈值漂移量相较于DUT-1 和DUT-2 均大幅下降。由此可知,实验中发现的阈值电压正向漂移现象主要由自热过程中器件能达到的最高温度决定,当降低器件在此过程中所能达到的最高温度后,阈值电压的漂移现象能得到显著的抑制。

图4 冷板散热条件下的器件特性表征结果

3.2 特性恢复研究

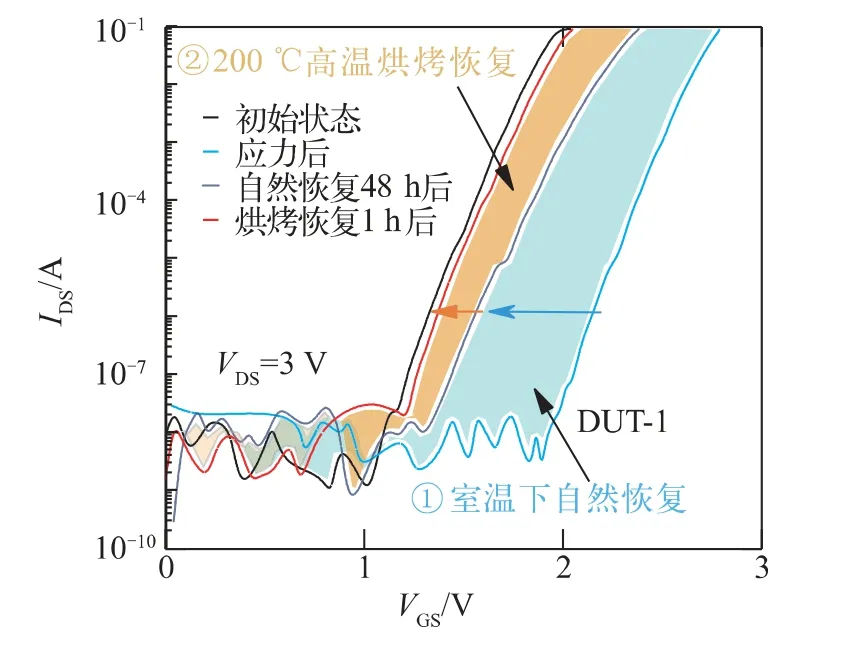

为进一步分析器件在自热过程中产生的阈值漂移现象是否为永久性退化,并深入分析产生此现象的内因及机理,针对阈值漂移最显著的DUT-1 进行特性恢复研究。将器件置于室温环境下,每间隔24 h 对器件的典型电学特性进行表征,监测器件自然恢复情况,直至器件的恢复量达到饱和,再使用恒温陶瓷夹板对器件加温烘烤1 h,观察器件是否能进一步恢复。

实验研究结果如图5 所示,器件转移特性的恢复呈两个阶段,在应力后到自然恢复时间内器件转移特性持续恢复,直到48 h 后,器件特性不发生明显恢复;对器件继续进行200 ℃高温烘烤1 h 后,转移特性进一步恢复到与初始态几乎重合,说明器件在应力过程中并未产生明显的结构损伤并且此阈值漂移现象具有可恢复性,此恢复机理与P-GaN HEMT 器件内部的载流子陷阱的捕获与释放机理相吻合。自然恢复状态下,被较浅能级位置的受主型陷阱捕获的电子会更容易满足释放条件,从而使器件转移特性能在室温下快速恢复,当大部分被浅能级陷阱捕获的电子释放完毕后,特性恢复将趋于饱和。而更深能级陷阱所捕获的电子由于需要更高的激活能才能被陷阱释放,所以室温下恢复十分缓慢,进一步的高温烘烤为陷阱内的束缚态电子提供了足够的激活能,因此被捕获的电子能加速释放使得特性得到进一步恢复,最终恢复到与初始状态相近。

图5 室温与高温下器件转移特性恢复结果

4 分析与讨论

4.1 结果分析

根据图3、4 可知,整个应力过程中除温度上升外,IG随温度的上升而上升,并且在温度达到稳定时,IG也几乎同时达到稳定,此现象既表明了阈值漂移机理的温度相关性,也进一步说明器件阈值漂移的产生可能与栅极叠层结构(Metal/P-GaN/AlGaN/GaN)中相关载流子的输运及陷阱电荷的捕获与释放机制相关。

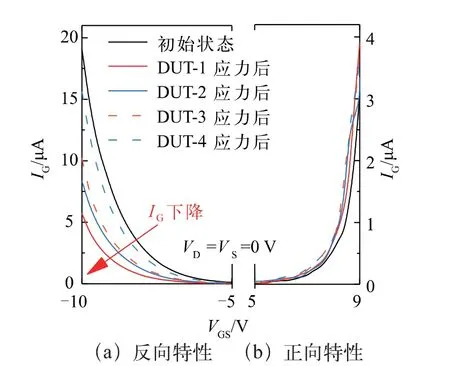

应力前后的正/反向栅极漏电流的进一步研究结果如图6 所示。从对比结果可知,应力前后反向栅极漏电流呈现减小趋势,且自热温度越高,其下降量也随之增大,同样呈现出与温度的相关性,而相较之下,正向栅极漏电几乎未发生改变。根据图1 所示的栅极等效电路结构,当栅极被施加反向电压偏置时,下方的P-i-N 二极管处于反偏阻塞状态,而上方的肖特基二极管处于正偏导通状态,绝大部分电压将降落在P-i-N 二极管上,所以栅极反向栅漏电是由P-i-N 二极管的反偏电流主导,进一步说明陷阱对电子的捕获并且其影响了栅极位置处载流子的输运机制,很大可能发生于P-GaN/AlGaN/GaN 结构中。所以,反向栅极漏电在应力后减小的原因可能是应力过程中的高温为沟道内的2DEG 提供了足够的能量而溢出沟道,部分电子将被AlGaN 层内由于工艺制造中引入的受主型陷阱捕获,使得AlGaN 层暂时出现多余的净负电荷,从而使AlGaN 层势垒高度提高,抑制P-i-N 二极管的反向漏电,导致应力后反向栅极漏电流的减小。

图6 应力前后栅极漏电流对比

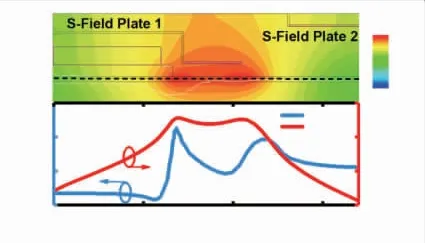

为进一步探究应力后的阈值电压漂移现象是否存在除栅极载流子输运及陷阱行为外的其他机制,对此款100 V P-GaN HEMT 器件进行了Sentaurus TCAD 建模与电热仿真分析,仿真结果如图7 所示。仿真设置栅极偏置条件为3.6 V,沟道部分开启状态,单个P-GaN HEMT 元胞,漏极偏置电流密度为108 mA/mm。仿真最高温度为160 ℃,考虑到器件结温与壳温的测量差异,此仿真温度接近于自热应力测试阶段实测温度。该器件在此自热应力下会产生两个热点,其中一个出现在靠近漏极一侧的栅极边缘,另一个出现在第一层源场板(S-Field Plate 1)的边缘处,位于栅漏接入区域。其电场也存在两个峰值,与温度峰值相对应。这说明在此应力下,器件可能在栅下与栅漏接入区域两个位置均存在载流子输运与陷阱行为。第一个热点与栅极处的电场峰值以及栅极的电压偏置共同作用于沟道电子,使电子溢出2DEG 沟道并且部分被AlGaN 层内受主型陷阱捕获;而栅漏接入区域的沟道电子在第二个热点与场板边缘的电场峰值作用下,发生了与栅极区域相似的陷阱捕获。由于器件在进行初始态标定时,栅漏区域可能已存在部分电子被本征的深能级受主型陷阱捕获填充,而在高温烘烤恢复时,栅漏接入区域内被深能级陷阱捕获的电子将获得足够的激活能而释放。

图7 100 V P-GaN HEMT 器件电热仿真结果

4.2 机理模型

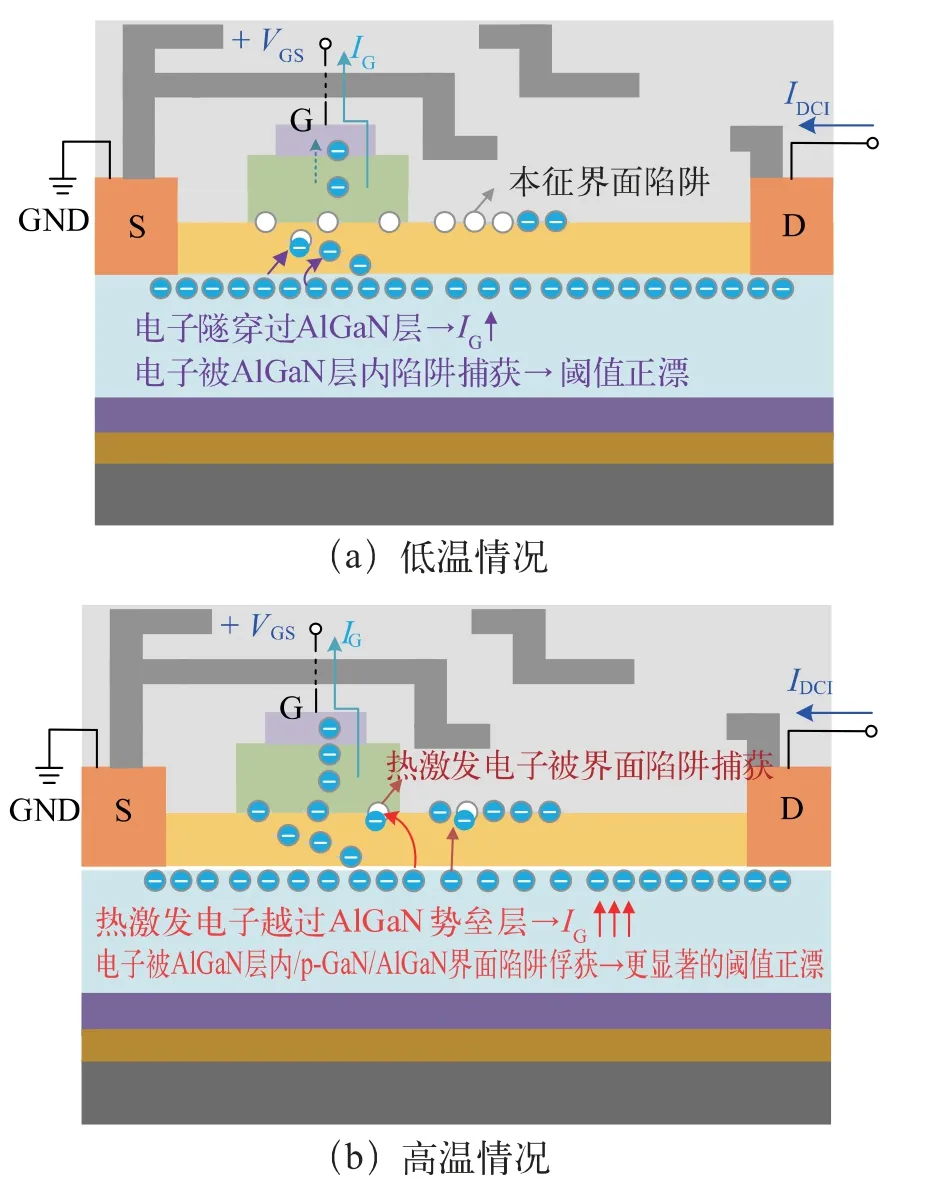

根据实验研究及仿真分析结果建立的自热效应下器件载流子输运及陷阱行为机理模型如图8 所示。除栅极区域分布有相应的受主型陷阱外,也会有部分陷阱分布于栅漏接入区,并且该区域的部分深能级本征陷阱被电子填充。

图8 载流子输运及陷阱行为机理模型

在较低的器件温度下,有部分电子从自热效应产生的热能中获得足够的能量从而溢出2DEG 沟道,但由于温度较低,部分电子并未到达P-GaN 与AlGaN界面,而被AlGaN 层内受主型陷阱捕获,从而导致P-GaN 层下方存在净负电荷,使器件在应力后出现DUT-2、DUT-3、DUT-4 所示的相对较小的阈值电压正向漂移,并抑制器件反向栅极漏电流。同时,被陷阱捕获的电子会在AlGaN 层内形成漏电通路,使得沟道电子更易发生隧穿而穿过AlGaN 势垒层,被P-GaN 层肖特基结的空间电荷区扫入金属电极而被收集,从而可观测到在施加应力的过程中,栅极漏电流呈现增大趋势。

在更高器件温度的条件下,更高的温度使沟道电子获得更大的能量,使其能越过AlGaN 势垒层,到达P-GaN/AlGaN 层界面以及SiN/AlGaN 界面。在栅极边缘第一热点及电场的作用下,热激发的电子越过AlGaN 势垒,一部分会被P-GaN/AlGaN 界面存在的界面电子陷阱捕获,导致更为显著的阈值电压的正向漂移;另一部分电子则未被界面陷阱捕获,而直接越过AlGaN 势垒层并被P-GaN 层内的空间电荷区的电场扫入栅极金属,从而在应力过程中可观测到更加明显的栅极漏电流增大的现象。同时,在第一层源场板边缘的第二热点与电场的作用下,沟道内部分电子向栅漏接入区方向溢出,被SiN 钝化层与AlGaN 层界面的电子陷阱捕获,这与电热仿真结果中的双电场与温度峰值出现的位置相对应。

5 总结

本文从P-GaN HEMT 实际高功率密度工作状态下存在的自热效应出发,提出了一种开态漏极电流注入技术,模拟器件自热状态并探究此状态下的器件可靠性问题。通过施加不同栅极偏置条件以及改变散热环境的实验方法,控制研究变量,让器件在应力下能达到不同的温度,观测到了器件阈值电压显著的正向漂移现象,并且改变量与自热过程中能达到的最高温度密切相关。从应力过程中栅极漏电流的增大与应力前后反向栅极漏电流的减小确定了栅极区域的失效位置为P-GaN/AlGaN/GaN 层所构成的P-i-N 二极管区域。

根据实验及仿真结果,建立了自热效应下器件阈值漂移现象的物理机理模型,在较低器件温度下,以溢出沟道的电子被AlGaN 层内受主型陷阱的捕获导致的辅助隧穿以及栅下净负电荷增多带来的阈值漂移占主导;而在更高器件温度下,获得足够能量后的热激发电子除以上机制外,还将进一步越过AlGaN 势垒层被扫入栅金属电极形成栅极漏电流,并有部分电子被P-GaN/AlGaN 界面陷阱捕获,从而导致更严重的阈值漂移。本研究结果进一步完善了P-GaN HEMT 自热效应下器件可靠性的理论基础,对后续的可靠性研究及加固工作有重要的参考价值。