高性能双通道稀疏采样虚拟示波器研制

姜 斌, 唐 禹, 包建荣, 唐向宏, 朱 芳

(杭州电子科技大学 通信工程学院,杭州 310018)

0 引 言

通常示波器在发展中可分为模拟和数字示波器。后者因强大的数据处理和波形分析等功能成为主流[1]。数字示波器测量信号准确度高,因成本高和不易携带,主要应用于高校及研究所,不适用于紧急通信线路抢修场景。为此,出现了针对具体应用场景,开发小巧易携带示波器产品,缺点是可扩展性差[2]。因高准确度模数转换器(Analog to Digital Converter,A/DC)售价一直较高[3],导致基于该核心器件的高端实验仪器成本高。

为消除高速A/DC对我国信号处理事业发展的影响,我国学者研发了多种等效A/DC采样技术。时间交替并行采样技术[4]为主流,该技术以较低成本实现周期及重复信号的高准确度采样,但因多片A/DC并行工作,能耗高、同步定时困难造成所需抽样样本数目多。示波器采样信号具有周期性,故频谱具有显著稀疏性。压缩采样基于信号稀疏特性,利用有限采样即可准确重构信号,可有效提升A/DC采样效率且降低能耗[5-6]。

常用压缩采样信号恢复算法主要有正交匹配追踪(Orthogonal Matching Pursuit,OMP)[5]及root-MUSIC[6],上述方法仅利用单一支撑集,易陷于局部最优,造成信号恢复不理想。多路径匹配追踪(Multiple Matching Pursuit, MMP),生成多个候选集并选择最优,有效提高信号准确度。因示波器信号采样无法预知信号稀疏度,故改进了MMP算法,获得稀疏度自适应-MMP(Sparse adaptive-MMP, SA-MMP)方法,并应用至该虚拟仪器,实现高稳定、高准确度的信号恢复,保证了带宽100 MHz、采样速率200 MS/s的双通道虚拟示波器的稳定性能。为方便现场故障排查,还扩展了信号生成,可生成5~10 MHz的常用波形。基于计算机的计算算力及硬件资源,增加了频谱仪、扫频仪以及记录仪的功能,增强实用性。研发的虚拟仪器具有功耗低,配置灵活、信号测试带宽大及扩展性强等诸多优势。

1 系统总体结构

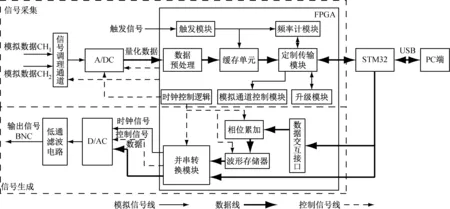

依据虚拟仪器设计思想,示波器分为硬件电路和PC端软件这两大部分。硬件采集并量化外部输入信号,依据PC指令设置生成信号波形参数,输出信号,完成信号显示及生成的功能。双通道虚拟示波器系统总体框架如图1所示。

图1 虚拟示波器总体框架图

通过功能的分类,硬件电路可分为以下几个模块:模拟信号通道、数据采集、微控制器(MCU)、个人电脑(PC)端数据处理和信号生成等模块。其中,信号采集主要由A/DC、现场可编程门列阵(FPGA)及时钟逻辑控制器等组成,基于FPGA平台压缩采样信号,可极大降低采样信号所需的能耗。PC端采用了采样离散信号,用信号重构算法恢复原始信号。重构算法的选择应遵循尽量少的采样次数实现高质量信号恢复。

2 硬件电路设计

硬件系统主要由“STM32+FPGA”构成。STM32模块以STM32F103C8T6芯片为主控制器,负责与上位机的通信及调控。FPGA选用EP1C3T100,分别控制A/DC和D/AC实现信号采集及生成功能。A/DC和D/AC分别选用ADS830E和AD5721。

2.1 信号采集电路设计

信号采集电路主要由模拟信号预处理、触发脉冲控制、信号采样通道控制、模数转换和FPGA缓存组成[8]。根据采样定理,若要准确重构信号,则A/DC工作频率不低于信号最高频率2倍,但会造成高能耗。为此,随机等效采样利用非均匀采样,依据触发脉冲与采样时钟间时间间隔存储采样值,多次采样完成波形信号重构,实现低奈奎斯特采样频率。

设采样信号时间间隔为(0,Ts],触发时刻与触发后的第1个采样时刻的上升沿的时间间隔Δtm,m为随机采样次数。触发采样脉冲理想且不重复的情况下,需要采样次数有N=Ts/Δtm。但在实际中,脉冲随机生成。故Δtm在(0,Ts]区间为非均匀分布,实际采样次数要多于N次。针对采样样本数少导致信号重构失败的问题,引入压缩采样技术。

为保证压缩采样信号准确还原,采样矩阵需便于硬件实现。在此,利用Whittaker-Shannon构建采样矩阵[5]。故采样信号y与原始信号x有下式:

(1)

式中:n为信号级数展开项的序号;m为随机采样次数,不大于准确重构原始信号最低采样次数,且m≤M;Te为等效时间采样周期。将式(1)改写为矩阵形式,则有:

y=Φx

(2)

y=Φx=ΦΨα

(3)

式中:α为稀疏度为K的稀疏信号,有效降低A/DC芯片工作负荷。

2.2 信号生成电路设计

信号生成电路利用直接数字信号合成(DDS)中的数字频率合成技术[9]。该模块主要包括主控芯片STM32、FPGA和D/AC。信号生成主要步骤如下:

步骤1PC端设置生成信号参数,依据协议编码指令,并由USB转发至STM32;

步骤2STM32解析指令,初始化D/AC,并生成指令发送至FPGA;

步骤3FPGA读取STM32指令并利用查表方式读取ROM固有波形信息,并完成相位累加、RAM读写和并串转换的时序逻辑控制,并生成指令下发至D/AC;

步骤4D/AC在时钟逻辑控制下输出对应波形。D/AC为AD5721芯片,可生成信号频率范围为:5 Hz~10 MHz。

3 软件电路设计

软件模块主要包括通信、采样、恢复及仪器驱动程序等。

3.1 通信电路设计

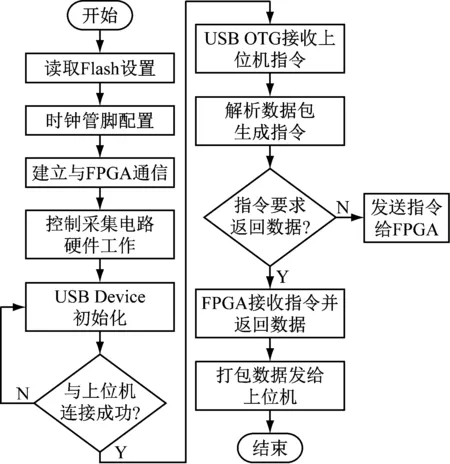

STM32作为一种集成多功能及成熟开发库的芯片,具有稳定、快速的特点,选用STM32连接硬件电路与PC通信。利用高速USB保证PC端信号稳定传输至STM32,STM32基于指令译码,并下发至FPGA及周边电路,FPGA与STM32通信流程如图2所示。

图2 STM32通信工作流程图

PC端给STM32发送初始化指令,STM32读取Flash中固有数据,初始化并设置时钟。STM32连接FPGA,采集信号并储存数据至FIFO中,将一定量的数据发送至PC端,完成信号采集。STM32作为主控模块,依据指令要求,选择生成或采样信号,基于异步通信协议激活信号采样和生成功能。

3.2 压缩采样信号恢复电路设计

压缩感知可利用有限采样样本,准确重构原始信号。但因接收端未知信号稀疏度K,故需利用穷尽方式选择性重构信号,每次采样都会造成能耗,时间及存储成本增加。信号重构需以尽量少的次数完成。

为满足上述要求,本文提出的SA-MMP算法的目标是在未知K条件下恢复原始稀疏信号。基本思想为:

(1) 估计方法估计信号稀疏度K;

(2) 基于估计得到的稀疏度K,构建深度为K的二叉搜索树模型;

(3) 利用深度搜索方式,寻求满足阈值的最优解。

按深度优先搜索的路径按次序生成,可有效避免路径重复遍历,降低存储负担。

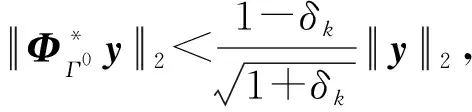

3.2.1 稀疏度估计

利用匹配测试得到原子集合,即真实稀疏度K0略小于K。假设第m次采样能够有效地恢复信号,接收信号y的真实支撑集为Ω,用|>·|表示势,有|>Ω|=K。令f=Φ*y,设f的第i个元素为fi,且f为压缩感知的中间投影矩阵变量,“*”为预设值。取|>fi|前K0(1≤K0≤N)最大值索引得集合为Ω0,则|>Ω0|=K0。因Φ满足有限等距离性质(Restricted Isometry Property,RIP)性质,故若K0≥K,且δk是预设偏差量,有:

(4)

3.2.2 稀疏多径匹配信号估计

MMP算法在OMP算法估得的索引基础上扩增候选索引集,并基于索引集扩增多个候选集,形成多个路径,类似于二叉树树形结构。将每一个候选集视作叶子节点,将残差最小候选集转化为树搜索问题。

MMP算法主要由稀疏度K及路径数S控制。每次迭代过程中,对当前候选集先通过计算内积,选出残差最为匹配的S个原子,在将该原子依据路径数分为S组,并将其加入到当前索引集,生成下一级迭代的S个索引集。经迭代,将产生多个索引集,并逐路径选择最优支撑集,实现数据重建。该算法通过增加候选集数目,提升选择正确索引的概率。但基于层序遍历的树最优解搜索,路径存在重合,需存储候选集,计算负担较大。因此,引入深度遍历搜索算法。有效避免从顶层开始计算多条路径候选集,降低计算量,提升信号重构准确度。

3.2.3 采样判决停止步骤

故采样信号采样判决停止步骤如下

图3 信号恢复流程图

3.3 仪器驱动程序模块设计

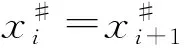

驱动程序模块主要由仪器关闭和启动、通道控制、水平控制、触发控制、数据采集、自动设置和波形生成等模块组成[9]。用户使用UI界面设置各模块参数。其功能组成框架如图4所示。

图4 仪器驱动模块组成框架图

PC端启动上位机示波器软件,发送指令初始化硬件电路,建立硬件电路与PC端的通信连接。仪器软件关闭,PC断开与硬件电路连接,释放PC端及硬件缓存。

通道控制模块主要控制信号采样通道。水平控制模块主要设置采样方式和时基挡位。

触发控制模块主要控制硬件电路触发脉冲,确保精准的时基定位,使波形稳定显示。模块主要包括2个设置,即触发方式及参数设置。触发参数因成本和硬件资源限制,主要调控是触发极性和电平。自动设置模块在系统启动时,默认设置时基和波形灵敏度。波形生成模块存储各标准生成信号,在选定某波形后,将该波形信息传输至信号生成电路,得到特定频率及幅度波形[11]。

4 虚拟示波器样机的实验测试

4.1 信号恢复性能测试

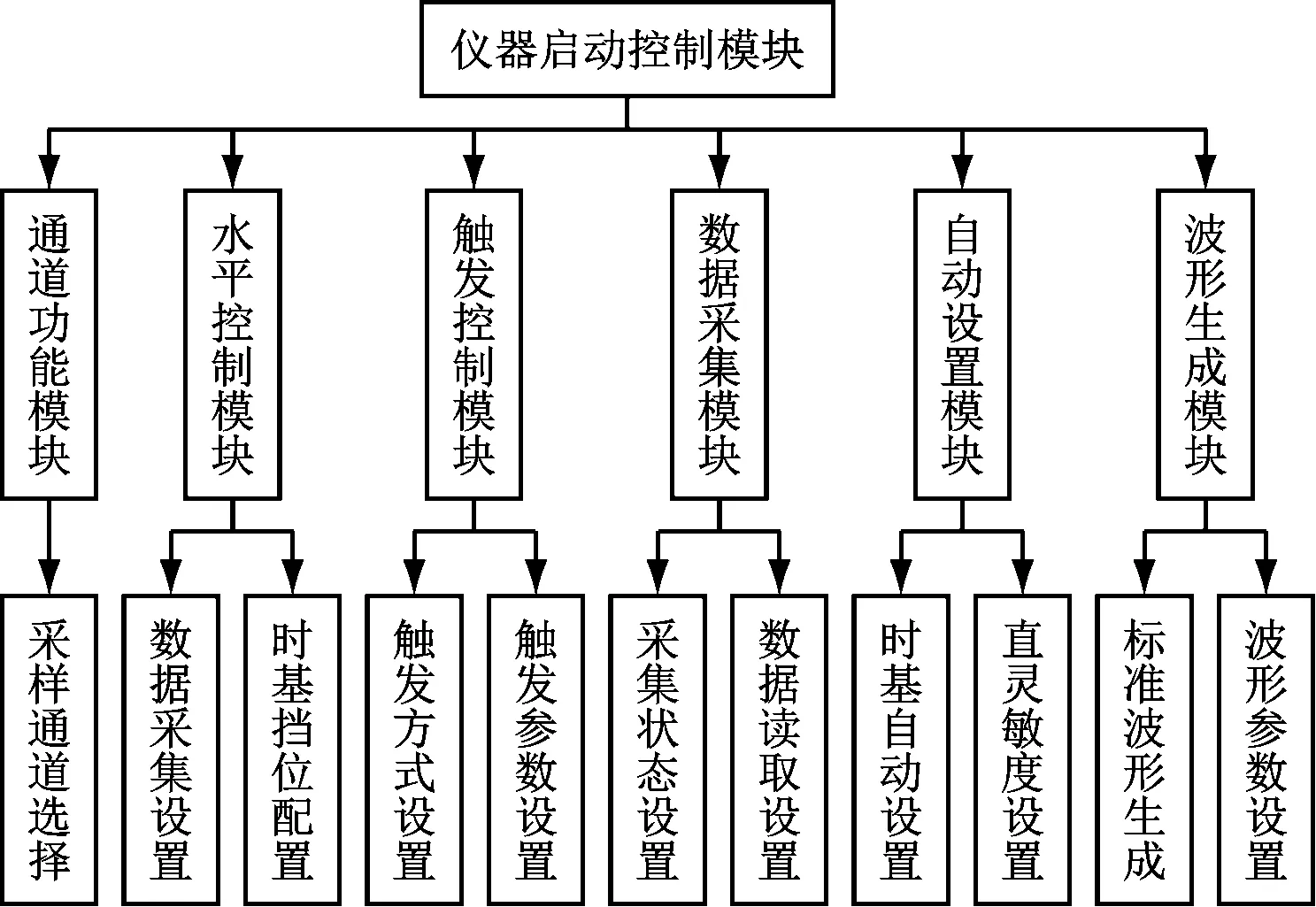

图5 不同稀疏度两种算法重构概率

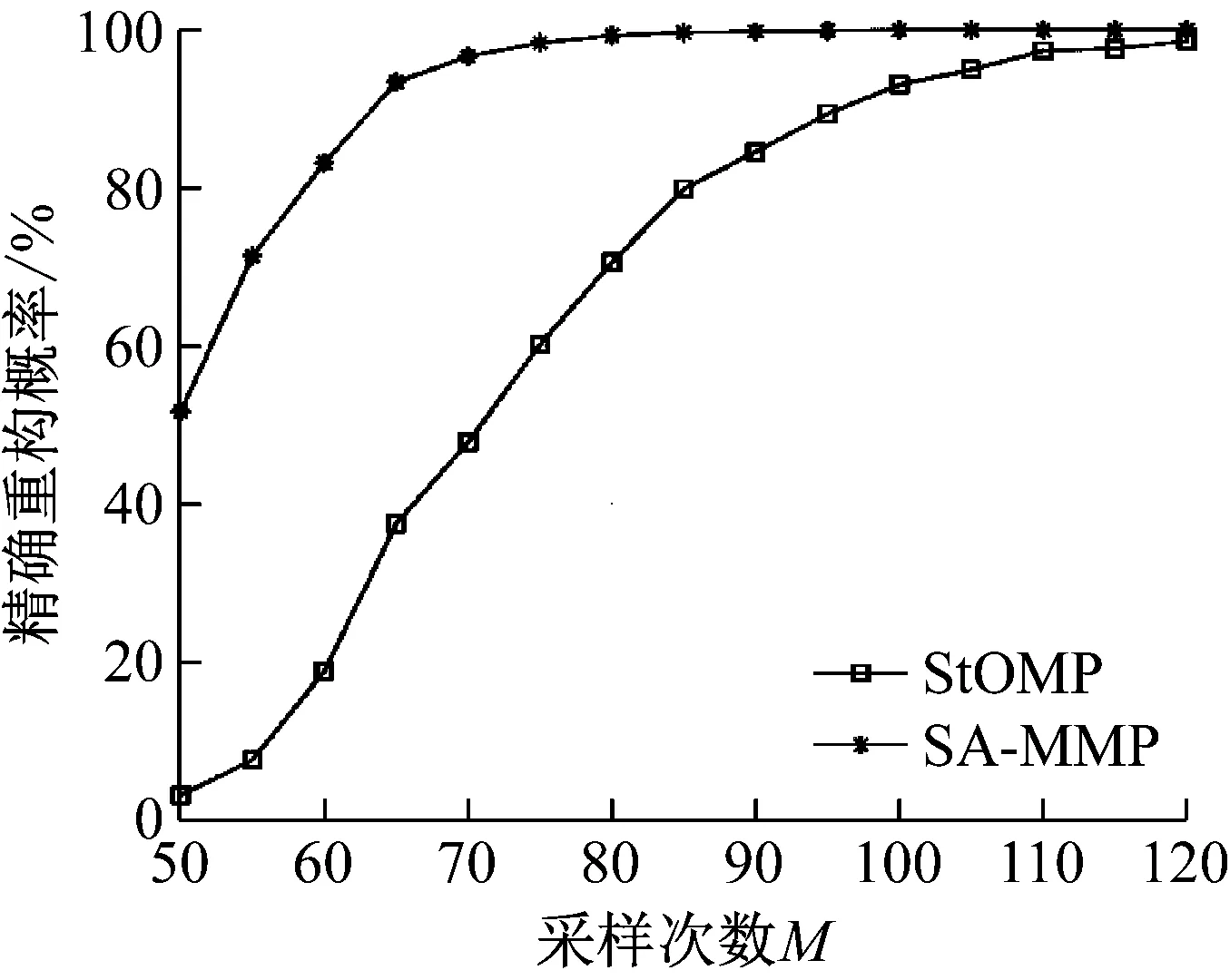

图6 不同采样数两种算法重构概率

如图5所示信号长度为256,采样矩阵为Whittaker-Shannon矩阵,采样128次,不同稀疏度对信号重构的影响。此处,稀疏度设置为[30,70],SA-MMP搜索树的宽度为4。由图6可见,本文所提SA-MMP算法要明显优于传统的OMP算法,当稀疏度K为40时,OMP算法的重构概率低于90%,之后性能将急剧下降。SA-MMP算法仍能保持100%信号重构。当稀疏度为55时,OMP算法无法重构信号,但SA-MMP仍能保持87%左右的重构概率。SA-MMP引入了多路径候选集,因此SA-MMP在较大稀疏度K仍保持良好性能。图6为稀疏度为30时,采样次数对信号重构的影响。由图6可见,当OMP实现90%以上重构成功率,则需采样95次左右。而所提算法仅需64次即可。故SA-MMP需要的采样样本数更低,并极大降低了对A/DC的准确度要求。各个压缩恢复算法的运行时间,见表1。SA-MMP因稀疏度估计原因,运行时长略高于OMP,仅相差0.41 ms,结合SA-MMP所需信号采样样本数更少,SA-MMP可实现更快信号重构。

表1 不同恢复算法CPU执行时间

4.2 虚拟示波器效果测试

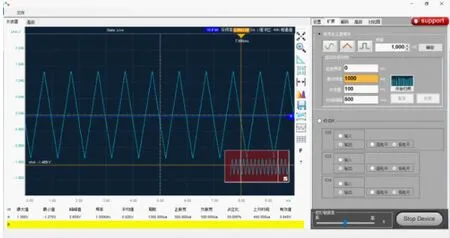

根据上述方案研制的虚拟示波器样机,同时具备示波器以及信号发生器功能。将PC端通过USB与硬件电路相连接,启动软件,点击“Start Device”启动示波器功能,点击右侧的“高级”设置信号发生输出信号参数。

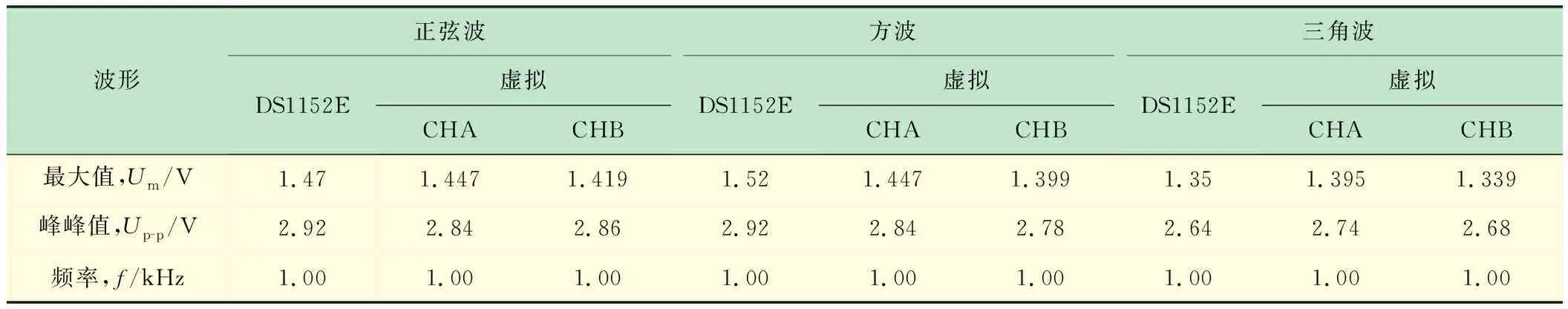

图7所示为示波器系统测试图。分别连接信号发生端至数字示波器DS1152E及虚拟示波器,输出频率为1 kHz的不同波形。收集不同情形虚拟示波器与数字示波器测量结果,结果见表2。由表2可见,虚拟示波器能够准确测定信号频率,幅值测量尚存在一定误差。但信号误差波动也仅在1%~3%,基本满足日常实验教学所需。

图7 系统工作效果测试

表2 虚拟数字示波器测量结果对比

除实现示波器及信号发生器功能外,还可进一步扩展软件功能。基于硬件电路信号采集功能,对采样插值后的数据做离散傅里叶变换(Discrete Fourier Transform,DFT),可得到信号频域数据,将数据在PC端显示得到频谱分析仪的功能,如图8所示。利用PC端可控制生成信号频率,设置步进频率,可输出扫频信号,实现扫频仪功能,如图9所示。

图8 频谱分析仪功能界面

图9 信号发生器和扫频仪功能界面

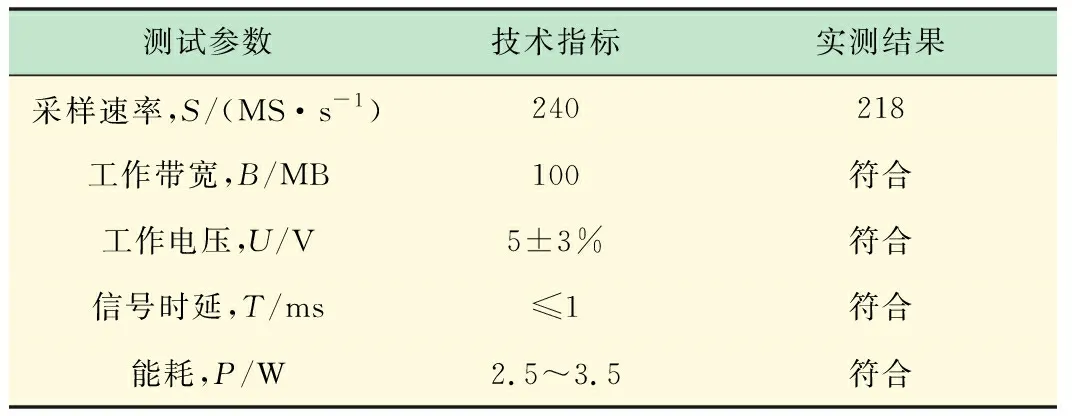

此外,为方便工程师回顾历史数据波形,增加了无纸记录仪的功能。点击REC 按钮即可对当前的波形进行记录,以星号*.osc文件名保存,记录容量大小受限于计算机存储容量。实现上述功能后,进一步测试示波器硬件电路的各项指标,由表3可得到结论:各项参数基本符合项目目标要求。

表3 虚拟示波器硬件电路模块各项参数

5 结 语

本文主要论述了基于稀疏采样的高性能双通道虚拟示波器的研制。该虚拟示波器采用STM32F103作为主控芯片,利用EP1C3T100和其他外围电路实现了示波器、信号发生器功能。为提升信号采样效率,利用FPGA芯片丰富的存储计算资源,基于非均匀采样采样信号,利用SA-MMP恢复信号,实现信号高质量测量、恢复。为充分利用硬件资源,进一步扩展频谱仪,信号发生器的软件功能[15]。该示波器具有体积小、易携带和多功能等特点,具有广阔应用市场,可为同类产品设计提供借鉴思路。