高速光纤通信网络总线链路的设计与实现*

刘 畅

(中国空空导弹研究院,河南 洛阳 471009)

0 引言

通信技术自古至今都是工业发展、人类日常生活中不可或缺的关键技术,随着当代控制测量系统中信息交互和传输数据量的增加,处理数据也变得复杂,能够让信息实时、准确、快速地传输成了一个不小的难题,链路是组成总线网络的基石,也是总线通信质量的关键,总线网络中高速通信链路的设计与改进是解决以上问题的关键。

传统的航天测试总线系统中,传感器、变换器设备分布较为零散,仪器间普遍采用点对点连接的电缆网进行信号传输。这种布线方式需要使用大量电缆,电缆中传输的模拟信号容易受到干扰,繁杂的连接线路降低了系统的可靠性,且带宽大大受阻,光纤凭借着较长的中继距离、大容量、宽频带、抗干扰性好等优势,以光纤作为传输主干的通信系统应运而生。因此,考虑将长中继距离、大容量、宽频带、抗干扰性好的光纤作为传输介质,以运算速度快、编程简易的FPGA 作为嵌入式系统的核心,设计出了高速数据传输链路应用于总线。

本设计将研制出以光纤作为传输媒介的更高速、更灵活、高可靠性的通信总线链路,以保证相关高速数据传输信号的质量。为了实时地观察和分析总线网络数据,总线网络通过网口与计算机进行数据传输,简化了原有测试系统的复杂结构,在提高总线数据传输速度和质量的基础上使链路可靠性提高,灵活性增强,设计周期被大大缩短,成本低且易于维护。

1 总线通信链路发展概要

总线通信技术最早出现在美国惠普1972 年提出的HP-IB,用于仪器与计算机之间的通信标准,后来渐渐演变为GPIB,直到VXI 总线被提出,它将总线易于操作和吞吐量高等优势展现了出来,目前总线朝着更加高速、稳定、可靠的方向迅猛发展。

近年来,我国在总线领域发展迅速。2012 年,第一代RS422 分布式测控仪器总线为多个航天设备提供了总线支持,但通信灵活性较差,速度较慢,传输距离不能满足通讯领域日益发展的需求;2017年,该总线升级为最新一代LVDS 有限级联自构网络仪器总线,在网络协议、网络架构、速率提升等方面较2012 年有较大改动与提高。LVDS 数据传输速度达200 Mb/s,适应性极强,从任何一个终端接口接入,可与全网所有终端通讯。

2 总体方案设计

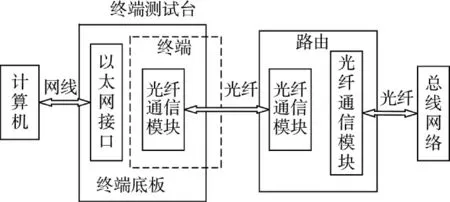

链路整体方案设计由计算机、终端测试台、路由和总线网络组成;总线网络中各设备之间均通过光纤通信模块进行数据交互,网络中的数据由计算机通过光纤通信接口传输至路由设备,路由与终端测试台之间通过光纤通信接口完成数据的接收与回放,光纤通信接口在数据收发的过程中可以完成光与电信号之间的转换,调配FPGA 中的吉比特率收发器核(gigabit transceiver intellectual property,GTX IP)将高速串行数据转化为低速并行数据,以太网底板将通过终端测试台的数据编成传输控制协议及互联网协议(transmission control protocol/internet protocol address,TCP/IP)可识别的帧数据形式,上传到计算机,计算机作为监控工具的同时也方便数据处理和命令下发。链路总体方案如图1 所示。

图1 链路总体方案

3 硬件设计

3.1 FPGA 控制模块

FPGA 作为本系统的主控芯片,具有强大的高速数据处理能力和灵活的用户接口协议,以及多I/O 口,低功耗,价格低廉等优点,此处选用具备16个GTX 的Kintex-7 系列FPGA XC7K480T,其自带32 路高速GTX 串行高速收发器通道,每通道的收发器速度高达12.5 Gb/s,可以实现数据的高速传输。XC7K480T 是SRAM 型的FPGA,这种芯片需外部配置芯片,否则掉电数据会丢失。

本课题中需要将配置文件下载到外部存储器中,所用到的是SPI 配置模式,每次上电后FPGA 从外部存储器加载程序进行工作,保证下电后数据不会丢失。N25Q128 是Numonyx(恒忆)的128 Mbit 串行Flash,工作电压范围为1.7 V~2 V,串行FLASH相比并行FLASH 所需要的引脚少,采用SO16 的小体积封装,能很大程度上节省电路板空间、功率和噪声,下页图2 为FPGA 配置的电路连接图。

图2 FPGA 配置电路

3.2 光纤通信模块

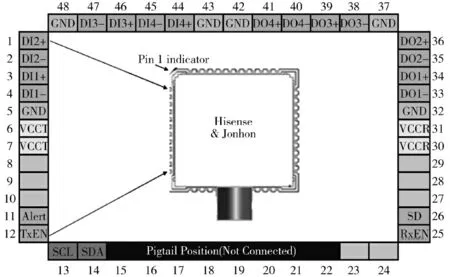

光电转化模块采用的是HTA8525 四路并行光收发一体光模块,单路速率最高可达10.312 5 Gb/s,主要应用于并列多通道光互联数据通信。其采用MT 式尾纤接口和LCC48 电气接口封装形式,具有辐射小,有较强的抗干扰能力,-55 ℃~85 ℃的环境工作范围,可广泛应用于背板互联、雷达与处理机互联、并行光互联等,车载、机载、舰载等环境均可适用,光电模块连接引脚图如图3 所示。

图3 光电模块连接引脚图

3.3 以太网模块

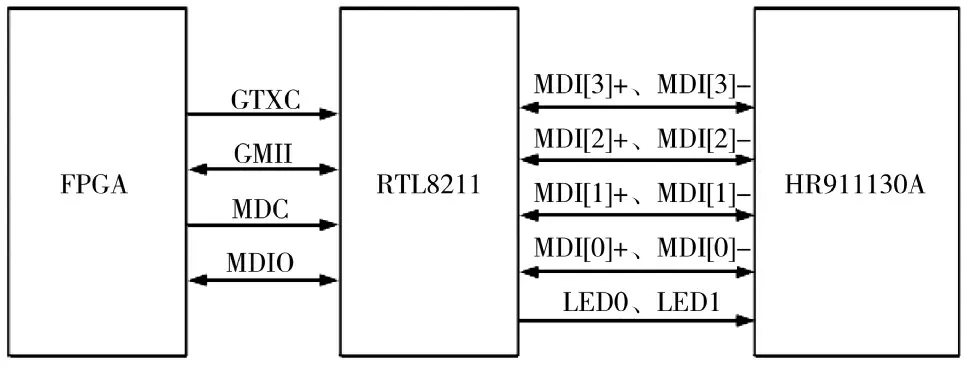

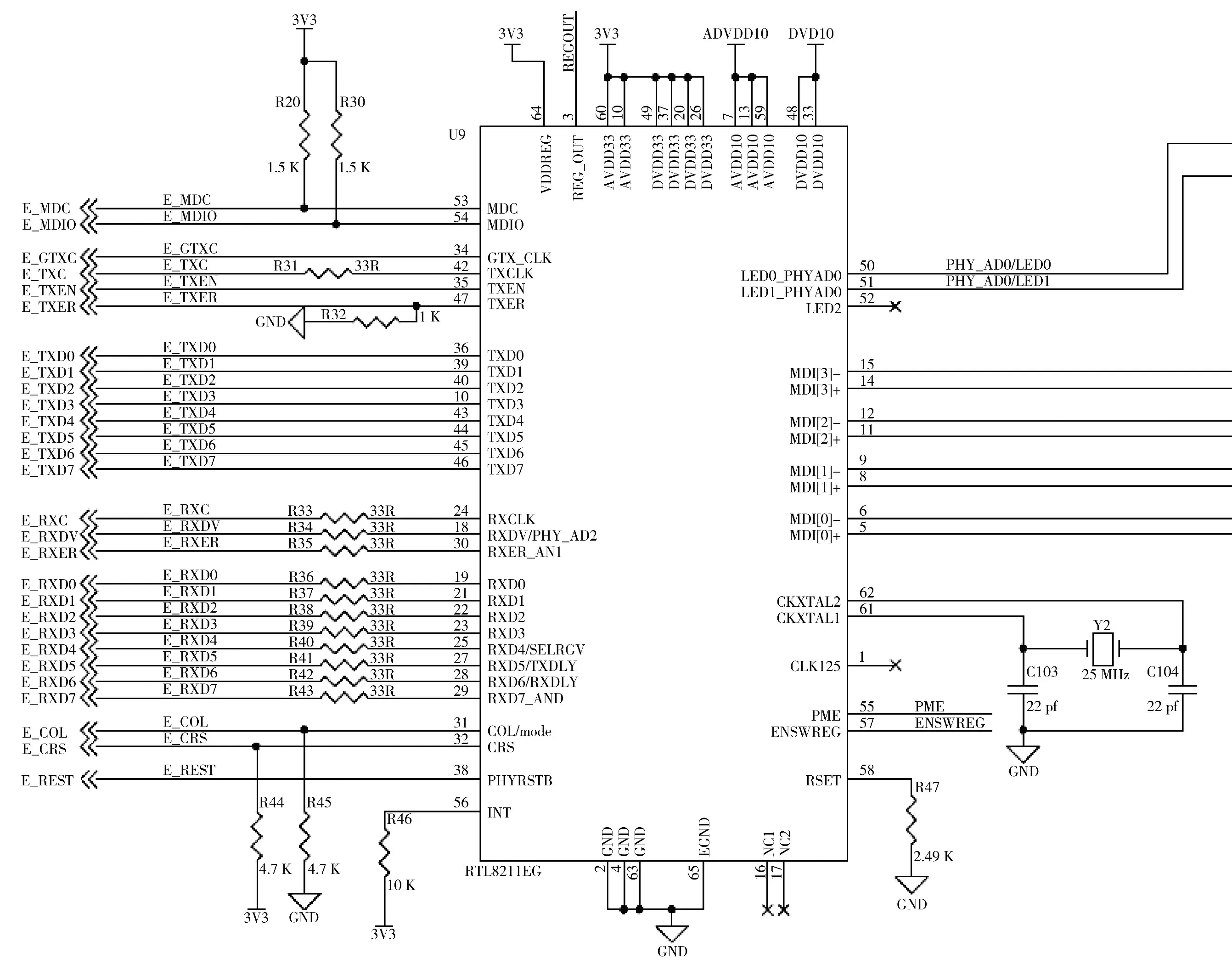

以太网模块由多址接入信道(multiple access channel,MAC)控制器、物理层(physical layer,PHY)芯片、RJ45 网口(网线连接口)组成,本设计中用FPGA 实现MAC 控制器,选用Realtek 公司生产的一款电平兼容性较好的RTL8211 千兆以太网作为PHY(物理层)芯片。它兼容目前市面常见的千兆媒体独立接口(gigabit medium independent interface,GMII)等接口,千兆以太网接口电路设计如图4 所示。

图4 FPGA 与SRAM 连接示意图

FAPA 通过GMII 接口与RTL8211 取得通信,配置为全双工千兆以太网工作模式,外接25 M 晶振,芯片IO 管脚为3.3 V,芯片本身的REG_OUT 管脚仅为芯片内核的1.05 V 进行供电,不需要外部提供基准电压,连接图如下页图5 所示。

图5 千兆以太网电路连接图

3.4 供电模块

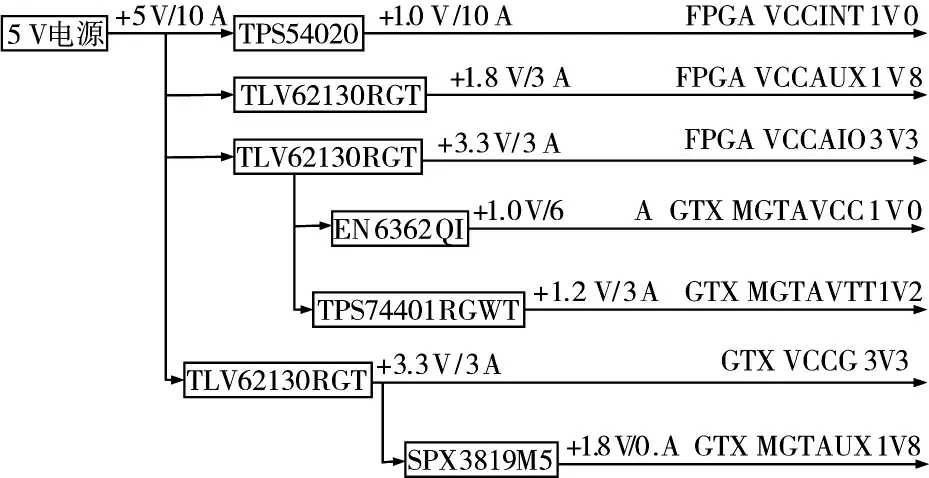

由于系统输入最大电压为5 V/10 A,因此,用5 V 外接电源进行供电。+5 V 输入电源通过压降转换芯片TPS54020 产生+1.0 V 的FPGA 核心电源,TPS54020 输出电流达10 A,满足FPGA 的核心电压的电流需求。另外+5 V 通过3 路电源芯片TLV621 30RGT 分别产生+3.3 V、+1.8 V、+3.3 V 3 路电源。其中,第1 路+3.3 V 可直接供FPGA 使用,其电压也通过芯片EN6362QI 和TPS74401RG WT 分别产生GTX 所需的+1.0 V/6 A 电源和1.2 V/3 A 电源;第2路+1.8 V 供FPGA 使用;第3 路+3.3 V 电源目的是供GTX 使用,这路+3.3 V 再通过芯片SPX3819M5后产生+1.8 V 电源供GTX 使用。本链路共用到1个TPS54020 芯片和3 片TLV62130RGT 来分别产生1.0 V、1.8 V、3.3 V 3 种电压,电源供电规则如图6 所示。

图6 电源供电规则

4 系统逻辑设计

4.1 光纤通信接口模块

光通信模块控制协议可以将光信息转化为数据流,按层规划可以分为物理层、数据链路层和用户逻辑层,如图7 所示。其中,物理层根据性能还可划分为物理介质相关子层(physical media related sublayer,PMD)、物理介质连接子层(physical medium connection sublayer,PMA)、物理编码子层(physical coding sublayer,PCS)3 层。

图7 光通信模块层规划

用户逻辑层:用户逻辑层是针对设计者来说的,是用户发送数据和接收数据的重要接口,收发接口的数据方向如下页表1 所示。

表1 收发接口数据方向

帧数据的发送需按照各接口信号的时序关系完成,数据发送时序如图8 所示。TX_D[[0:(wn-1)]指发送数据,TX_SOF_N 和TX_EOF_N 分别是帧起始信号和帧结束信号;TX_REM 是指示数据帧最后一个TX_D 内有效的Byte 数;TX_SRC_RDY_N为发送准备信号,当它为0 时,说明发送端已准备好数据,否则,数据无效;TX_DST_RDY_N 是接收准备信号,若该信号在时钟上升沿变低,则说明接收端准备接收数据。

图8 数据发送时序图

4.2 总线网络通信协议设计

网络中所有设备在组网之前都被设置了固定的设备地址,主节点路由在上电发起设备枚举命令,轮询其下子设备地址信息,并将地址信息记录在路由表中,本级路由表的信息汇总完毕会继续向上级路由设备汇总,最终在顶层路由设备中形成网络中完整的路由表信息。

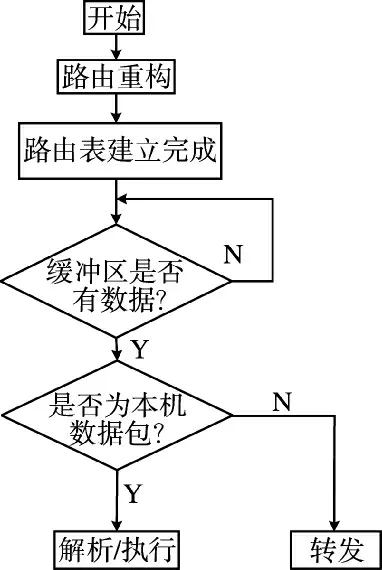

数据寻址模块轮询各端口缓存区中是否有数据,在收到数据后检索到数据包中目的地址,查询路由表中该目的地址对应的接口是否和本机一致,从而判断是否为本机的数据包,若一致,则执行相应的功能,发送数据时流程与接收数据相同,判断数据包与本机一致后,对数据包进行解析后发出,若判断不是本机,则转发到相应目的地址。这种寻址模式可以做到数据若从总线网络中任意设备输入,通过设备枚举和寻址,数据可以快速被指定设备接收,数据寻址流程如图9 所示。

图9 数据寻址流程图

4.3 以太网模块的逻辑设计

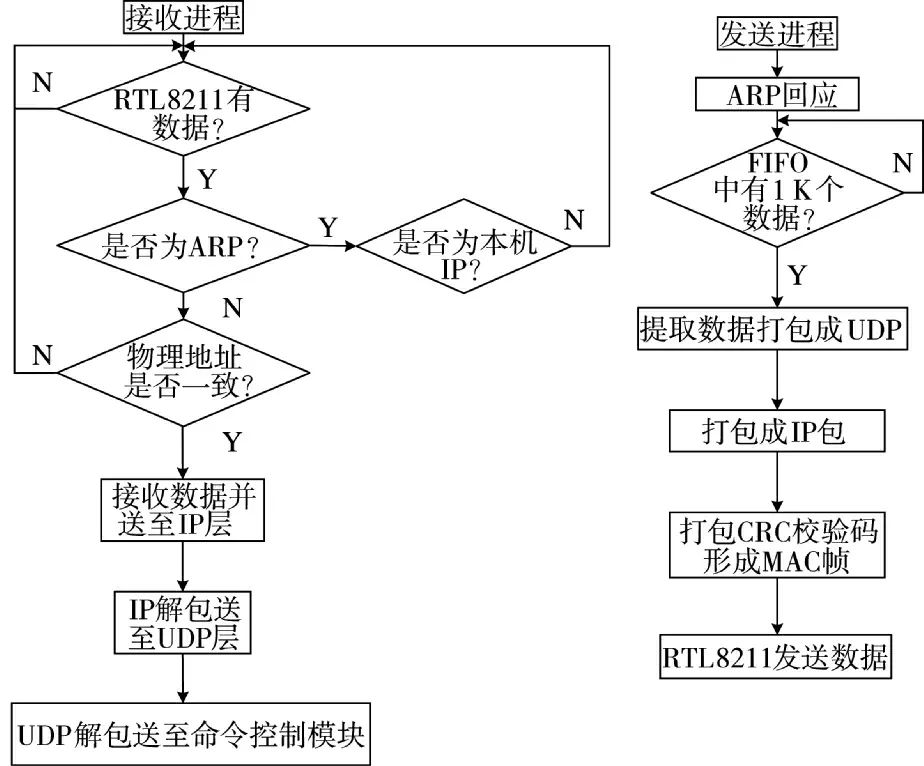

以太网模块程序设计实现分为发送和接收两个进程,程序设计框图如图10 所示。发送进程首先对地址解析协议(address resolution protocol,ARP)请求进行回复,判断FIFO 中是否有1 K 数据,满足1 K 数据量即可发送,从ARP 协议获取多址接入信道(multiple access channel,MAC)地址后,再从FIFO中读取数据打包为MAC 帧(1 024 Byte/次);接着打包成以太网帧,打包顺序按照以太网模型的传输层、网络层、物理层的顺序逐层打包,同时识别数据中是否发送了7 Byte 的引导码、1 Byte 帧前界定符,以上引导符都识别到以后开始发送以太网帧,最后添加4 Byte 循环冗余校验(cyclic redundancy check,CRC),通过GMII 接口发给RTL82110,发送过程完毕。

图10 以太网模块程序设计框图

以上涉及到的传输层、网络层、物理层逐层打包和对指定MAC 地址进行接收发送等操作需要设计以太网数据软件包,实现过程如下:MAC,IP,用户数据报协议(user datagram protocol,UDP)这3个层的数据需要分别存放,所以在ISE 14.7 中分别声明了3 个变量mac_addr,ip_header,udp_header 对应于这3 个层存放数据,软件中同时设置了本机MAC 地址(192.168.151.200)、本机IP 地址(192.168.151.200)和目的IP 地址(192.168.151.201),在每次通信建立前利用ARP 协议获取目的MAC 地址并绑定,将数据写入mac_addr 信号中,缺省值设定为全快速跳频(fast frequency-hopping,FFH)。

5 实验结果

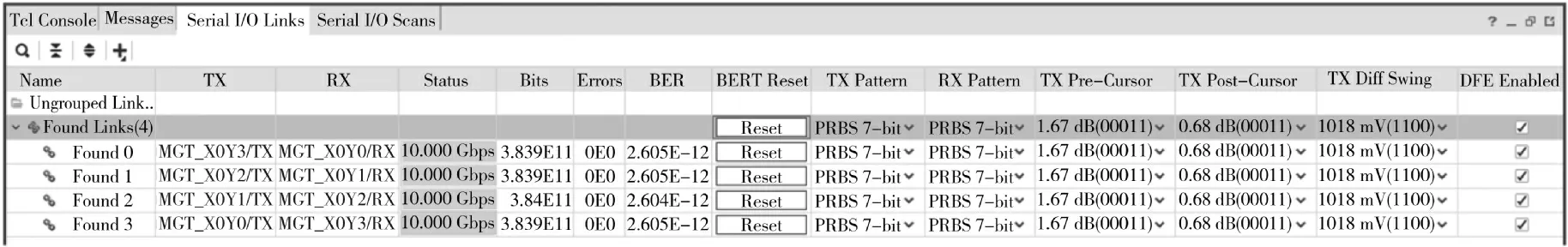

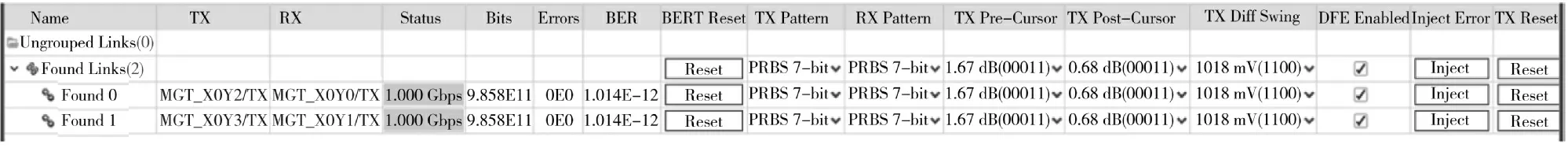

考虑到总线网络中各子设备之间的连接形式有两种,分别是路由与终端相连,路由和路由相连,所以在设计完成后需要回环测试的通道分别是路由-终端之间、路由-路由之间,并且路由- 路由之间的通道传输效果和路由本身连接通道的传输效果相同。终端的两个通道之间的数据传输信息统计含义与此相同,路由和终端高速数据传输链路验证如下页图11 和图12 所示,可以看出传输速度为10 Gb/s,误码率1.014×10。由此可知,路由4 通道和终2 通道的速度均可达到10 Gb/s。

图11 路由高速数据传输通道验证

图12 终端高速数据传输通道验证

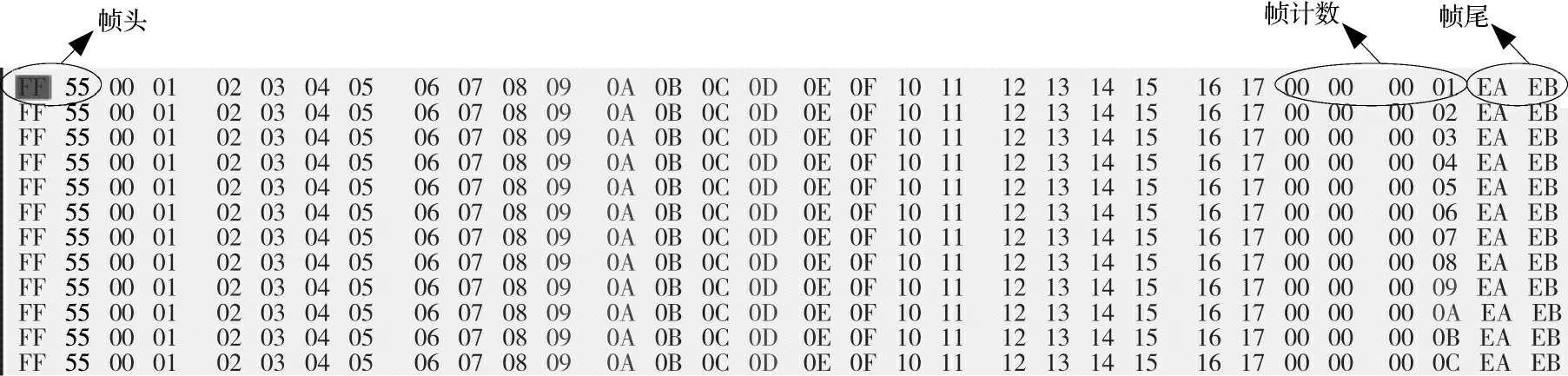

为验证链路整体效果,测试平台搭建如图13 所示,使用5 V 开关电源进行供电,终端测试台通过网线连接计算机,路由和终端之间通过光缆进行连接,为保证本链路中路由与上位机数据通信的完整性,这里举例在路由中设计信号源发送一组数据8 位递增数,包含帧头帧尾和32 位的帧计数。通过光电转换模块以及光纤光缆传到终端,终端测试台将路由信号源发出的数据接收,转发到上位机存储数据,结束后数据采集软件将数据文件存入保存路径,接着用Hex编辑器打开数据采集软件存储的文件,图14 为接收到的数据,是包含帧头帧尾和帧计数的8 位递增数,与发送一致,数据也没有丢失。

图13 链路整体测试平台示意图

图14 上位机接收数据

6 实验结论

数据在所搭建的测试平台上多次地发送与接收均一致,说明高速光纤通信链路发送数据正常,链路畅通,验证高速光纤通信链路的回传过程是以上过程的逆过程,回传实验均正常,链路畅通。实验和仿真结果表明,网络中路由与终端之间及路由与路由之间链路传输速度为10 Gb/s,能够快速进行数据传输,并且可以将数据回传至上位机进行观察分析,误码率可达到1.014×10,满足任务要求。