基于FPGA的多路实时视频处理系统设计

严飞丁兆东刘银萍陈伟刘佳*

基于FPGA的多路实时视频处理系统设计

严飞1,2,丁兆东1,刘银萍1,3,陈伟1,刘佳1,2*

(1.南京信息工程大学 自动化学院,江苏 南京 210044;2.江苏省大气环境与装备技术协同创新中心,江苏 南京 210044;3.南京信息工程大学 大气物理学院,江苏 南京 210044)

基于FPGA平台,采用双线性插值缩放算法,实现了对多路实时视频任意比例的缩放。进行了DDR3的读写逻辑设计,采用乒乓操作以及多通道读写仲裁模块,实现了实时的图像缓存。采用Alpha叠加融合算法,实现了对多路视频任意位置的漫游叠加,以及任意通道视频透明度的调节。实验结果表明,本次设计的多路实时视频处理系统,实现了最大分辨率为3 840×2 160、最低分辨率为100×100的缩放,能够灵活改变叠加位置的大小和位置,图像清晰、无闪屏、无错位情况的发生。

FPGA;双线性插值;视频缩放;图像漫游

1 引言

视频显示技术发展到21世纪,同时显示多个视频的需求仍然存在,人们需要从单个显示器获得更多、更复杂的信息。因此,人们对图像处理的效率、实时性、功耗以及处理设备的体积也有了更严格的要求[1]。当前常用的嵌入式图像处理平台有ARM(Advanced RISC Machine)、数字信号处理(Digital Signal Processing,DSP)、专用集成电路(Application Specific Integrated Circuit,ASIC)以及现场可编程逻辑门阵列(FPGA)等。ARM平台有较不错的处理能力,配合一系列的开源处理算法,开发比较方便,因此这种方式能够满足部分图像应用场景的需求。但是随着高速处理视频图像需求的增加以及算法的日趋复杂,单靠微处理器已经无法满足实时性处理的要求。DSP是一种专门用于实现快速数字信号处理算法的微处理器,其中有一些固定的运算模块,使得其信号处理的速度优于微处理器,适合操作性强和运算量大的场合,但是由于DSP采用的是串行指令系统,使用起来有诸多限制。ASIC是为专门应用场景下所设计的芯片,虽然在特定使用场景下功耗低、性能强,但是在其他使用场景时需要重新设计,适用性较差。FPGA由于可编程以及并行运算的特性,相比于ASIC虽然功耗较高,但其可无限重复编程[2-5],因此,采用FPGA作为核心处理器能够满足高分辨率、高帧率等性能需求。

针对传统的实时视频处理系统大多存在分辨率低、控制不灵活、视频处理算法单一、实时性差等问题[6-8],本文设计了一款具有4通道高速并行处理能力的多路视频实时处理系统,采用高清多媒体接口(High Definition Multimedia Interface,HDMI)的视频作为视频源,经过FPGA处理,最终实现将4路视频任意比例缩放、漫游、叠加融合成一路视频显示。这使得用户可以实时观察真实直观、细节丰富的多路超高清影像数据,也符合市场需求。

2 系统设计

本设计发送卡和接收卡采用的FPGA芯片是由Xilinx生产的XC7K325系列的XC7K325-TFFG900,主要用来接收图像、处理图像以及驱动显示器实时输出显示。

多路实时视频处理系统采用一块视频发送卡对4路HDMI视频数据进行接收。系统上电后,首先将接收到的视频数据进行预处理,再根据串口接收到用户的缩放参数、图像裁剪参数,将处理后的视频数据根据用户命令参数进行实时缩放处理,然后将缩放后的视频数据根据用户需要的视频图像大小进行裁剪,通过读写仲裁模块按照一定的顺序存储到动态内存DDR3中,最后将读出的每个通道的数据通过光纤发送模块发送出去。视频发送卡的内部逻辑框图如图1所示。

图1 视频发送卡FPGA内部逻辑框图

接收卡通过4路光模块接口接收到视频数据,对数据进行上采样处理,再根据串口接收到用户的旋转角度参数,对接收到的4个通道数据进行旋转处理,然后通过多通道读写仲裁模块按照一定的顺序存入到动态内存DDR3中,按照用户选择通道的数据从DDR3读出对应通道的有效数据,并对多通道视频进行叠加融合,最后进行色彩空间转换,并通过HDMI接口将融合后的一路数据在4K显示器上显示。视频接收卡的内部逻辑如图2所示。

图2 视频接收卡FPGA内部逻辑框图

3 双线性插值缩放算法实现

常规视频缩放算法有最邻近插值算法、双线性插值算法、双三次插值缩放算法。由MATLAB仿真效果可知[9],最临近插值算法效果差;双线性插值法计算量和效果居于两者之间;双三次插值缩放算法效果最好、画面细腻但计算量大;在既要保证效果的同时又要考虑视频处理的实时性以及算法的复杂情况下,本次设计选用双线性插值算法进行基于FPGA的缩放逻辑设计[10-13]。

3.1 双线性插值缩放算法逻辑设计

双线性插值缩放算法的逻辑设计框图如图3所示。

图3 双线性插值算法逻辑设计图

由于双线性插值采用周围4个像素点确定目标像素点,因此至少缓存两行以上的数据才能根据周围像素点值计算目标像素点的值[14-16]。本设计可以采用两个RAM即可对目标像素点周围4个像素点进行计算,但是为了提高处理速度,本设计采用4个双口RAM进行数据读写的乒乓操作。且为防止处理效率低,第一次计算时必须保证4个RAM存满才开始进行插值计算。

3.2 双线性插值缩放计算

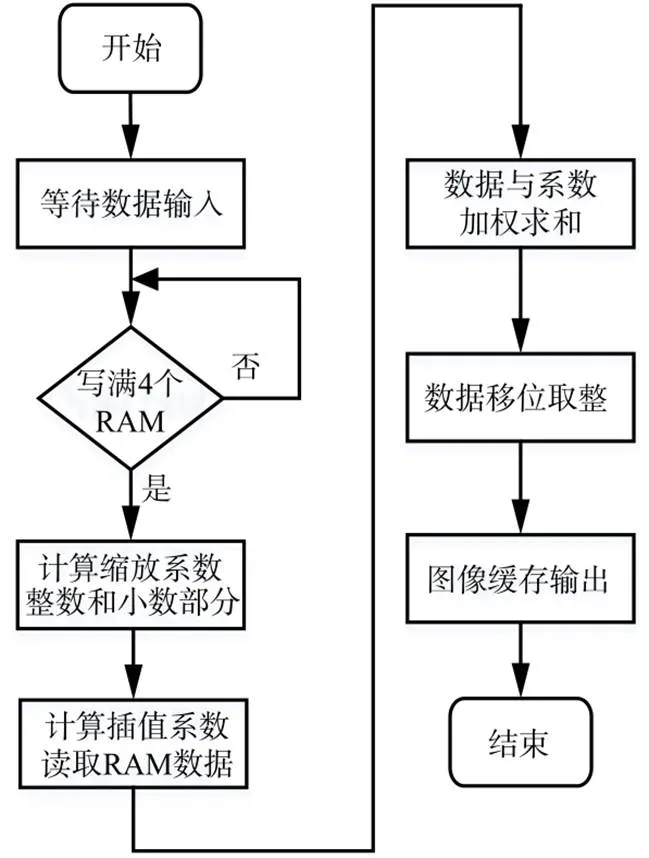

双线性插值缩放计算流程如图4所示。首先等待数据输入,当有效数据来临时,将其存入RAM。本设计设定存满4行视频数据以后,系统才开始进行计算。最后将数据取整输出。

图4 实时视频缩放流程图

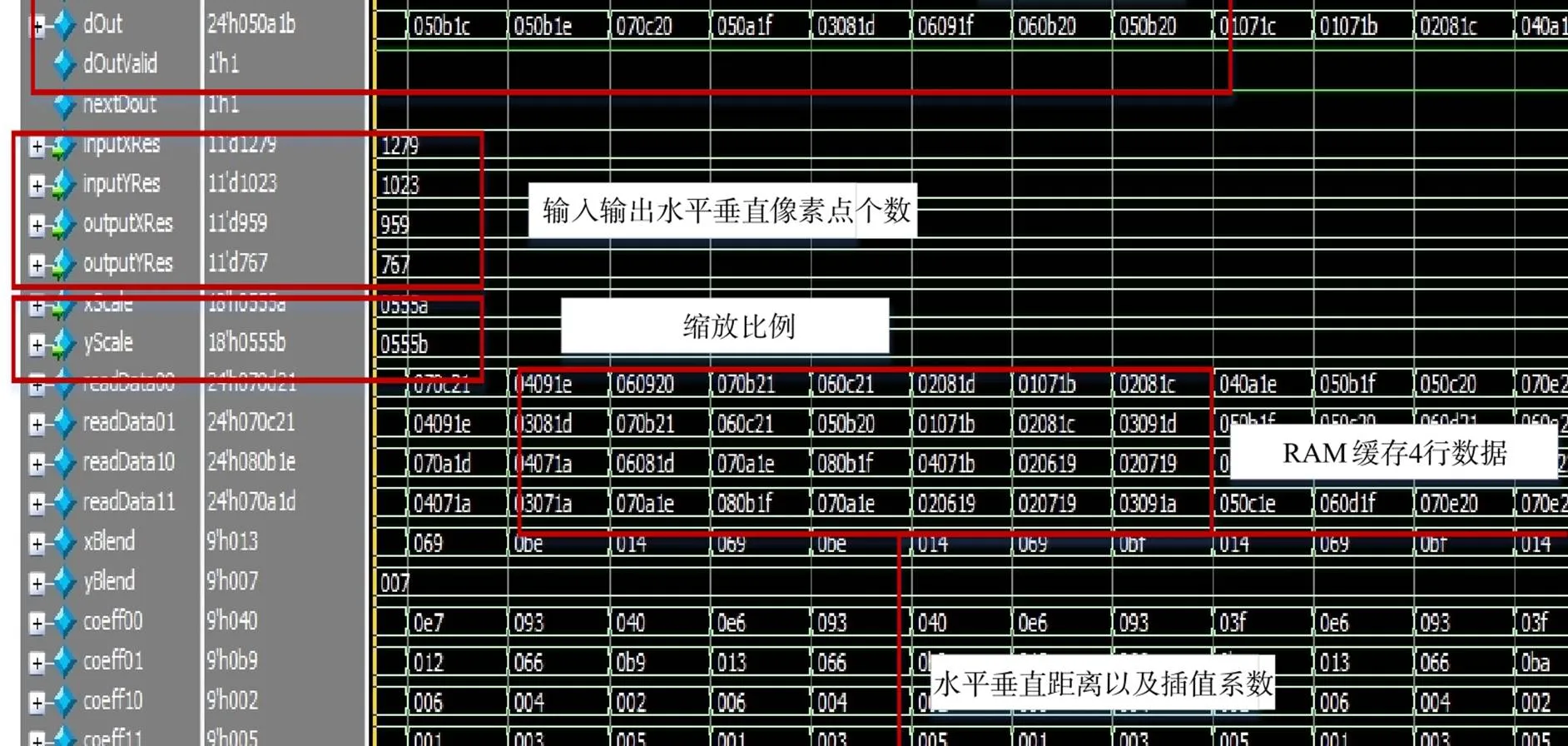

缩放算法的仿真波形如图5所示。仿真波形是以1 280×1 024为输入,缩小到960×768,根据输入输出水平像素点个数可以求出缩放比例、插值系数以及插值点与原图像中像素点的水平距离和垂直距离。通过使用4个RAM实现对两行数据的缓存,实现对插值像素点周围4个像素点的缓存输出。其中dOut为输出数据,coeff为求得的插值系数,xScale、yScale为水平和垂直方向因子,inputXres、inputYres表示输入水平、垂直方向像素点个数。outputXres、outputYres为输出水平、垂直方向的像素点个数。

图5 缩放算法的仿真波形

3.3 双线性插值算法验证与分析

在保证以上测试模块均正常工作情况下,进一步对缩放模块进行验证。实际板上验证时,通过HDMI接口输入的1 080P视频数据作为视频源,ILA在线逻辑分析仪的波形窗口的显示如图6所示。在传输有效像素信号时,行同步(hs)信号、帧同步(vs)信号、有效信号(de)均符合图像传输时序定义。从在线逻辑仿真图中可以看出,在有效信号(de)保持为高电平时,从起始点1 130到终止点1 230,每行数据仅输出100个有效数据其余数据均为0,说明实现了100×100缩放设计,接下来进一步进行板上验证。

图6 100×100缩放在线逻辑分析仪的波形图

如图7所示,实际板上验证时采用视频流为1 080P的HDMI输入作为视频源,经过缩放、缓存、同步等操作,最后再通过HDMI接口输出至显示器上显示。图7(a)、(b)分别为3 840×2 160缩放效果图以及100×100缩放效果图。实验结果表明,本系统双线性插值图像缩放能够支持图像进行任意比例的缩放,但是在实际缩放效果观察过程中可以发现,虽然理论上可以支持最低缩放到1×1分辨率,但是实际上板100×100效果已经出现了比较严重的失真,缩放模块满足本次设计要求。

图7 双线性插值在FPGA上实现效果图

4 实时图像缓存实现

4.1 DDR读写逻辑设计

本次设计视频发送卡和接收卡的核心处理器均采用Xilinx公司的7系列FPGA,采用4片4G的镁光DDR3作为内存。由于均支持Xilinx官方的DDR3控制器MIG IP核,本设计直接通过调用MIG IP核控制DDR3,降低了开发难度[17-22]。

为了简化操作,重新编写了面向用户的读写接口。读写操作如图8所示。在初始状态下,首先判断是否有读写请求,当两个信号同时来临时,优先进行写操作,防止读出数据为空的情况出现。当写请求信号为1时,首先判断此时写命令app_cmd是否为0和DDR3返回响应信号是否为高,只有在两种条件同时满足情况下,才开始向DDR3中写入数据。其次判断DDR3写完成信号是否拉高,若拉高则写结束并返回初始状态,反之则继续进行写操作。读操作处理流程也是如此。

图8 用户接口突发读写流程图

针对DDR3读写测试,用户接口读写控制的逻辑仿真波形如图9所示。其中app_wdf_rdy和app_wdf_wren同时为高,并且app_cmd为000时,开始写入数据进DDR3。当app_cmd为001则开始从DDR3读出数据。当初始化信号init_calib_complete拉高以后,在app_wdf_rdy、app_wdf_wren同时为高并且app_cmd为000时执行写操作。本次测试的突发长度设置为32,测试数据由计数器产生为0~127。在DDR3初始化完成以后,首先向DDR3中写入测试数据。从仿真图中可以看出,每次向DDR3中突发写入32个数据,实现了对DDR3的突发写操作。

图9 用户接口读写控制

当控制器处于读状态,读命令信号app_cmd为001并且读数据有效信号app_rd_data_valid为高时,开始从DDR3中读出数据。由于读出DDR3数据比写入DDR3的数据有一定的延迟,因此在实际观察时要找到第一次读出数位置,观察是否错位。DDR3第一次读出数据为0~31,第二次读出数据为32~63,读突发长度为32。通过对比读写数据可以看出,两者保持一致,且读写突发长度满足设定要求。且错误信号error_num一直保持为0,说明DDR3数据读写正确。

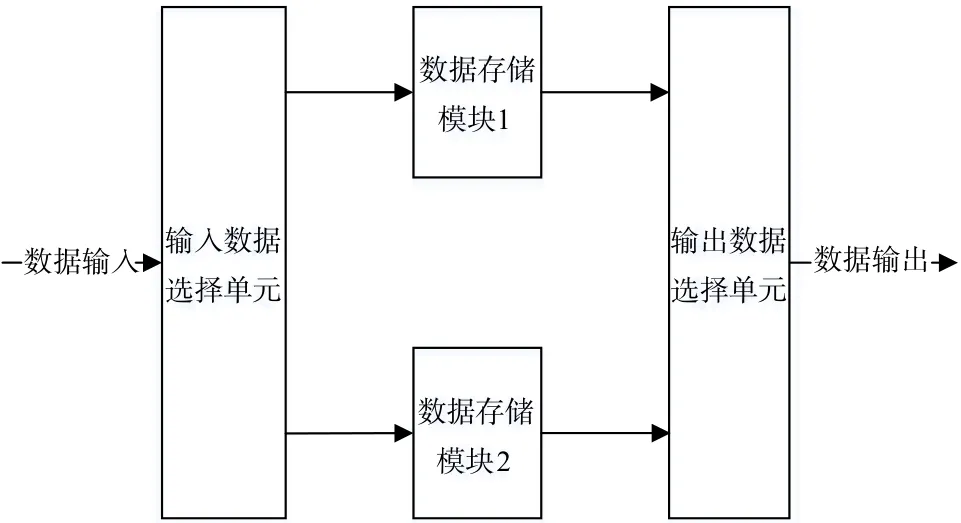

4.2 读写模块乒乓操作实现

在本次设计中数据存储模块主要是指将DDR3区域划分两个区域,乒乓操作如图10所示。对多路实时视频图像数据进行处理具有数据量大的特点,乒乓操作可以有效地控制数据流的快速传输,提高数据处理速度,缩短处理时间,提高图像显示的实时性。其实现的基础是数据的缓存,采用数据选择器将数据流分成两部分,两个数据缓存器交替地进行数据输入处理,这样既保证了数据的完整性,又有效地提高了数据处理速度,保证数据不出现混乱。

图10 乒乓操作示意图

系统处于写状态时,写数据选择单元会根据场同步信号找到一帧图像数据的开始点,然后缓存进数据存储模块1。当下一帧数据来到时则缓存进数据存储模块2,如此反复进行存储模块切换。系统处于读状态时,读数据选择单元会根据输出视频时序的场同步信号进行存储模块切换并读出数据。

4.3 多通道读写仲裁模块逻辑设计

本次逻辑设计最大可支持7个通道仲裁。以三通道读写仲裁为例,其处理流程如图11所示。当数据开始输入时,首先判断当前通道条件S:读请求和读突发长度是否都不为0,判断是则进行当前通道数据处理并输出当前数据,反之跳转到下一个通道判断条件,对下一个通道数据进行处理,依次判断可实现多通道读写仲裁,在多通道读写仲裁模块逻辑设计同样如此。

图11 多通道仲裁处理流程图

5 视频图像叠加融合

视频图像叠加融合是将两路视频图像信号中的一路作为背景,另一路为前景,在背景视频图中融入前景图像,在同一终端上显示多通道叠加图像[23-26]。本次设计采用Alpha叠加融合算法,视频图像叠加融合模块采用两路视频源叠加进行测试,为了方便观察,首先将背景的值设置为一个固定值24’h108080。其中背景视频大小为1 920×1 080,前景视频大小为100×100。Alpha融合叠加算法的ILA在线逻辑分析仪波形窗口如图12所示。当前景视频处于有效数据范围内并且Alpha为16’hff时,全部显示为前景,输出融合视频数据等于前景视频的有效数据;当前景视频处于无效数据范围内并且Alpha为16’h00时,输出融合视频数据等于背景视频有效数据24’h108080。

图12 Alpha融合叠加在线逻辑分析仪的波形

Alpha融合叠加在FPGA上实现实际效果图如图13所示。其中图13(a)为一路PC电脑桌面作为视频源输入,并将输入的画面进行四通道复制。首先将输入的1 080P视频数据缩放至960×540大小,最后将4个通道数据进行叠加融合输出。实际上板验证的叠加效果图a~d的Alpha值分别为16’h00,16’h40,16’h80,16’hff,其画面对应的透明度也依次降低。图13(b)将两路输入的1 080P视频缩放为两路960×480大小的视频,且将背景画面的Alpha值设置为16’hff,前景画面的Alpha值设置为16’h80,960×480的前景图叠加在960×480背景图上,其余区域均为黑色。根据叠加融合输出效果图可以看出,图像清晰,无闪屏、无错位情况发生。另外可以通过串口设置参数,灵活改变叠加位置的大小和位置,满足系统的设计需求。

(a) 4画面融合叠加效果图(a) Four-picture fusion superimposed effect picture (b) 2画面融合叠加效果图(b) Two-picture fusion superimposed effect picture

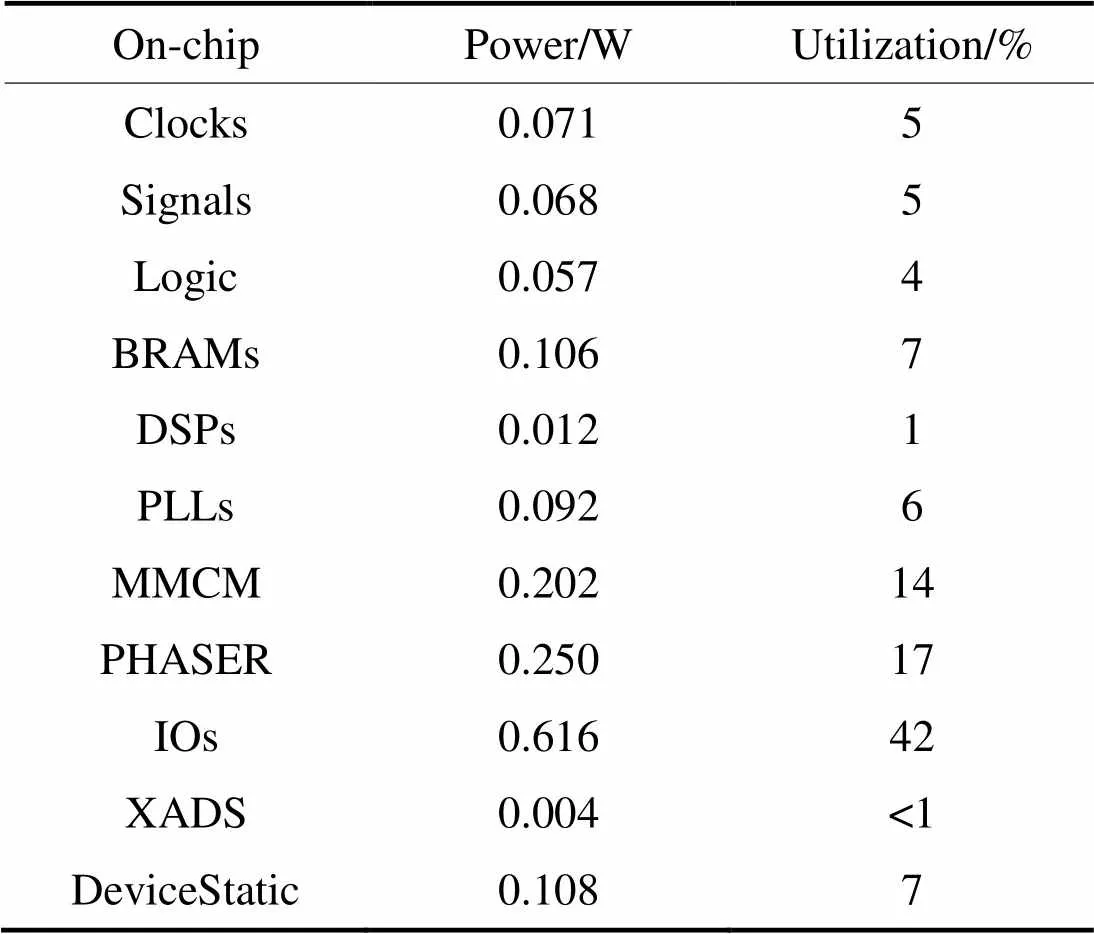

6 实验测试和功耗分析

片上总消耗主要由动态功耗和静态功耗组成。从表1可以计算出,视频发送卡的片上总功耗为1.479 W,其中动态功耗占93%。从表2可以计算出,视频发送卡的片上总功耗为3.520 W,其中动态功耗占95%。系统在设计过程中对于功耗的分析是十分必要的,若功耗过高则会造成芯片发热甚至损坏,其次会导致FPGA内部时序的不稳定,导致冒险与竞争的出现。为了进一步降低功耗以及提高系统的稳定性可以从以下两个方面进行优化。

表1视频发送卡的片上功耗情况

Tab.1 On-chip power consumption of the video sending card

表2视频接收卡的片上功耗情况

Tab.2 On-chip power consumption of the video receiving card

(1)资源优化:以存储器为例,在设置双端口RAM时设置成NO CHANGE模式以及设置时钟使能的情况下,可以实现对存储器功耗的降低。

(2)算法优化:首先要设计最优的算法,使资源占用达到最少。比如流水线和状态机结构,需要根据实际情况进行选择,以达到面积和速度的平衡。

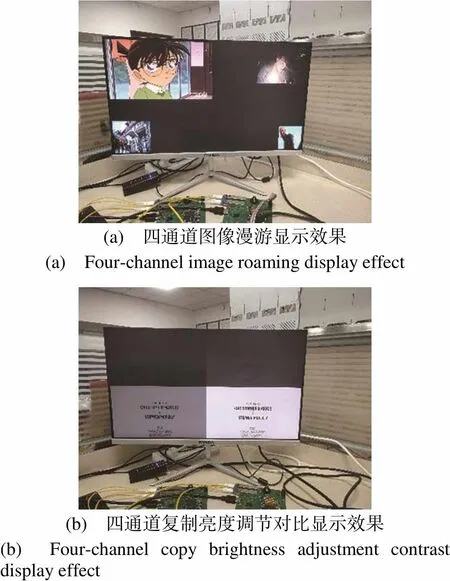

本次设计可以实现4K视频的任意比例缩放、透明度调节以及4路视频任意位置漫游、叠加与融合。首先进行多通道缩放、漫游、旋转以及叠加融合测试,其实际板上验证效果如图14所示。为了方便观察,本次选用比较有代表性的结果图进行展示。

(a) 四通道图像漫游显示效果(a) Four-channel image roaming display effect (b) 四通道复制亮度调节对比显示效果(b) Four-channel copy brightness adjustment contrast display effect

测试多路视频输入采用笔记本作为视频源,其分辨率为1 920×1 080@60 Hz;由于笔记本输出分辨率的限制,单路视频输入测试时采用台式电脑作为视频源,其分辨率为3 840×2 160@30 Hz,最后均通过4K分辨率显示器显示。

图14(a)将四通道输入视频缩放至不同大小,最后将4路视频在没有叠加的情况下进行漫游输出。图14(b)将单通道分辨率为3 840×2 160@30 Hz的视频源,复制为4路视频进行输入。将4路视频缩放至960×540大小以后,分别设置Alpha值为16’h00,16’h40,16’h80,16’hff,实现对画面透明度由高到低的调节。由实验结果可知,本系统实现了高清4K视频的任意比例缩放、多路高清视频的任意位置漫游、任意位置叠加融合。在实际调试过程中,由于时钟速率不匹配,显示效果图可能会出现未知显示效果,因此需要对系统进行时序约束,防止竞争冒险的出现。

7 结论

本文基于FPGA开发平台,实现了一种多路实时视频处理系统。采用Vivado 2019.1作为软件开发平台完成了双线性插值缩放算法设计,实现了最大分辨率为3 840×2 160、最低分辨率为100×100的缩放,满足了用户特殊分辨率的需求。同时可以将多路视频数据进行任意位置漫游以及叠加融合,满足了人们需要从单个显示器获得更多、更复杂的信息的需求。

本系统目前仅支持单一的HDMI输入输出接口,为满足用户的各种需求,应当增加接口种类,并合理增加一些拓展接口。目前本系统在硬件上仅支持4路视频源输入,应该在硬件上设计增加更多的视频输入接口数量,并对硬件进行信号完整性验证。为了满足用户多样化需求可以在现有的基础上增加多样视频算法,并优化系统的整体延时。

[1] BAILEY D G.基于FPGA的嵌入式图像处理系统设计[M].原魁,何文浩,肖晗,译.北京:电子工业出版社,2013.

BAILEY D G.[M]. YUAN K, HE W H, XIAO H, trans. Beijing: Publishing House of Electronics Industry, 2013. (in Chinese)

[2] 金永明,蒋韬.DP与DVI接口在4K显示器上叠加显示的电路设计[J].山东工业技术,2016(14):144-146.

JIN Y M, JIANG T. Circuit design of DP and DVI interface superimposed display on 4K display[J]., 2016(14): 144-146. (in Chinese)

[3] RADICKE S, HAHN J U, WANG Q,. A parallel HEVC intra prediction algorithm for heterogeneous CPU+GPU platforms[J]., 2016, 62(1): 103-119.

[4] KASSIM A A, CHUA K S, FONG F K,. DSP-based system for real-time video communications[J]., 1999, 10(1): 47-53.

[5] KIM K, KOH J S, SUH K B,. An efficient frame memory interface of MPEG-2 video encoder ASIC chip[C]//1999. Los Angeles: IEEE, 1999: 58-59.

[6] 严飞,宋振声,刘银萍,等.4K裸眼立体显示系统设计[J].液晶与显示,2019,34(9):862-870.

YAN F, SONG Z S, LIU Y P,. Design of 4K bare-eye stereoscopic display system[J]., 2019, 34(9): 862-870. (in Chinese)

[7] 易子川,林跃,王利.基于FPGA的多路视频实时处理系统[J].华南师范大学学报(自然科学版),2017,49(1):51-55.

YI Z C, LIN Y, WANG L. Multi-channel real-time video processing system based on FPGA[J].(), 2017, 49(1): 51-55. (in Chinese)

[8] 郭昕.基于FPGA的多路超高清视频实时处理系统设计[D].上海:华东师范大学,2018.

GUO X. FPGA-based multi-channel ultra-high definition video real-time processing system design[D]. Shanghai: East China Normal University, 2018. (in Chinese)

[9] 丁雪晶.实现图像缩放功能的Matlab插值算法研究与比较[J].湖北大学学报(自然科学版),2018,40(4):396-400,406.

DING X J. Research and comparison of Matlab interpolation algorithm for image scaling function[J].(), 2018, 40(4): 396-400, 406. (in Chinese)

[10] 李向军.数字视频系统接口应用[J].电视技术,2016,40(10):37-40.

LI X J. Application of interfaces in digital video system[J]., 2016, 40(10): 37-40. (in Chinese)

[11] 严飞,陆宝毅,刘银萍,等.实时视频流缩放系统设计[J].液晶与显示,2019,34(11):1124-1130.

YAN F, LU B Y, LIU Y P,. Design of real-time video stream scaling system[J]., 2019, 34(11): 1124-1130. (in Chinese)

[12] SINGH R, RADPOUR F, NARAYAN J,.-rapid isiheial pocessing of thin epitaxial dieleciric films on silicon and compound semi semiconductors[J]., 1986, 75(1): 681-690.

[13] YUSIANTO R, MARIMIN, SUPRIHATIN,. Green logistics approach in bioethanol conversion from potato starch in central Java[C]//:. Jeju Island: IOP, 2019: 012100.

[14] 张梁,王景存,梅镖.视频缩放在FPGA中的应用和实现[J].电子技术应用,2016,42(6):34-37.

ZHANG L, WANG J C, MEI B. Application and implementation of video scaling algorithm based on FPGA[J]., 2016, 42(6): 34-37. (in Chinese)

[15] 岳鑫,肖晨.基于奇异值分解和双三次插值的图像缩放算法改进[J].西安邮电大学学报,2018,23(4):72-77.

YUE X, XIAO C. Improvement of image scaling algorithm based on singular value decomposition and bicubic interpolation[J]., 2018, 23(4): 72-77. (in Chinese)

[16] 于亚龙,穆远彪.插值算法的研究[J].现代计算机(专业版),2014(5):32-35.

YU Y L, MU Y B. Research on interpolation algorithm[J].(), 2014(5): 32-35. (in Chinese)

[17] 潘亮,穆仕博,何广亮,等.FPGA的SDR/DDR3 SDRAM控制器设计[J].单片机与嵌入式系统应用,2020,20(1):52-55.

PAN L, MU S B, HE G L,. Design of SDR/DDR3 SDRAM controllers based on FPGA[J]., 2020, 20(1): 52-55. (in Chinese)

[18] VERSEN M, ERNST W. Row hammer avoidance analysis of DDR3 SDRAM[J]., 2020, 114: 113744.

[19] 杨朋飞,聂亮.基于FPGA和DDR3的图像采集系统设计及实现[J].自动化与仪表,2019,34(9):37-40,51.

YANG P F, NIE L. Design and implementation of image acquisition system based on FPGA and DDR3[J]., 2019, 34(9): 37-40, 51. (in Chinese)

[20] 齐佳硕,王洪岩.基于FPGA的SDRAM接口设计及实现[J].电子测量技术,2018,41(19):141-144.

QI J S, WANG H Y. Design and implementation of the SDRAM interface based on the FPGA[J]., 2018, 41(19): 141-144. (in Chinese)

[21] 侯广琦,魏平,白廷柱.多通道嵌入式高速图像采集存储系统的研究[J].仪器仪表学报,2011,32(11):2543-2548.

HOU G Q, WEI P, BAI T Z. Study of multi-channel high-speed embedded image capture and storage system[J]., 2011, 32(11): 2543-2548. (in Chinese)

[22] 何雯,董威,苟辉.基于FPGA的高速视频采集系统的设计[J].国外电子测量技术,2016,35(5):83-87.

HE W, DONG W, GOU H. Design of high-speed video acquisition system based on FPGA[J]., 2016, 35(5): 83-87. (in Chinese)

[23] HALL A, LEGER D S, SINGH A,. The utility of computed tomography and diffusion-weighted magnetic resonance imaging fusion in cholesteatoma: illustration with a UK case series[J]., 2020, 134(2): 178-183.

[24] KURALT M, GAŠPERŠIČ R, FIDLER A. 3D computer-aided treatment planning in periodontology: a novel approach for evaluation and visualization of soft tissue thickness[J]., 2020, 32(5): 457-462.

[25] MORGAN H L, BUTLER E, RITCHIE S,. Modeling superimposed preeclampsia using Ang Ⅱ (Angiotensin Ⅱ) infusion in pregnant stroke-prone spontaneously hypertensive rats[J]., 2018, 72(1): 208-218.

[26] ULRICH R, SCHRÖTER H, LEUTHOLD H,. Automatic and controlled stimulus processing in conflict tasks: superimposed diffusion processes and delta functions[J]., 2015, 78: 148-174.

Design of multi-channel real-time video processing system based on FPGA

YAN Fei1,2,DING Zhao-dong1,LIU Yin-ping1,3,CHEN Wei1,LIU Jia1,2*

(1,,210044,;2(),210044,;3,,210044,)

Based on FPGA platform, the bilinear interpolation scaling algorithm is used to realize arbitrary scaling of multichannel real-time video. DDR3 read and write logic is designed. Using ping-pong operation and multi-channel read and write arbitration module, the real-time image cache is achieved. Alpha overlay fusion algorithm is used to realize roaming overlay at any position of multichannel video and adjust the video transparency of any channel. The experimental results show that the multi-channel real-time video processing system designed in this paper can realize the maximum resolution of 3 840×2 160 and the minimum resolution of 100×100, and can flexibly change the size and position of the stacking position. The image is clear, no flash screen and no dislocation.

FPGA; bilinear interpolation; video scaling; image roaming

TP274

A

10.37188/CJLCD.2022-0001

1007-2780(2022)07-0861-10

2022-01-01;

2022-02-17.

江苏省产业前瞻与关键核心技术重点项目(No.BE2020006-2);国家自然科学基金(No.61605083)

Supported by Jiangsu Provincial Key Research and Development Program (No.BE2020006-2);National Natural Science Foundation of China(No.61605083)

,E-mail:liujia@nuist.edu.cn

严飞(1983—),男,江苏南京人,博士,讲师,2013年于中国科学院大学获得博士学位,主要从事三维测量和信息显示技术方面的研究。E-mail:fyan@nuist.edu.cn

刘佳(1981—),女,江苏扬州人,博士,教授, 2008年于东南大学获得博士学位,主要从事虚拟现实/增强现实、人机交互及机器人技术方面的研究。E-mail:liujia@nuist.edu.cn