一种高精度紧凑型X波段6位数控移相器

陈 宁,梁 煜,张 为

(天津大学 微电子学院,天津 300072)

移相器是相控阵系统的重要组成部分,是收发组件中控制波束方向的关键模块,广泛应用于相控阵雷达、无线通讯等领域。其中,X波段相控阵雷达已成为国家导弹预警系统的重要组成部分,但由于其高实施成本、大重量、大体积和实施复杂性的特点,使该频段雷达技术更多应用于军事系统[1-2]。随着电子技术不断发展,X波段相控阵系统逐步拓展到民用领域,如气象雷达[3]等。近年来,移相器作为相控阵系统的核心功能模块不断发展,常见电路拓扑结构包括负载线型[4]、反射型[5]、矢量合成型[6-7]和网络切换型[8-19]。负载线和反射型移相器是基于传输线调整相位,因此在工作频率低于10 GHz时电路尺寸通常很大。矢量合成相移器普遍具有体积小和增益大的优点,但由于引入有源电路,导致其只能单向工作,并且有较大的功耗。

在数字移相器的设计中,高低通网络切换型移相器在插入损耗、移相精度等方面都具有较好的性能,在工作频段范围内相移相对平坦,且具有功耗低、宽带宽的优势,因此这种类型移相器逐渐得到广泛应用。切换型移相器结构上分为两类。其一是采用SPDT或DPDT作各移相单元的级联开关。该类移相器结构简单,但由于级联开关的插入可能会引起较大的插损,通常需要采用额外的级间损耗补偿放大器(Loss Compensation Amplifier,LCA)补偿损耗,如LIU[11]及GONG[14]等,一般会增加设计难度及电路复杂度。其二是采用MOSFET作开关嵌入移相单元电路中[8-10,12-13,15-18]。如张博等[16]基于0.25 μm GaAs pHEMT工艺设计的5位X波段移相器,小移相单元采用T型/π型的高(低)通/带通网络结构,90°和180°移相单元采用高/低通切换拓扑结构,移相RMS误差仅为1.6°,芯片尺寸为2.2 mm×0.7 mm。杨杰等[17]基于0.15 μm GaAs pHEMT工艺设计的X波段6位数控移相芯片,最大移相RMS误差为4°,最大插损为-10 dB,芯片面积为4 mm×1.8 mm。以上移相器均满足高性能的设计需求,但集成度可以继续提升。

笔者提出一种宽带、高性能的网络切换型移相器,通过改良90°移相单元电路实现芯片面积缩小,对于降低移相器的成本具有重要意义。移相器包含6个移相单元,分别对应相移180°、90°、45°、22.5°、11.25°和5.625°,通过开关控制可形成步进为5.625°的64种移相状态。电路基于0.18 μm SiGe BiCMOS工艺完成设计,相比砷化镓工艺,硅基芯片具有低成本、中等射频性能和高集成度等特点。

1 移相基本原理

1.1 滤波网络

当输入信号通过高通滤波网络时,输出信号的相位超前于输入信号;当输入信号通过低通滤波网络时,输出信号的相位滞后于输入信号,因此单个滤波网络可以视为单位移相单元。以三阶π型低通滤波结构为例,其电路结构如图1(a)所示。

(a) 三阶π型低通滤波结构

计算该二端口网络的传输函数为

(1)

则可以得到路径实现的信号相位延迟为

(2)

同时可计算该网络端口的反射系数为

(3)

其中,Z0为特征阻抗,ω为工作频率。将如图1(a)所示的多个移相单元级联,并内嵌控制开关对各单元电路的移相状态进行切换,得到如图1(b)所示的由电压控制的数控网络切换型移相器。

1.2 内嵌MOS管开关及其优化

笔者在设计时采用如图2(a)所示深阱NMOS管作为电路内嵌开关。对晶体管衬底进行单独偏置,如图2(b)所示,将体端通过一个大电阻(如10 kΩ、20 kΩ)连接到地,从而消除通过寄生电容Csb和Cdb到地面的通路信号,与传统开关相比,衬底相对于地电位悬空,因此该优化方式称为浮体技术。通过浮体技术减弱射频信号泄漏,降低了开关的插入损耗。同时在晶体管的栅极上接一个大电阻(如10 kΩ、20 kΩ),以避免信号通过栅漏、栅源的寄生电容泄漏到地面,这也会减少开关导通时的插入损耗。

(a) 深阱NMOS剖面图

该优化方式通过了仿真结果的验证。对同一尺寸的晶体管做开关特性测试,如文中所选晶体管总栅宽为1 μm×10、栅长为350 nm,分别对普通NMOS晶体管、栅极偏置大电阻的普通NMOS晶体管、采用栅极偏置及浮体优化技术的同尺寸深阱NMOS晶体管进行频带为1~30 GHz的后仿真,结果如图3所示。由图3(a)、(b)可见,相比栅极偏置技术,深阱浮体技术可以大大减小插入损耗即S21,可为该尺寸晶体管带来约5dB的幅值变化,而栅极偏置技术则在高频时有正向的影响。通过图3(c)中对截止电容的对比,可见该类方法对插损优化同时,几乎不会影响开关隔离度。

(a) 导通电阻

2 移相器电路设计及分析

2.1 小移相单元电路

5.625°、11.25°、22.5°为小移相单元,采用低通/带通网络切换结构,电路拓扑结构如图4(a)所示。当M1导通、M2截止时,等效电路如图4(b)所示,输入信号经过M1形成的等效电阻Ron1,不发生相对相移,该路径下的信号相移作为参考态相位,此时电感L2与M2的截止电容Coff2谐振,提高隔离度以阻止信号泄漏。当M1截止、M2导通时,电路在Ron2(M2导通等效电阻)足够小的前提下形成如图4(c)所示的π型三阶低通滤波结构,并将通过的信号进行相位延迟后置,电路此时处于移相工作状态。交流输入信号在MOS管M1、M2导通,截止交替切换中通过两条不同的路径实现相移差完成目标移相。

当电路网络端口阻抗匹配时,反射系数应满足

|S11|=0 。

(4)

当电路无损耗时,传输系数应满足

|S21|=1 。

(5)

联立式(2)至式(5),可推导出在不考虑NMOS管开关影响下的L1、C1理论值计算公式:

(6)

(7)

另外,取M2的截止态等效电容Coff2,由谐振关系可计算L2的理论值,可表示为

(8)

45°单元电路拓扑结构如图4(d)所示,在图4(a)电路基础上增加一个并联电容C2。45°单元移相度数增大导致M2栅宽减小,因此为达到工作频率下有效谐振,电感L2值过大。为提高移相精度和节约面积,在M2源、漏两端并联电容C2以增大C1与地之间的隔离电容。由式(8)可知,在所需工作频带内谐振电感L2可以相应减小。该单元电路的工作原理与5.625°、11.25°、22.5°的单元电路的一致。由于该结构信号通路中只有一个MOS管作开关,插入损耗较低。

(a) 5.625°~22.5°单元电路

2.2 90°移相单元电路

90°属于大移相单元,图4中电路结构很难实现所需带宽内的平坦相移。为了实现90°移相,大部分数字移相器采用高/低通切换拓扑结构[8,16-18]或高通/带通切换[9-10,12-13,15]来设计该单元,而大量的无源大电感导致电路面积较大,如图5(a)所示电路结构。

笔者提出一种新的90°电路结构,如图5(b)所示,采用低通/带通滤波网络切换来实现移相。M1、M2同时截止时电路处于参考态,等效电路图如图5(c)所示,其中Ceq为M1截止电容Coff1与C2并联的等效电容,通过电容Ceq与L1、Coff2与L2的两次谐振,形成带通滤波器,使信号通过该滤波结构后在目标工作频带内保持相对不变。令Ceq与L1在所需频率谐振,则串联支路阻抗达到最小,等效于纯电阻r,此时串联支路阻抗远小于并联支路电容阻抗,信号通过等效电阻r相位几乎不受影响;令M2截止电容Coff2与L2在所需频率实现谐振,达到阻抗最大,提高电路与地之间的隔离。90°移相态电路如图5(d)所示,M1、M2导通,串联电感L1与并联电容C1形成低通滤波结构,实现相位延迟。两种状态电路切换信号做差,可以在工作频带内实现90°移相。

(a) 传统90°移相单元电路结构

2.3 180°移相单元电路

180°移相单元采取高/低通切换型网络结构,以保证在工作带宽内移相稳定,电路如图6所示。每条支路由两个MOS开关管和高通/低通无源移相元件组成,M1导通M2截止时形成五阶低通滤波支路,M1截止M2导通时形成三阶高通滤波支路,通过计算及调整器件值,使经过两条支路的信号具有相同的相位斜率且保证两者相位差为180°。

图6 180°移相单元电路图

2.4 移相单元级联及移相器版图

移相器整体电路如图7(a)所示,V0至V5为可变控制电压,分别连接5.625°至180°各单元开关MOS管的栅极,通过控制电压在0~1.8 V之间的切换实现6位移相器。级联顺序需考虑各单元的端口匹配,一般将反射系数较好的单元放在较差单元的两端,以实现电路整体性能最优,本次设计采用22.5°/180°/ 45°/5.625°/11.25°/90°的连接顺序。图7(b)为最终电路版图,其面积为1.68 mm×0.64 mm,在版图布局设计中,合理布局器件和走线,尽可能缩短电路走线,节约版图面积,降低电路中的寄生阻抗。

(a) 移相器电路原理图

3 仿真结果

移相器采用0.18 μm SiGe BiCMOS工艺设计,直流工作电压为1.8V。为对版图元器件和非理想寄生效应提取更为全面,对于无源电感、互连线部分使用ADS Momentum进行电磁仿真,对于晶体管部分进行PEX参数提取,最终进行联合仿真。这种仿真处理方式使结果更接近测试结果。电路通过Cadence、ADS工具完成版图的设计及验证。

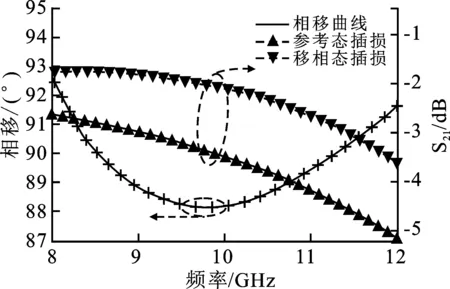

6位移相器各主要性能如图8~图9所示。其中,结构创新的90°移相单元在工作频带内性能如图8所示,其相移为88.3°~92.6°,满足相移低误差的要求。参考态插入损耗为-1.8~-3.6 dB,移相态插入损耗为-2.6~-5.04 dB。移相器无源结构在移相态下,随着频率增加趋近于表现出低通滤波特性,且随着频率的升高,电感寄生效应更加明显,而参考态引入的串联电容抵消了部分电感,使得频率升高时插损增加速度小于移相态,导致两者幅度差值在工作频率内随频率的增大而增大,但对电路整体影响尚可。

图8 90°单元仿真结果

移相器整体工作的64位相移如图9(a)所示,在8.3~12.0 GHz的频带内,各相位曲线不发生交叠,移相性能良好。8~8.3 GHz频带内发生交叠的是174.375°移相曲线与180°曲线,主要原因是各移相单元在低频处实际移相值均略大于所需移相,174.375°为5位单元移相的叠加,因此误差较大,从而造成174.375°低频时相位曲线上曲,与180°曲线交叠。图9(b)为移相器的各工作状态下插入损耗仿真曲线,无源器件和开关导致高频时插损较大,最大值为-16.7dB,最小插损为-8.36 dB,其中,该6位移相器参考态相位曲线,即相对相移为0°时的插入损耗为-11.35~-14.21dB。

(a) 移相器相位曲线

通过计算得出,在8~12.0 GHz带宽内,最大移相RMS误差为4.20°,最大幅度RMS误差为1.47 dB。在8.3~12 GHz的工作频带内,移相RMS误差均小于等于2.5°,最大幅度RMS误差为1.25 dB,各自随频率变化如图9(c)所示。图9(d)至图9(e)所示为移相器在64种工作状态下的输入、输出端口回波损耗。

表1所示为笔者设计的移相器与几种硅基移相器[7,10,12-13,15]主要性能及版图面积对比。

表1 移相器对比

4 结束语

基于0.18 μm SiGe BiCMOS工艺,笔者设计了一款工作于X波段的6位数控移相器,这是一款采用深阱MOS管做支路内嵌开关的网络切换型移相器,电路设计紧凑。其中针对90°移相单元进行了优化设计,提高单元移相精度及电路集成度。在8.3~12.0 GHz的工作频带内,所制移相器64种状态的插入损耗均小于-16.7 dB,移相均方根误差均小于等于2.5°,幅度均方根误差均小于等于1.25 dB。该移相器适用于相控阵系统。