氮钝化对SiC MOS电容栅介质可靠性的影响

白志强,张艺蒙,2,汤晓燕,宋庆文,2,张玉明,戴小平,高秀秀,齐 放

(1.西安电子科技大学 微电子学院,陕西 西安 710071;2.西安电子科技大学 芜湖研究院,安徽 芜湖 241000;3.湖南国芯半导体科技有限公司,湖南 株洲 412000)

由于碳化硅(Silicon Carbide,SiC)功率金属氧化物半导体场效应晶体管(Metal Oxide Semiconductor Field Effect Transistor,MOSFET)具有栅极驱动电路简单、开关速度快、功率密度高等优势,其在各种电力电子系统有着广泛的应用前景[1-4]。然而,SiC金属氧化物半导体(Metal Oxide Semiconductor,MOS)结构中存在多种类型的陷阱种,使其氧化层(SiO2)质量较低,这严重阻碍了SiC功率MOSFET器件商业化应用水平的提升。目前业界主流的栅氧钝化方法是在热氧化后采用一氧化氮(Nitric Oxide,NO)退火工艺[5-6],该方法可以降低界面态密度,从而提高MOS结构器件的界面质量[7-8]。然而,有研究表明氮退火工艺会增加4H-SiC/SiO2界面处的空穴陷阱[9-11],这可能会对器件负向的阈值稳定性带来严重的影响。因此,需要对NO退火引入的空穴陷阱进行有效评估。若采用n型4H-SiC MOS电容器,需要额外的辐照条件才能产生足够的空穴,难以实现对空穴陷阱的有效表征[12]。文献[13]利用p型MOS电容发现增加氮钝化时间会增大近界面空穴陷阱的含量,但缺少氮钝化对平带电压漂移和栅介质可靠性方面的研究。笔者开展平行电导峰测试和双向电容-电压(Capacitance-Voltage,C-V)测试,对比研究了不同NO钝化时间对n型和p型电容的电学特性影响。通过室温和高温电压应力测试研究NO退火时长对平带电压漂移的影响,从而反映出对阈值稳定性的影响。通过栅漏电测试研究了NO退火时长对器件栅介质可靠性的影响。

1 实验方案

实验对比研究了不同NO退火工艺对4H-SiC/SiO2界面附近电子陷阱和空穴陷阱的影响。采用n型MOS电容表征电子陷阱,因为其在表面积累状态时,费米能级接近导带底,此时费米能级的位置与N沟MOSFET的反型状态相对应。通过n型MOS电容电子陷阱的表征能反映出其对N沟MOSFET迁移率、平带电压、阈值电压以及阈值电压正向漂移的影响。而p型MOS电容可以弥补n型MOS电容无法表征空穴陷阱的缺陷,通过p型MOS电容的表征能反映出空穴陷阱对N沟MOSFET平带电压和阈值电压以及阈值电压负向漂移的影响。由于p型MOS电容表面积累时费米能级接近价带顶,其C-V曲线不能反映出对N沟器件迁移率的影响。笔者采用氮和铝掺杂的SiC同质外延片分别制备了n型和p型MOS电容样品。n型和p型MOS电容的外延层掺杂浓度均为4×1016cm-3,厚度均为5 μm。实验样品分为3组,所有样品在1 250℃[13]条件下同时进行干氧氧化50 m,氧化后在1 250 ℃条件下进行不同时长的NO退火和氮气(Nitrogen,N2)退火工艺。详细参数如表1所示。

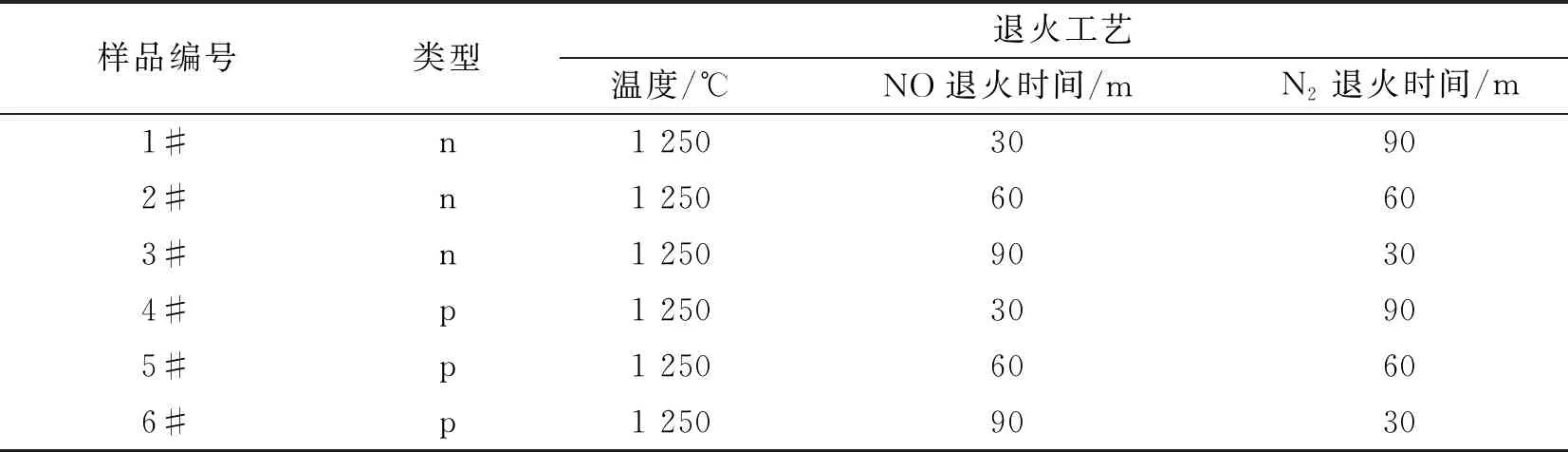

表1 不同样品的NO退火工艺

为了使所用样品具备可表征的界面特性,同时考虑到不同退火条件的样品之间的区分度,NO退火时间控制在30到90 m之间,以30 m为间隔。N2退火工艺的设置是为了使所用样品具有相同的热处理时间,其惰性气体特征对界面特性的影响可以忽略。最终生成的栅氧化薄膜厚度约为30 nm,所用电容样品的电极面积均为9×10-4cm-2。

首先,对n型MOS电容样品开展平行电导峰测试,表征其界面质量。然后对不同NO钝化时间的n型和p型电容样品进行C-V回滞测试,评估不同样品的近界面陷阱。测试中采用的频率为1 MHz,电压从电容的耗尽态扫描到积累状态,再回扫到耗尽态。利用电压应力测试(Time Dependent Bias Stress,TDBS),分别表征了室温(300 K)和高温(450 K)应力后MOS电容样品的平带电压漂移,比较不同NO退火时长样品的氧化层中电子陷阱和空穴陷阱的量。TDBS测试中n型电容的所施加的电压应力为+5 MV/cm,应力时长为1 h;p型电容的所施加的电压应力为-5 MV/cm,应力时长为1 h。对施加电压应力后的样品进行了C-V特性测试,比较应力前后的平带电压漂移。此外,通过电流-电压(Current-Voltage,I-V)特性测试对比了不同NO退火样品的栅漏电,评估其栅介质可靠性。文中电容样品的电学特性均是通过Keysight B1505A半导体分析仪测试得到的。

2 结果与讨论

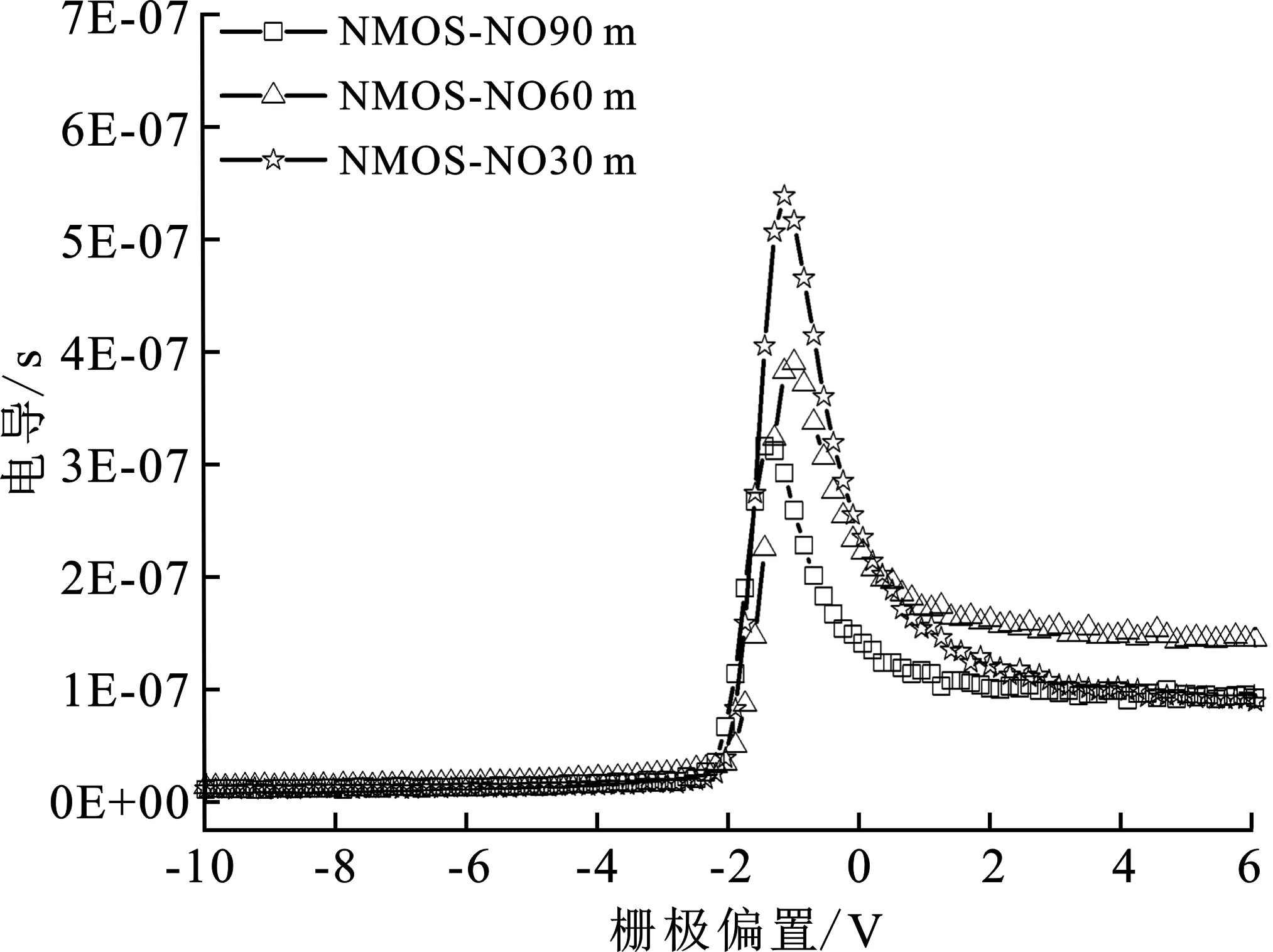

图1为不同NO退火时长的n型MOS电容样品的平行电导峰测试结果。随着NO退火时间的增加,n型MOS电容样品的电导峰值明显减小,表明NO钝化工艺可以有效降低4H-SiC MOS结构器件的界面陷阱密度,从而提升N沟MOSFET的沟道迁移率,降低导通电阻。同时注意到随退火时间的增加,电导峰的降低会逐渐趋于饱和。

图1 不同NO退火时长的n型MOS电容样品的平行G-V特性曲线

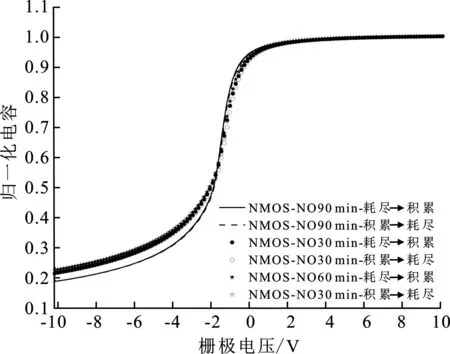

不同NO退火时长的n型和p型MOS电容样品初测的回滞C-V曲线测试结果如图2所示。

(a) n型

NO退火90 m的样品在初测C-V曲线中部存在一处非常明显的台阶,台阶出现的位置对应于4H-SiC价带顶以上0.5~0.6 eV左右,这说明在p型MOS电容中出现了某种深能级陷阱[13]。高频C-V测试过程中,在直流电压信号的作用下费米能级移动到深能级陷阱附近时,深能级陷阱会随着交流小信号捕获和释放电荷,形成一个与深能级陷阱有关的附加电容。正是这个附加电容导致了MOS电容曲线的畸变。

通过n型和p型MOS电容初测的回滞曲线,代入式(1)可以分别求得近界面电子和空穴陷阱的有效面密度(DNITs):

(1)

其中,Cup和Cdown分别为电压从耗尽扫到积累和电压从积累扫到耗尽的电容;S为MOS电容的电极面积。

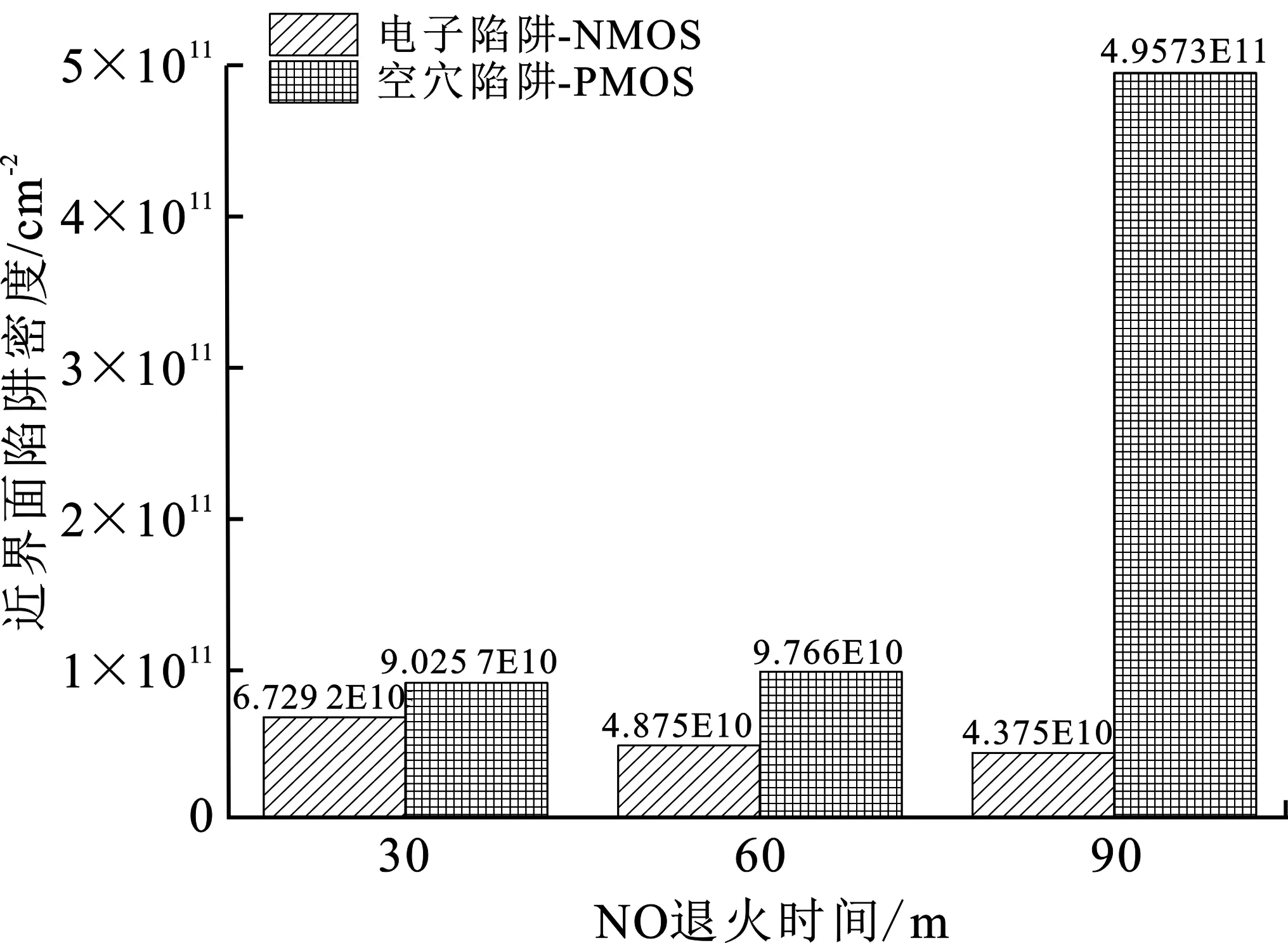

图3展示了由不同样品的近界面陷阱密度。可以看出,在n型MOS样品中随着NO退火时间从30 m增加到90 m,近界面电子陷阱密度从6.7×1010cm-2减小到4.3×1010cm-2。而p型MOS样品中近界面陷阱密度随着NO退火时间的增加而增加,退火时间90 m的情况增加尤为明显,高达4.9×1011cm-2。空穴陷阱的增加会对迁移率和导通电阻带来负面影响,同时造成阈值电压的负向移动,严重时会导致器件常开。

图3 不同NO退火时长的n型和p型MOS电容的近界面陷阱密度

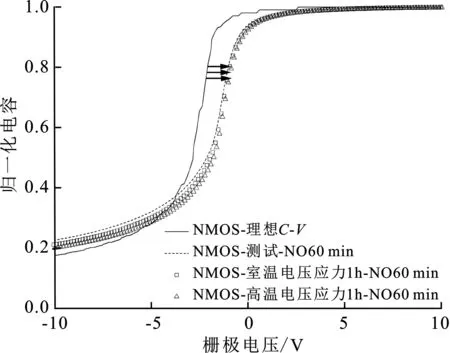

图4为n型和p型MOS样品在初始测试,室温电压应力和高温电压应力后测试得到的典型C-V特性曲线。图中虚线为理想C-V曲线。

(a) n型

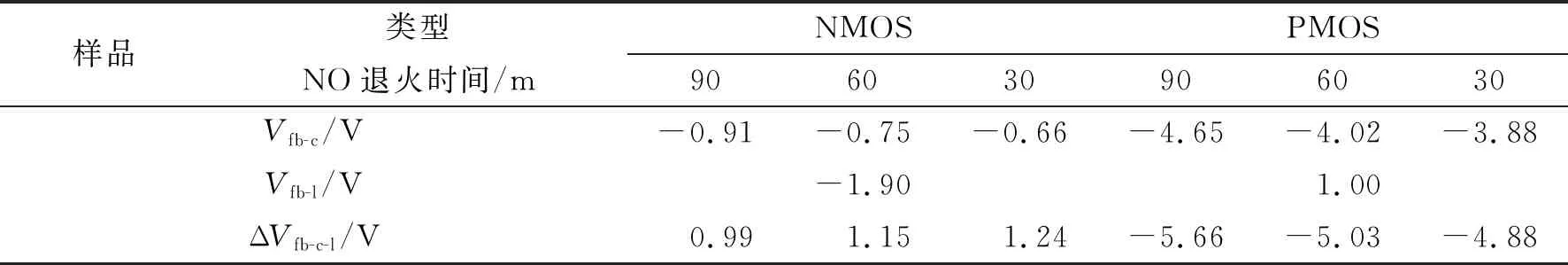

提取得到不同样品初始的平带电压[14]相对于理想平带电压的漂移如表2所示。

表2 不同样品的平带电压相对于理想平带电压的漂移

相对于理想平带电压,不同NO钝化时长的NMOS样品测试的平带电压均往正向移动。而随NO钝化时间的增加,平带电压的正向漂移量从1.2 V减小到0.9 V,表明样品栅氧化层中显负电性的有效固定电荷密度在减小。而相对于理想平带,PMOS样品测试的平带电压均往负向移动。随NO钝化时间的增加,平带电压的负向漂移量从4.8 V增加到5.0 V,表明样品栅氧化层中显正电性的有效固定电荷密度在增加。

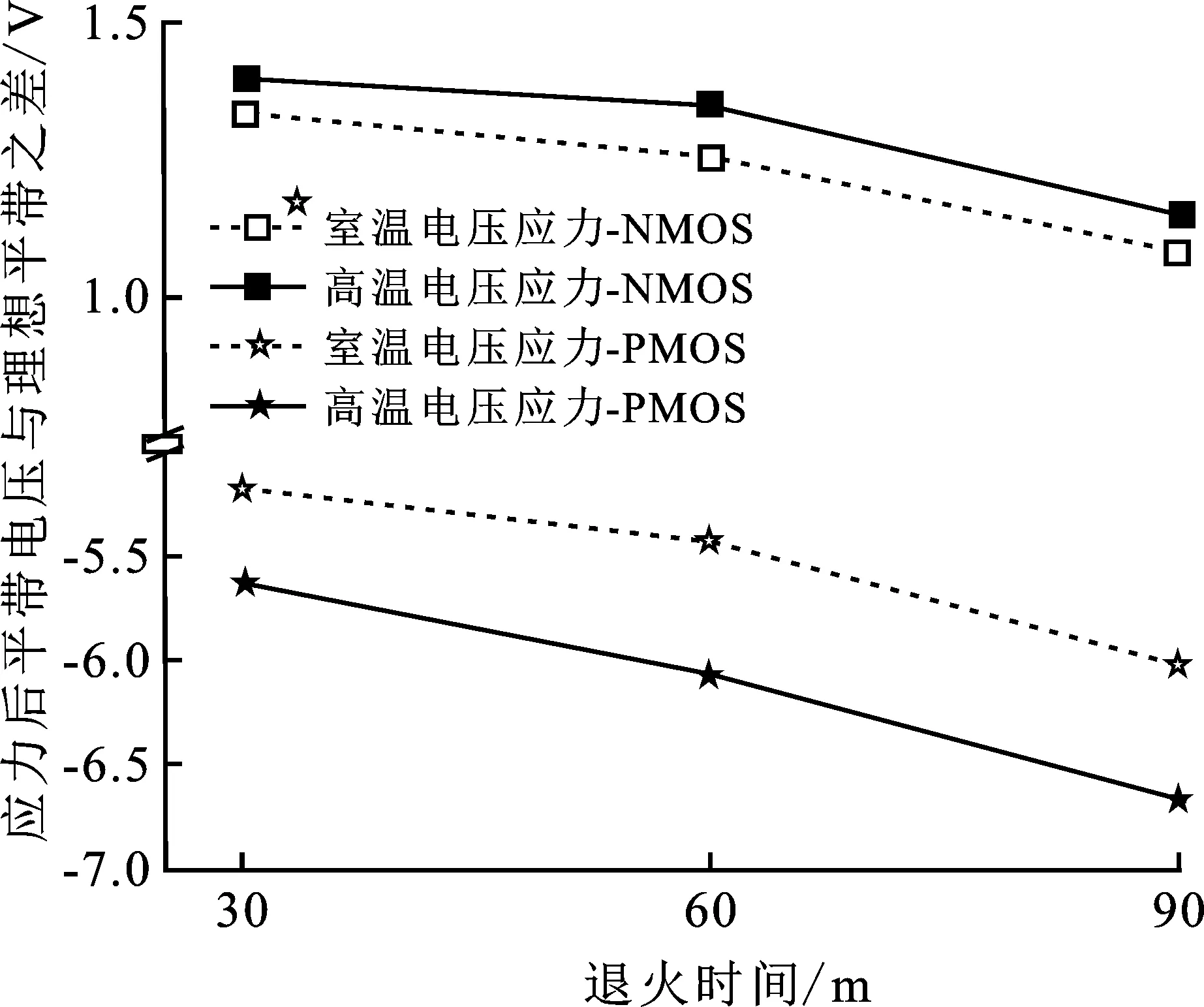

根据图4所示的室温和高温下电压应力后测试的C-V曲线,得到不同样品在应力后的平带电压相对于理想平带电压的漂移量如图5所示。可以看出,无论室温电压应力测试还是高温电压应力测试,在正向应力后NMOS的平带电压正向漂移;负向应力后PMOS的平带电压负向漂移。并且PMOS平带电压的负向漂移明显高于NMOS平带电压的正向漂移,在相同时间室温电压应力后,随NO退火时间从30 m增加到90 m,NMOS电容的平带电压正向漂移量从1.3 V减小到1.0 V;而PMOS电容的平带电压负向漂移量从5.1 V增加到6.0 V,表明氮钝化时间的增加会减少氧化层中的电子陷阱,但会引入额外的空穴陷阱。对器件长期工作的可靠性影响是改善了阈值电压的正向稳定性,但会恶化阈值电压的负向稳定性。此外,高温电压应力后平带的漂移趋势与室温情况相同,漂移量明显大于室温电压应力后的漂移量。这是因为高温会激活更深层的氧化层陷阱,从而在电应力作用下俘获电荷而引起更严重的平带漂移。

图5 不同NO退火时长的MOS电容在相同时间的室温和高温电压应力后的平带电压与理想平带电压的漂移量比较

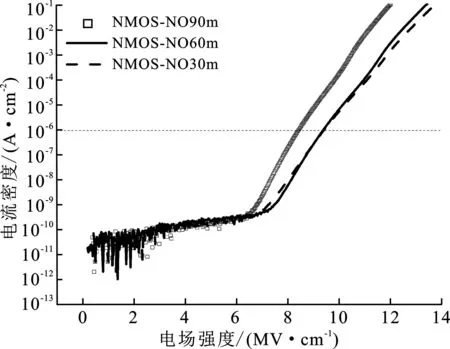

对不同NO退火样品在黑暗环境中进行I-V特性测试。利用式(2)将I-V曲线转化成电流密度-电场(Current Density-Electric Field,J-E)关系曲线,如图6所示。

(a) n型

(2)

其中,E为电场强度,V为测试电压,Vfb为样品的平带电压,tox为氧化层厚度。

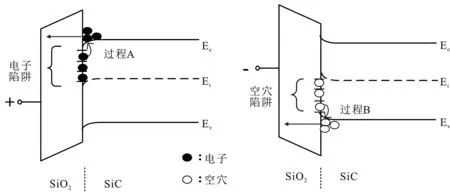

对于n型MOS电容来说,对应于N沟MOSFET器件工作时的开态。NO退火时间从30 m增加到60 m并未对样品栅漏电特性产生明显影响。NO退火时间从60 m增加到90 m后,福勒-诺德海姆(Fowler-Nordheim,F-N)隧穿点从7.2 MV/cm提前到6.5 MV/cm,漏电流也更早达到击穿定义的漏电流值(1×10-6A/cm2),这个击穿电流值用于表示器件定义的安全工作值而非栅介质的永久性击穿[15]。由此可见,过度的氮钝化会减小器件正常工作的正向栅偏置范围。对于p型MOS电容来说,对应于N沟MOSFET器件工作时的关态。NO退火时间从60 m增加到90 m后,F-N隧穿点从-6.1 MV/cm移动到-6.9 MV/cm,在相同的电场强度下,漏电流有明显的下降。这表明氮钝化能扩大器件关态时的负向栅偏置范围。NO退火工艺对n型和p型MOS电容栅漏电特性产生的不同影响可以从它们的能带结构中得到解释。n型MOS电容的情况如图7(a)所示。在正栅极偏置作用下,半导体表面电子积累,能带向下弯曲。同时被界面陷阱俘获的电子重新发射至导带底(过程A)。90 m退火样品界面处有更少的电子陷阱,过程A明显减少,相同的栅极偏置下能带会下弯得更严重,施加在栅氧化层上的压降更多,导致F-N隧穿点提前。p型MOS电容的情况如图7(b)所示。在负栅极偏置作用下,半导体表面空穴积累,能带向上弯曲。同时被界面陷阱俘获的空穴重新发射至价带顶(过程B)。90 m退火样品界面处有更多的空穴陷阱,过程B明显增加,相同的栅极偏置下能带下弯得并不严重,施加在栅氧化层上的压降减少,导致F-N隧穿点滞后。注意到在测试的初始阶段,p型MOS电容样品的I-V曲线中存在一段凸起。这种凸起与电压应力下空穴对界面附近陷阱的填充有关[16]。

(a) n型 (b) p型

3 结束语

笔者分别制备了n型和p型4H-SiC MOS电容以研究不同NO退火时长对SiC MOS结构器件栅介质可靠性的影响。n型MOS电容样品的平行电导峰测试结构表明增加NO退火时间能够有效降低SiO2/SiC界面陷阱密度;随着退火时间的增加这一改善会趋于饱和。通过回滞C-V测试发现,随着NO退火时间的增加,n型MOS样品的近界面电子陷阱在减小;而p型MOS样品的近界面空穴陷阱在增加,NO退火时间为90 m的情况下增加尤为明显。室温和高温电压应力测试结果显示正向应力下n型MOS电容平带电压正向漂移,负向应力下p型MOS电容平带电压负向漂移;且负向漂移量明显大于正向漂移量,高温情况下的漂移量大于室温情况。更重要的是,随着NO退火时间的增加,正向漂移减少的同时负向漂移在明显增加。这表明NO退火能提升器件长期工作中阈值电压的正向稳定性,但会更明显地恶化阈值电压的负向稳定性。在I-V特性测试中,增加NO退火时长会恶化NMOS样品的栅漏电特性,而PMOS样品的栅漏电特性则会得到改善。这会减少器件正常工作时的正向栅偏置范围,扩大器件关态时的负向栅偏置范围。因此,综合考虑不同NO退火时长对n型和p型MOS电容的影响,氮退火时间的选择需要从沟道迁移率、阈值电压正向漂移的改善与阈值电压负向漂移的恶化两方面进行折中,同时还需考虑其对器件正向和负向栅偏置范围的影响。文中的实验结果为工艺参数的选择提供了有益的参考。