一种通用SDR平台的设计与实现

张仁良, 周昌义, 胡婉如,2, 安军社

(1.中国科学院 国家空间科学中心,北京 100190; 2.中国科学院大学 计算机科学与技术学院,北京 101408)

软件无线电(Software-Defined Radio,SDR)具有结构开放、软件可编程、硬件可重构和支持多种频段等特点,在现代通信系统中占据着重要的地位,无论在军事[1]、微小型卫星[2],还是在商业通信[3]中都有很大的影响力。

SDR主要特点是通用化、标准化、模块化和对频段的广泛覆盖性。硬件系统本身支持的频段或者通过扩频再结合软件配置,基本可以满足多种通信场景中应用的需求。

随着国外各种先进技术应用于SDR平台,目前基本实现了3个目标:① 高度集成化;② 模块化;③ 面积最小化。AD9371[4]是最具代表性的一款集成电路(Integrated Circuit,IC),内部提供可靠的链接,包含了20多个高性能分立式无线电元件,极大减小了芯片面积,纯die(芯片)仅为7.8 mm×8.2 mm。NI公司的USRP(Universal Software Radio Peripheral,通用软件无线电外设)[5]是模块化的代表,其封装为一个黑盒子,用户连接外部设备再配合上位机即可使用。国内主流的SDR平台实现方法有两种:① 依赖于离散元件的组合[6];② 采用国外的模块化方案,例如使用AD9361[7]、AD9364等一体化射频芯片和Radio420s射频板[8]等搭建平台。

本文提出一种较为先进的SDR平台,其目的是使用SDR方式,灵活地改变通信的参数,适用于多种应用场景,例如作为地检测试应答机与无人机、直升机进行通信,通过软件可以直接设置相关参数,极大地提高了配置的灵活性,扩大了应用范围。

1 硬件设计方案

Kintex7嵌入了MicroBlaze软核,可以对AD9371进行配置,收到的RX信号解调为基带信号,经过ADC转换和滤波后送入JESD204B接口,发出的信号通过JESD204B接口送出,再经过滤波及DAC转换和混频后输出到TX接口。完成这些操作需要一个硬件平台,所以笔者主要介绍整体硬件设计方案,并对选用AD9371和Kintex7来搭建平台的原因做出阐述。

1.1 AD9371外围芯片概述

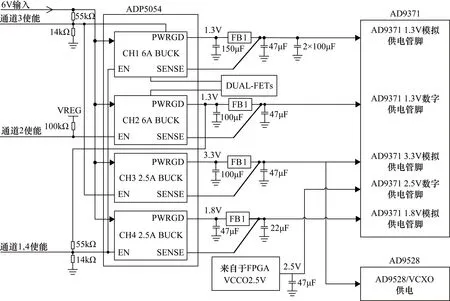

AD9371的电源供电使用四通道高性能降压DC-DC调节器ADP5054。使用14路LVDS/HSTL输出的JESD204B时钟发生器AD9528产生AD9371和Kintex7之间的同步时钟来同步高速数据总线JESD204B。

AD9371是一款高度集成的宽带RF收发器,提供2个发射器(Tx)、2个接收器(Rx)、2个观测接收器(ORx)、三通道嗅探接收器(SnRx),集成了频率合成器和数字信号处理功能。

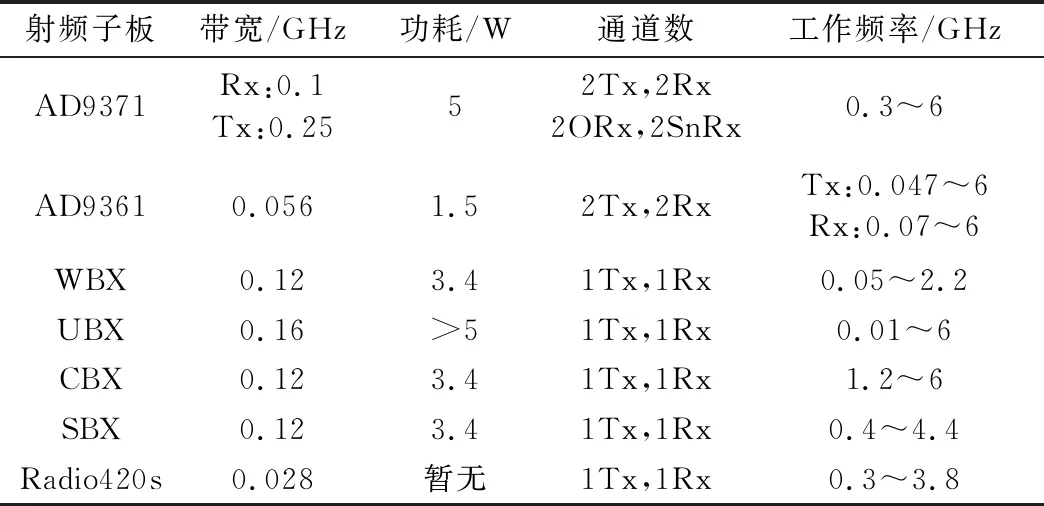

射频子板参数对比如表1所示。由表1可知,AD9371无论是在工作频率、带宽还是在通道数量上都具有明显优势,采用JESD204B串行接口[9]作为数据传输通道,最高数据率可达6144 Mbit/s。其他平台皆采用LVDS或其他并行接口进行数据传输,最高速率仅为1.0 Gbit/s。虽然其功耗在表1所列的其他平台中处于劣势,但在性能上处于第一位置。参考AD9371功能框图可知[10],其中SnRx和ORx共享ADC和数字处理器。4个高速的串行接口用于发射链路,4个串行链路被Rx、ORx和SnRx通道所共享。

表1 射频子板参数对比表

1.2 Kintex7外围芯片概述

Kintex7的外围芯片包括:4收4发的RS422接口、4收4发的LVDS高速接口、1片W5300网口芯片。其中,RS422和LVDS接口使用J14-26连接器,网口使用RJ45连接器;外接1片DDR2芯片作为存储器的扩展;外接配置Flash用于存储调制解调、JESD204B接口协议和MicroBlaze代码;1片128 Gbit的NAND Flash用于存储大量数据。

表2为对Microsemi和Xilinx公司几款FPGA的逻辑单元、收发器数量(速率)价格等方面的比对,依据性价比最终选择了XC7K410T,其在容量、速度、逻辑单元数量、价格方面都处于优势地位,对于本平台来说比较适合。

表2 FPGA产品特性对比

1.3 整体硬件原理框图

原理框图如图1所示。原理分为两个部分,其中绿色底图为Kintex7外围连接;浅蓝色底图为AD9371外围连接;中间使用箭头②表示Kintex7和AD9371的信号连接。

图1 原理框图

箭头①为AD9371的电源拓扑,采用ADI公司的ADP5054四通道BUCK作为供电芯片,AD9371电源拓扑如图2所示,模拟供电使用通道1、3、4,数字供电使用通道2以及FPGA输入的2.5 V电源。

图2 AD9371电源拓扑

通过控制使能信号,使AD9371的上电顺序为先数字1.3 V供电,再模拟1.3 V和1.8 V供电,模拟3.3 V可以任意时间上电。

图3为AD9371与Kintex7之间的信号流及射频接口,SPI配置信号和高速串行数据总线JESD204B是AD9371与FPGA之间的主要连接信号。其他需要重点注意的信号主要有:同步辅助、复位、测试和GPIO信号。

图3 AD9371与Kintex7信号流图

2 PCB设计注意事项

遵守AD9371的PCB设计规则是该硬件系统成功的重要前提,下列四点对于提升硬件性能具有重要意义。

① 叠层和阻抗匹配。

② 布局时模拟部分和数字部分分开。

③ 需要根据优先级布线,先布高优先级的信号线,再布低优先级的信号线。

④ 各RF射频信号中引入隔离结构,以达到通道之间的隔离度要求。

2.1 叠层和阻抗匹配

PCB板为14层盲埋孔混压板,顶层和底层使用Rogers基材降低高频损耗。Rogers基材下的层2和层13为GND层,作为RF传输线的参考平面,以保证信号的完整性。为了实现电源通道之间的良好隔离,层3和层12用于电源域的布线。高速串行接口JESD204B在层5和层10布线,以达到RF信号和高速数字信号良好隔离的目的。余下的低速数字控制信号布在层7和层8。

为了在不改变现有叠层的情况下增加线宽,对RF信号走线使用单独的阻焊开窗模型。

2.2 布局原则

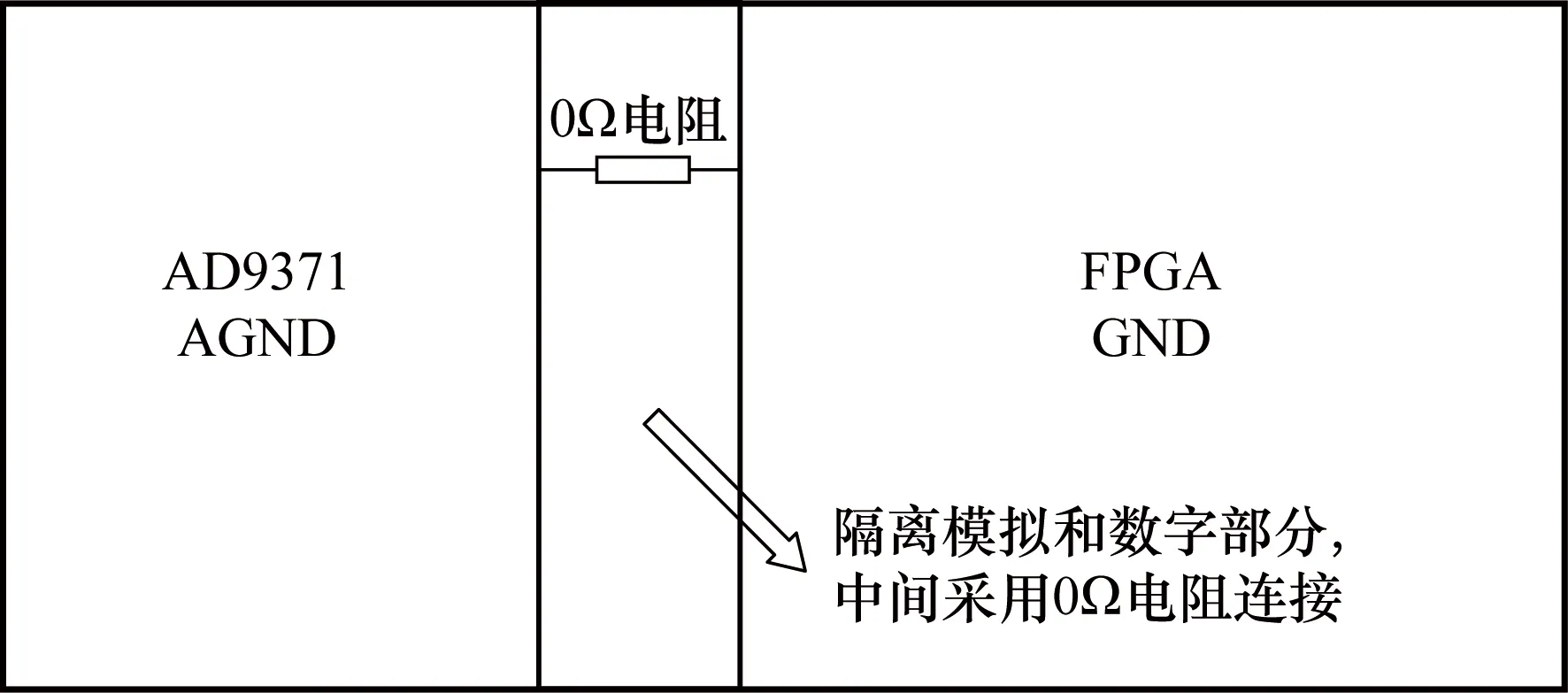

AD9371模块(模拟电路)和Kintex7模块(数字电路)是本硬件电路设计的两个主要组成部分。AD9371和Kintex7模块布局如图4所示,为了减少两个模块之间的信号和回流干扰,将AD9371模块摆放在左边,Kintex7模块摆放在右边。另外,将AD9371模块的地命名为AGND,Kintex7模块的地命名为GND,铺地阶段AGND和GND单独铺地,中间使用0 Ω电阻或铜皮连接,极大地减少了二者之间的回流干扰。需要注意AD9371模块表层与内层铺地需要保持一致。

图4 AD9371与Kintex7模块布局示意图

2.3 布线优先级

为了保证AD9371的关键信号可以在PCB设计阶段就获得足够的设计优化空间,第一优先级是RF和JESD204B信号,二者需要最早布线。第二优先级是电源信号,最低优先级的是低速数字信号。需要严格按照布线优先级的顺序布线,以达到不干扰关键元件的布局和布线的目的。

2.3.1 第一优先级RF线设计规则

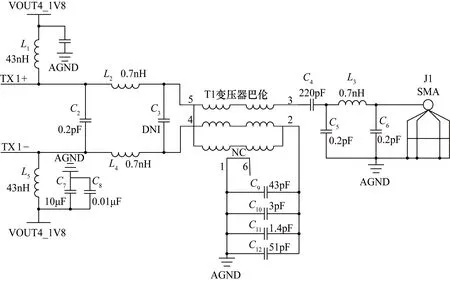

以RF发射通道1举例介绍其设计规则,图5为AD9371发射通道的电路原理图。

由于本设计的巴伦没有提供直流中心引线,所以将绕线式电感(Chokes)连接在VOUT4_1V8和Tx输出之间,以满足Tx输出所需要的200 mA电流。图5中的L1、L5为绕线式电感;C7为Tx电源的储能电容器。当改变衰减值的时候,为了有效减少静态电流,要通过1.8 V的电源域向巴伦直流供电。在进行PCB设计时候,必须将发射通道1和通道2的1.8 V供电路径做好隔离,且不允许使用铜皮连接绕线式电感,只允许使用引线直连[11]。

图5 AD9371发射通道电路原理图

2.3.2 第一优先级JESD204B线设计规则

要求在开始PCB设计时候就布JESD204B信号。为了减少JESD204B信号走线插损,要求AD9371尽可能靠近Kintex7放置,使走线长度尽可能短,保证直接芯片间互联。层5布JESD204B发射信号,层10布JESD204B接收信号,信号线上层、下层使用完整的GND平面作为参考。JESD204B走线严格控制为100×(1±10%)Ω的到地阻抗,要求差分对共面、松耦合和线宽最大。

为了保持阻抗的连续性,线宽必须尽可能接近Pin/Ball的宽度,1 oz(1 oz=35 μm)铜皮厚度,线宽至少为8 mil(1 mil=0.0254 mm),走线的参考地面不能跨分割或中断。连接器和无源元件的焊盘尺寸与JESD204B的线宽尽可能接近,以避免由于阻抗不连续导致的信号反射串扰等问题。

2.3.3 第二优先级电源线设计规则

电源供应品质直接影响整个系统性能,但遵循下面的布线要求,就可以保证各个模拟电源域之间具有良好的隔离度。为了保证每条电源布线都被地面包围,电源布线应遵循星状布线法,数字和模拟电源Ball都通过磁珠电阻的隔离后单独布线来完成供电。

图6为电源布线示例,显示了在层12上的电源布线结构,每条电源线之间通过包地和接地过孔来隔离。

图6 电源布线示例

电源引脚要求放置0.1 μF或(0.1+10)μF旁路电容,对于数字供电和JESD204B供电还需要加入100 μF滤波电容以减少低频干扰。通过铁氧体磁珠FB(Ferrite Bead)供电时,需注意FB、旁路电容应尽可能靠近Ball放置,FB必须通过引线连到储能电容器,每个Ball的FB应隔开放置以确保它们的电场互不影响。

2.4 AD9371信号隔离规则

为了确保收发器满足AD9371数据手册中的通道隔离要求,本平台需要满足以下的隔离指标要求。分为RF隔离和JESD204B隔离,二者隔离距离计算方法一致,前者计算的是隔离方口的距离,而后者是包地过孔距离,这里仅介绍RF隔离设计规则。

2.4.1 隔离结构

AD9371Datasheet中隔离参数要求如下。

① 在6 GHz时,Tx to Tx不少于80 dB。

② 在6 GHz时,Tx to Rx不少于80 dB。

③ 在6 GHz时,Rx to Rx不少于60 dB。

④ 在6 GHz时,ORx to ORx不少于60 dB。

为了实现这些目标,引入了两种隔离结构。

隔离结构由矩形槽和方口组合构成,图7展示了在本设计中所用的隔离结构。采用矩形槽主要是为了快速加大隔离区域,且PCB设计效率较高,但如果都采用矩形槽设计,就会导致其他低速和电源信号没有布线空间。方口虽然设计起来比较麻烦,但方口之间还可以进行信号布线,且不会使隔离度恶化。

图7 通道隔离结构

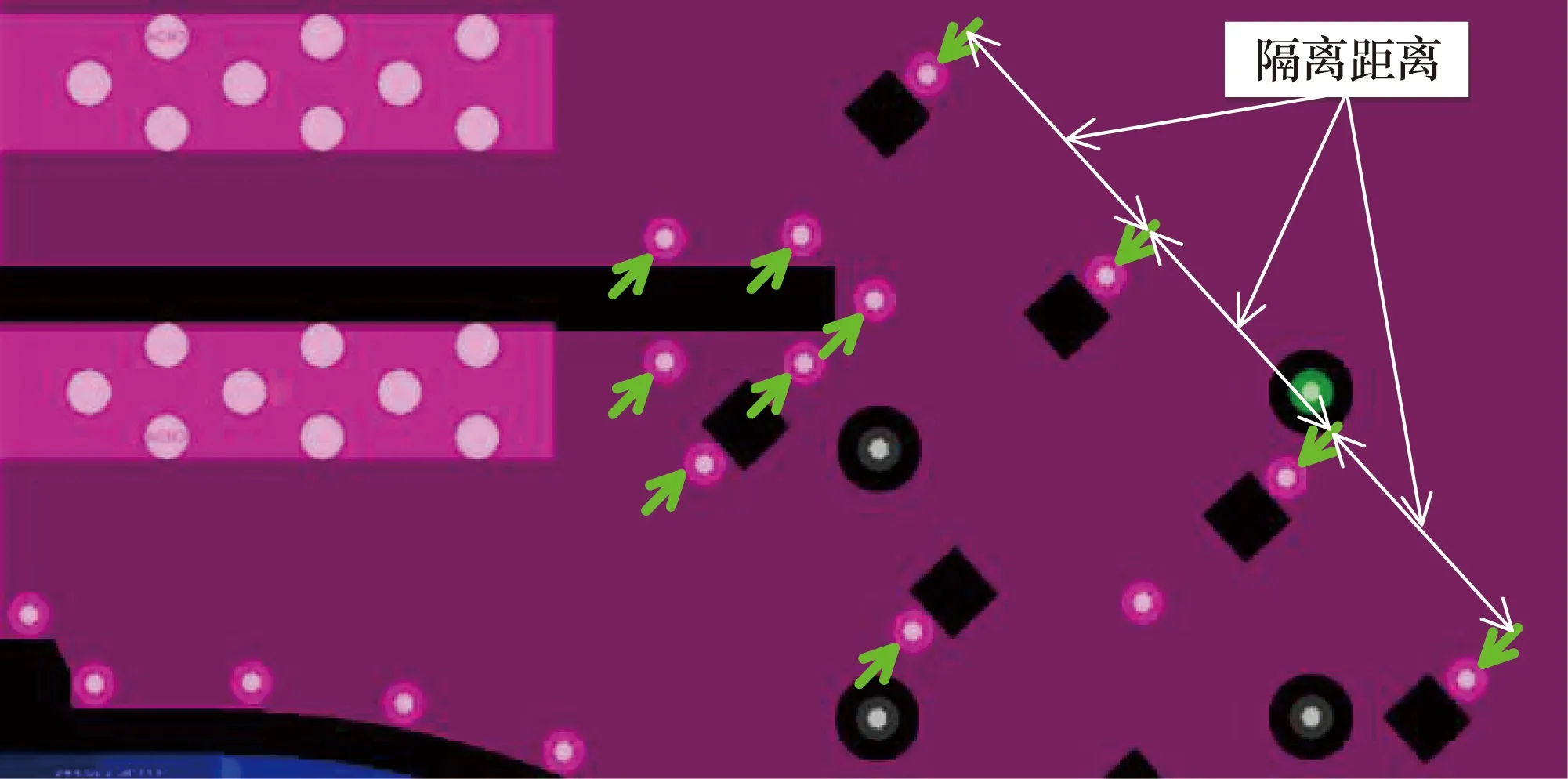

使用方口、矩形槽时,需要就近放置地过孔,可以参考图8绿色箭头所指的放置方法,方口至少需要一个,矩形槽需要在周围放置多个。过孔应是通孔,过孔的作用是就近引导返回电流到靠近方口或矩形槽的地层。

图8 放置回流过孔和隔离距离示例

2.4.2 隔离距离计算

设计PCB图纸时,方口之间的间距应不超过最高频率波长的1/10,如图8中的白色箭头所示的隔离距离。

波长可以使用式(1)来计算。

(1)

式中:εγ为隔离材料的介电常数;f为RF频率,一般取最大值;λ为RF信号波长。

AD9371最大的RF信号的频率是6 GHz。对于Rogers 4350B板材,εγ为3.5。由式(1)可计算出λ为26.73 mm,即最小的波长为26.73 mm。

为了满足1/10波长的规则,方口的间距必须小于等于2.673 mm。

3 SDR平台硬件测试

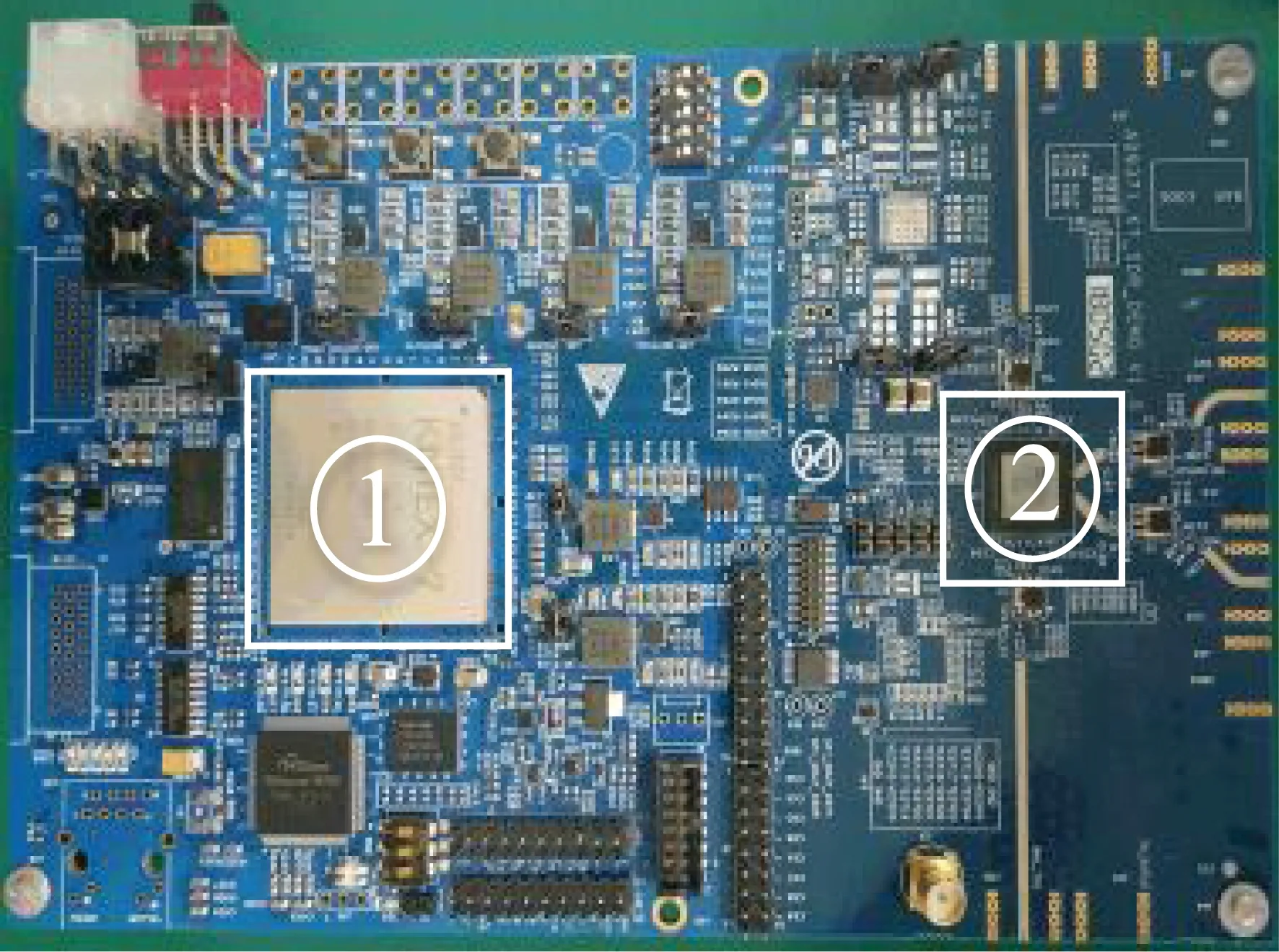

平台硬件实物如图9所示,标号①为FPGA IC,标号②为AD9371 IC,整板布局紧凑,测试也证明了此种布局分开的方法是正确的,板子性能良好,解决了模拟与数字相互干扰的问题。

图9 硬件实物

目前AD9371数据发射有两种方法,一种为DMA模式,另外一种为DDS模式。

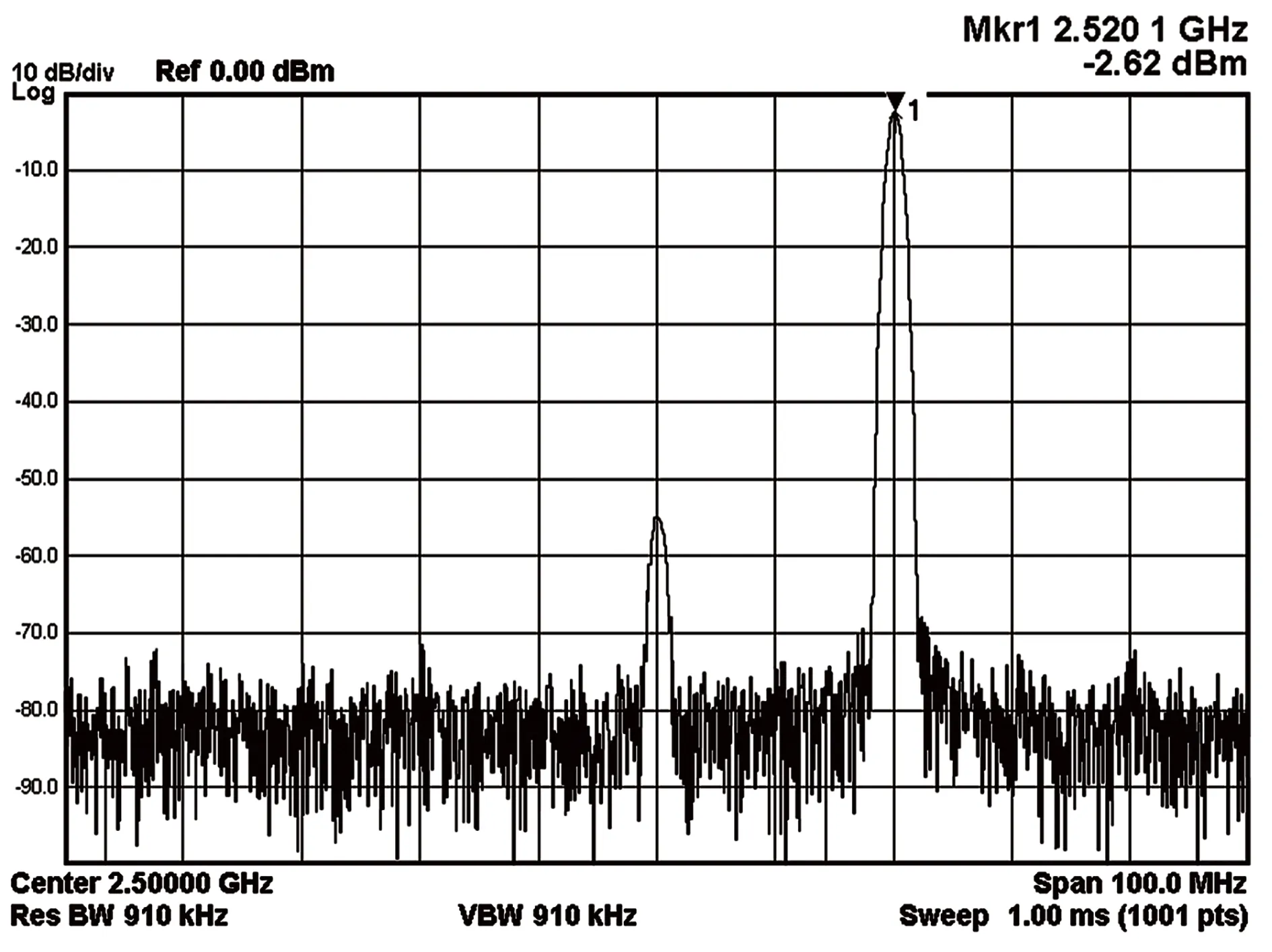

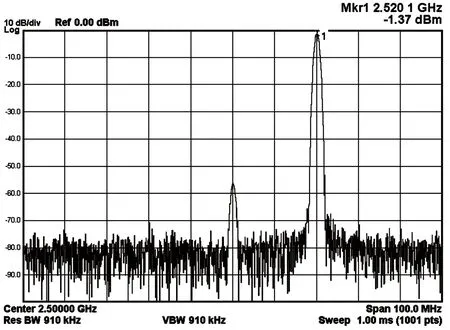

测试数据为2.5 GHz载波+20 MHz正弦波,采用DDS模式。图10为官方DEMO板对应的增益,为-2.62 dBm;图11为本平台对应的增益,为-1.37 dBm。频谱仪参考电平设为0 dBm,频宽设置为100 MHz,测试代码增益设置相同,衰减系数设为0,通过对比大量频谱仪增益数据,可以看出其明显比官方DEMO板提升了1~2 dB的增益。

图10 官方DEMO板DDS模式测试频谱

图11 本平台DDS模式测试频谱

4 SDR平台软件设计

本平台直接在MicroBlaze中跑C语言代码,过程如下[12]:ADI提供TES(Transceiver Evaluation Software)软件,此软件最大的优势在于集成了所有AD9371可以配置的寄存器,将设置好的采样、载波频率、模式、滤波器等参数直接转换为C语言代码,再配合ADI专用于配置AD9371的API接口代码,将这些代码整合到一起,使用Vivado最终生成MCS文件,将其载入到配置Flash中。当硬件上电时,逻辑代码将按照其存储的地址空间顺序载入到FPGA的SRAM中,完成MicroBlaze软核处理器的初始化,再读取配置Flash中的C语言代码,配置好AD9371。

4.1 Verilog代码框架

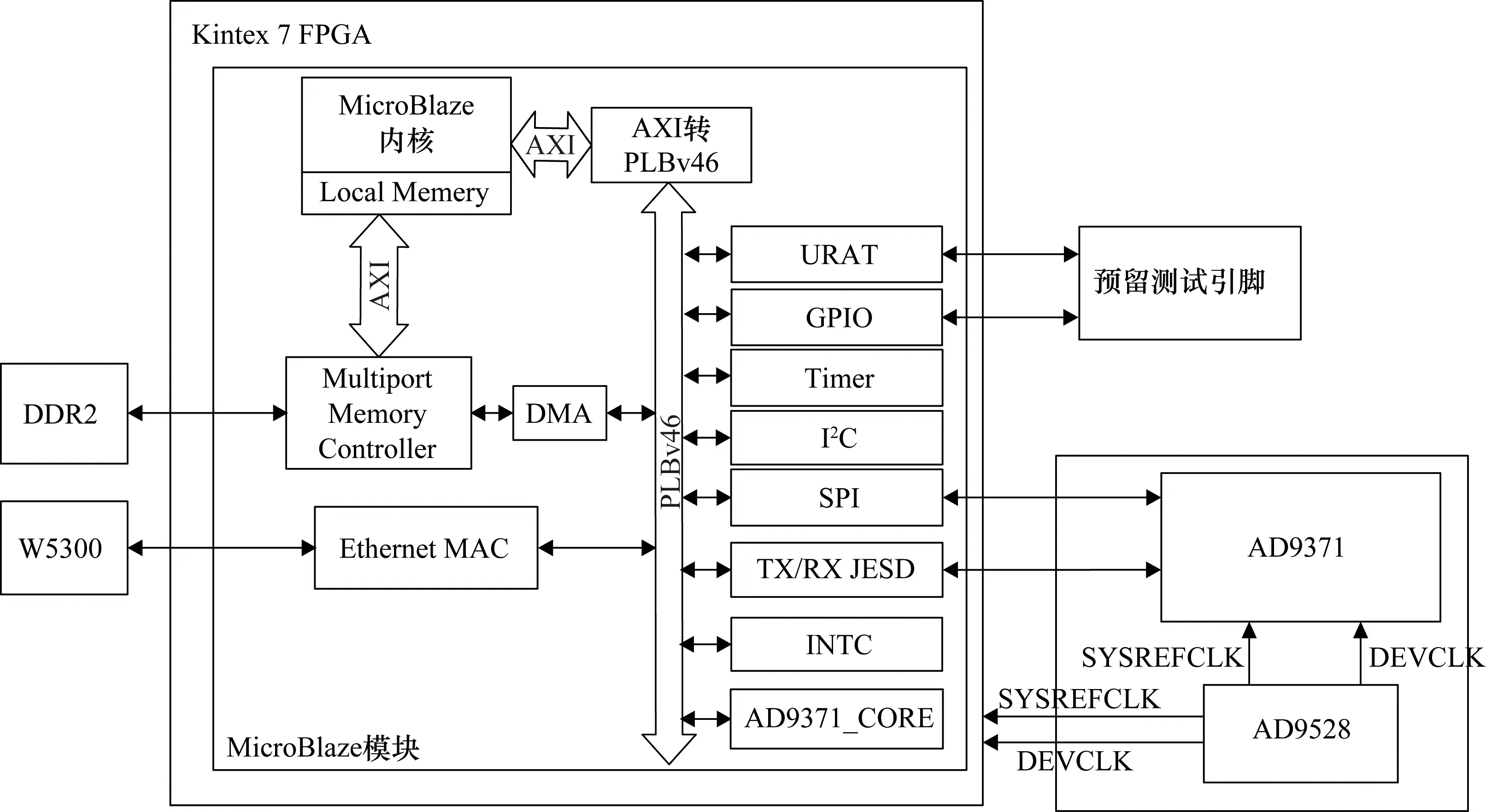

Verilog代码框架如图12所示,这里只给出部分重要的代码模块。MicroBlaze软核通过AXI总线转PLBv46总线连接低速IP模块,SPI用于配置AD9371的相关寄存器,串口用于打印AD9371配置流程信息,JESD204B TX/RX用于连接AD9371数据通道。其余的I2C、INTC和GPIO为拓展接口。

图12 基于MicroBlaze的代码框架

数据发射的两种模式如下。

① DMA模式下,在MicroBlaze初始化完毕后,将事先存储在Flash中的正弦波矩阵送入DDR2暂存,随后由DMA接口直接送入AD9371数字接口,再经过DAC采样送入到混频器中加入载波,最终送到发射通道。

② DDS模式下,MicroBlaze直接通过配置AD9371_CORE IP生成不同相位和不同频率的通道波形。

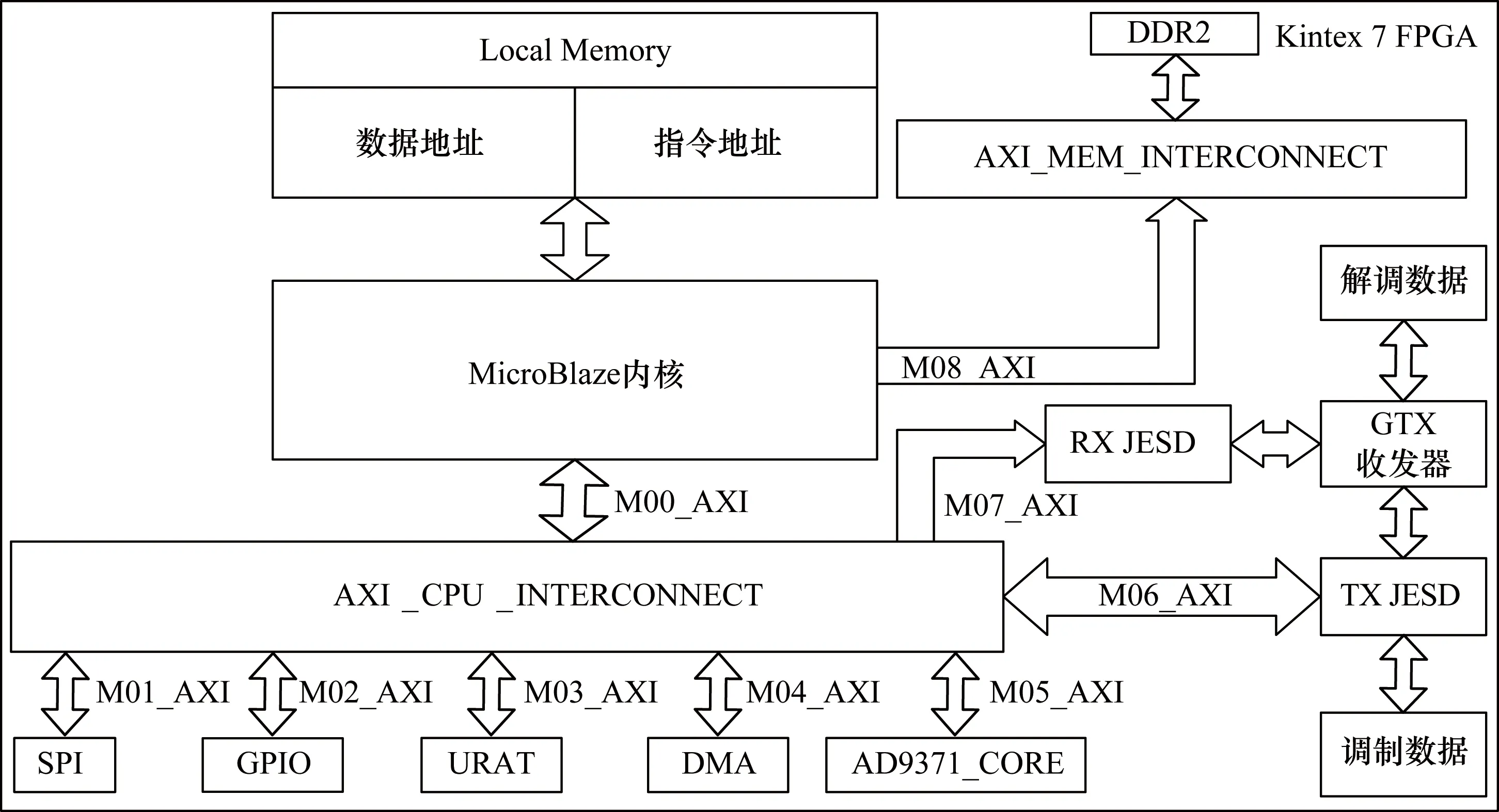

4.2 MicroBlaze总线连接

图13为MicroBlaze软核的部分总线连接图,其中AXI_CPU_INTERCONNECT模块为AXI转PLBv46模块,用于连接外设模块。M00_AXI~M08_AXI为主总线。其中,M06_AXI和M07_AXI直接连接JESD204B RX和TX IP,二者共同连接到JESD204B PHY IP即实际物理接口IP,这个IP直接与硬件引脚对应。调制数据和解调数据为拓展代码。

图13 基于MicroBlaze的总线图

5 结论

经测试,本平台系统性能良好,增益比官方DEMO板提高了1~2 dB,且总体功耗没有增加,维持在5 W左右。

对比NI和ADI的平台,目前ADI的AD9371一体化射频芯片解决方案虽然牺牲了功耗,但在芯片面积、适配性和性能上占有绝对优势。

本平台的意义在于降低传统离散化硬件设计的复杂度,实现面积最优化。嵌入MicroBlaze软核处理器,通过修改C语言代码即可修改AD9371的配置参数,无须修改FPGA逻辑代码,有效简化了配置流程,极大地提升了应用到多种工作场景的效率。所提出的SDR平台具有商用价值,可以根据需求灵活、快速地适配不同场景,甚至可以更换处理器软核(如选择NiosII[13]、龙芯[14]等),通过提升处理器的速度,也间接提升了平台的事务处理性能。

虽然一款通用的SDR平台可以应用于多种场景,但还是有以下劣势:

① 使用受到功率、稳定性、成本和半导体技术的限制。

② 对于特定波形的处理必然增加复杂度和成本。

③ 无法实现很高的频率,对于更高的频率(如12 GHz),目前只能离散化,集成化无法实现。

当然集成化的方案目前在航天领域还无法应用,离散化的方案稳定性更高一些。虽然本平台具有航天应用潜质,但由于航天环境比较复杂,最终能否适应,还需要在可靠性和稳定性方面继续做深入研究。