保护环对双向可控硅静电防护器件电容特性的影响

杨帅康 汪洋 苏雪冰 张玉叶 杨红娇,

关键词:双向可控硅;保护环;寄生电容;传输线脉冲测试系统

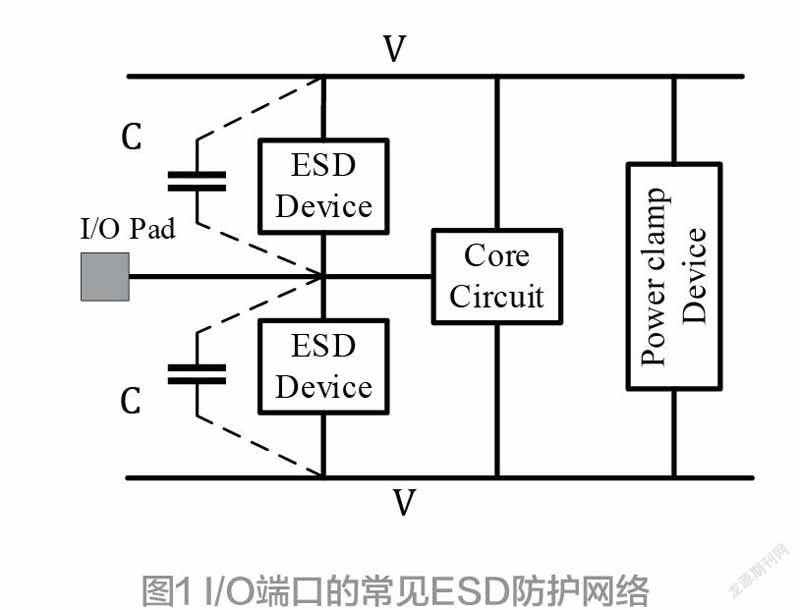

静电释放(electro-staticdischarge,ESD)是集成电路(IC)的主要可靠性问题之一[1],因此IC片上需放置静电防护器件,其端口的常规静电防护网络如图1所示。静电防护器件的设计首先应满足ESD窗口要求,此外,ESD防护器件的寄生电容(CESD)应尽可能小,避免器件寄生电容过大影响被保护电路的工作速度[2]。特别地,传送高频信号的IC端口对ESD器件电容更加敏感[3]。常规静电防护器件有二极管、三极管、金属氧化物场效应晶体管和可控硅整流器件(siliconcontrolledrectifier,SCR),其中SCR拥有最佳的单位面积静电泄放能力,可为IC提供高水平的静电防护[4]。为了保护信号电平高于和低于地的IC引脚,文献[5][6]提出了双向可控硅(dual-directionSCR,DDSCR)静电防护器件,以满足正向和反向ESD防护需求。在与内核电路集成时DDSCR器件外围需增加保护环,以实现器件与电路隔离,对于防止少数载流子迁移对电路造成的干扰和损坏至关重要,并且也是防止闩锁的常用方式[7]。本文的主要工作是分析讨论保护环对DDSCR器件电容特性的影响,在高低压工艺下分别制备了带保护环和不带保护环的DDSCR器件,测试并分析了器件寄生电容差异的根本原因。目前基本没有文献对DDSCR的电容模型开展研究,本文工作对于低容静电保护器件设计具有一定的指导意义。

1低压DDSCR器件结构

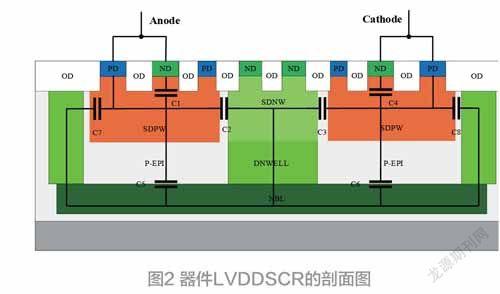

图2为常规低压DDSCR器件剖面图,器件内部不同掺杂类型层次之间的结电容以及它们的拓扑连接关系一并展示于图中。LVDDSCR器件使用的层次有N注入(ND)、P注入(PD)、P阱(SDPW)、N阱(SDNW)、深N阱(DNWELL)、P外延层(P-EPI)和N型埋层(NBL)。器件采用指状版图画法,为216μm×89μm和232μm×105μm,使用0.18-μmBCD工艺制造。

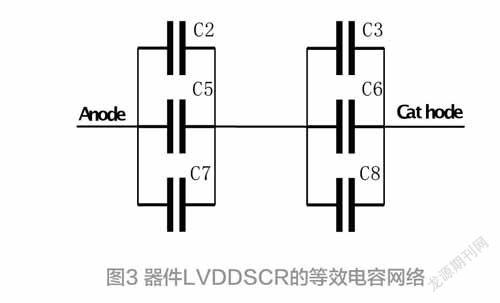

LVDDSCR器件的等效电容包括C1-C8,其中ND与SDPW之间形成的结电容为C1和C4;器件中间用来隔离的复合层次SDNW/DNWELL与P-EPI之间形成的结电容为C2和C3;P-EPI与NBL之间形成的结电容为C5和C6;左右两侧的隔离DNWELL与P-EPI之间的结电容为C7和C8。根据器件的剖面图分析,得到LVDDSCR器件的等效电容网络如图3所示,结电容C1和C4短路,不参与电容网络搭建。

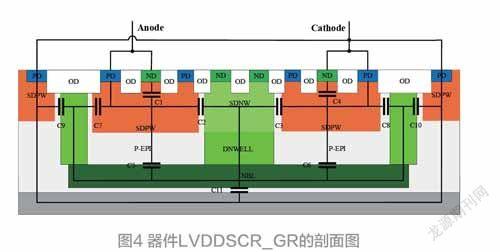

图4为LVDDSCR_GR器件剖面图,LVDDSCR_GR在LVDDSCR的外周增加了一圈P型保护环,该保护环由P+注入以及包裹它的P阱(SDPW)构成。

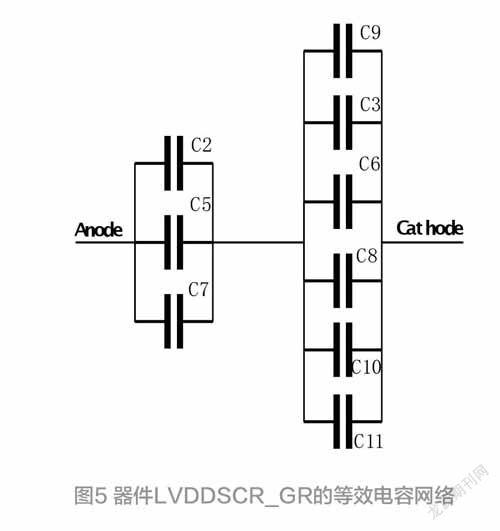

保护环的加入,使得器件增加了DNWELL与P-EPI之间的结电容C9、C10,以及P-EPI与NBL间的结电容C11,因此,器件LVDDSCR_GR的等效电容网络变为图5所示。与Anode连接的结电容没有变化,但是结电容C9、C10、C11的加入使得连接到Cathode的电容值增大,因而使得整个器件寄生电容增大。

2低压DDSCR器件测试与分析

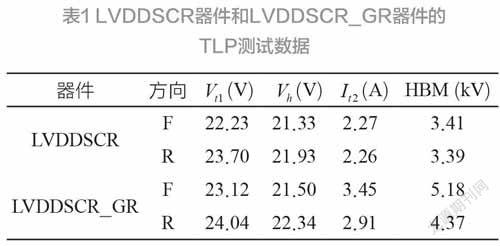

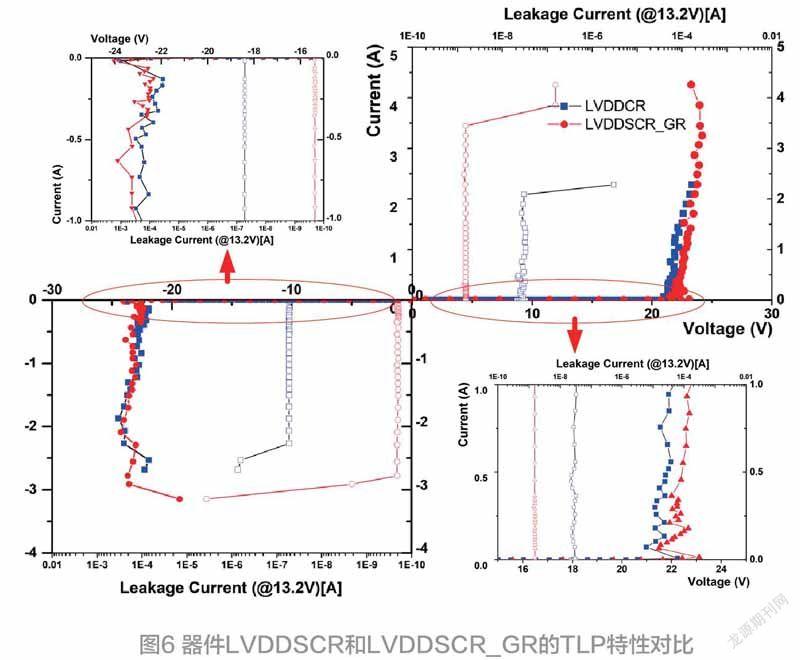

传输线脉冲(TLP)测试系统可获得准静态的I-V特性曲线,是表征器件静电性能的重要手段之一。该测试系统提供的脉冲信号为10ns上升时间和100ns脉冲宽度,可得到等效的HBM静电防护等级。LVDDSCR和LVDDSCR_GR器件的TLP测试结果如图6所示,器件的关键静电性能参数列于表1。

器件的TLP测试结果表明,不带P型保护环的器件LVDDSCR与带保护环的器件LVDDSCR_GR相比,触发电压和维持电压基本相同。它们的正向触发电压Vt1分别为22.23V和23.12V,反向触发电压分别为23.7V和24.04V,维持电压Vh都在22V左右。这说明二者的ESD电流主要泄放路径一致,仍位于器件内部。保护环的增加使得器件内部的热量分布有所改进,因此LVDDSCR_GR器件的失效电流相比LVDDSCR有所提升。该器件的失效电流(It2)略有不对称,这是由于版图布局采用指状,不是完全对称的布局,因此器件的正反会存在略微的不对称现象。

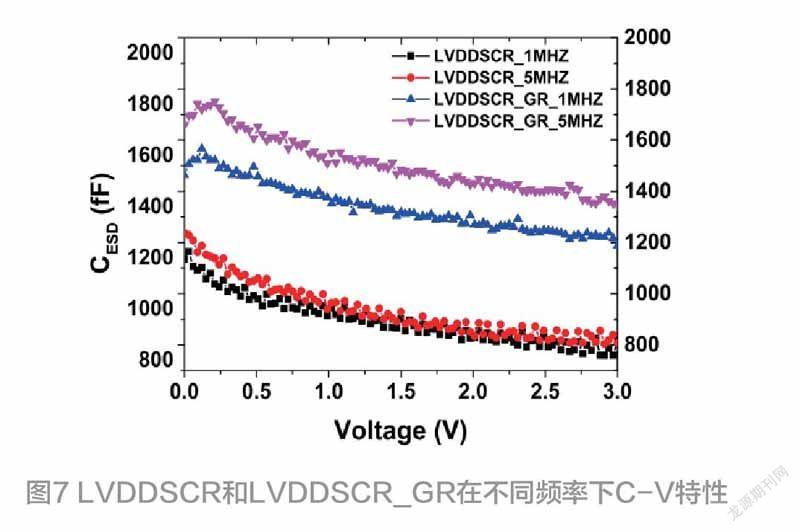

Keysight公司的B1505A功率器件分析仪可测试器件C-V特性。采用该设备测试获得的LVDDSCR、LVDDSCR_GR器件在1MHz和5MHz频率下的C-V特性曲线如图7所示。随着电压的增加,器件的寄生电容呈下降趋势,同一个器件在5MHz频率下的电容值高于1MHz频率下的电容值。器件LVDDSCR在增加了保护环后,在1MHz的频率下测试发现,LVDDSCR与LVDDSCR_GR器件的寄生电容有较大差别。在零偏压条件下,1MHz的频率下电容值由原来的1135fF增加到1463fF,5MHz的频率下电容值由原来的1237fF增加到1658fF。

为了评定ESD器件的寄生电容和泄放静电能力,引入品质因子(featureofmerit,FOM)来表征ESD器件的综合性能:

式中VHBM为ESD器件能够承受的HBM电压,CESD为器件寄生电容,A为器件面积。

通过计算得到在1MHz下LVDDSCR与LVDDSCR_GR的正向FOM值分别为15.6和15.5,反向FOM值分别为14.5和12.2,说明LVDDSCR器件综合能力最佳。

3高压DDSCR器件结构

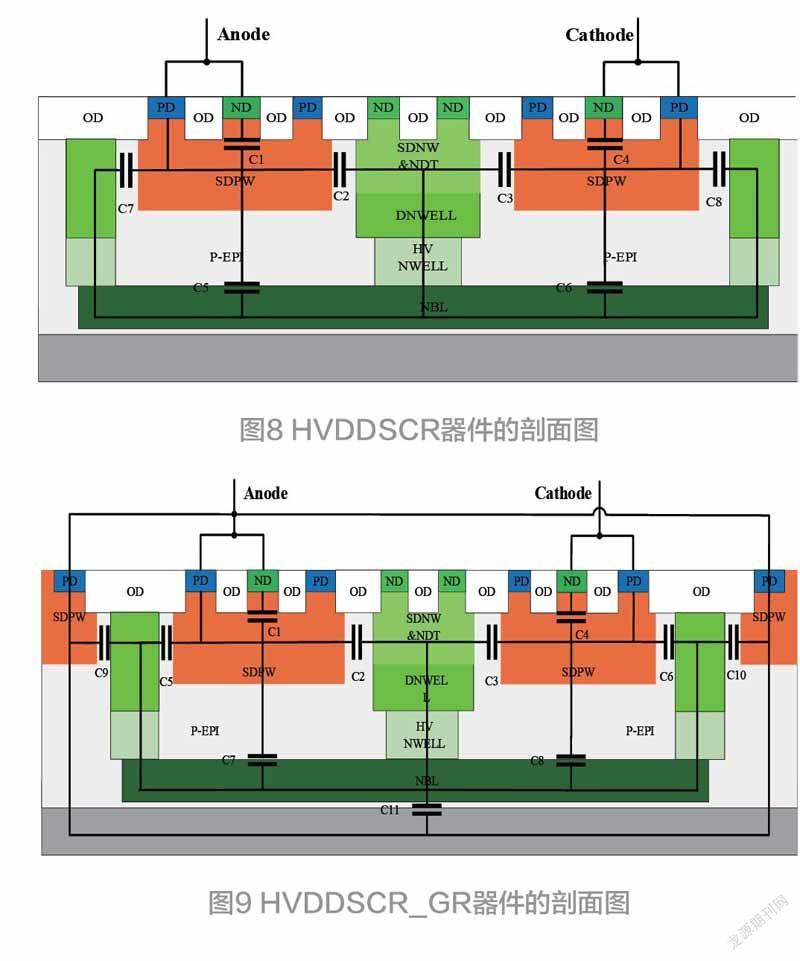

高壓工艺下双向可控硅带保护环和不带保护环的静电保护器件剖面图分别如图8和9所示。HVDDSCR与LVDDSCR器件结构相似,但是由于工艺发生变化,额外增加了高压N阱(HVNWELL)层次,同时为了调节器件的触发电压,触发面增加了NDT层次,SDPW与SDNW之间的距离也增加。两个高压器件的寄生电容网络与LVDDSCR和LVDDSCR_GR器件相同,已在剖面图上标识,因此不再单独作图。器件HVDDSCR和HVDDSCR_GR均为多指结构,采用指状版图画法,为221μm×95μm和237μm×111μm,使用0.18-μmBCD工艺制造。

4高压DDSCR器件测试与分析

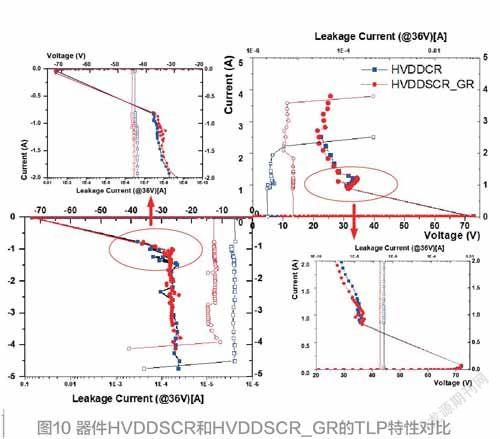

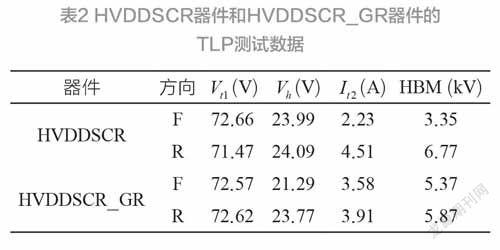

利用TLP系统测试得到HVDDSCR和HVDDSCR_GR器件的ESD特性。在高压工艺下,由于ESD设计窗口的不同,器件的部分尺寸与层次进行了调整,因此器件的ESD特性相应发生了变化。

器件HVDDSCR和HVDDSCR_GR的触发电压都在72V左右,HVDDSCR的维持电压比HVDDSCR_GR的稍高一些,但都在23V左右。器件HVDDSCR的正反向失效电流分别为2.23A和4.51A,器件HVDDSCR_GR的正反向失效电流都在3.5A以上,综合来看器件HVDDSCR_GR的鲁棒性更强。同样,高压器件版图布局也采用指状画法,亦存在正反向失效电流不对称现象。

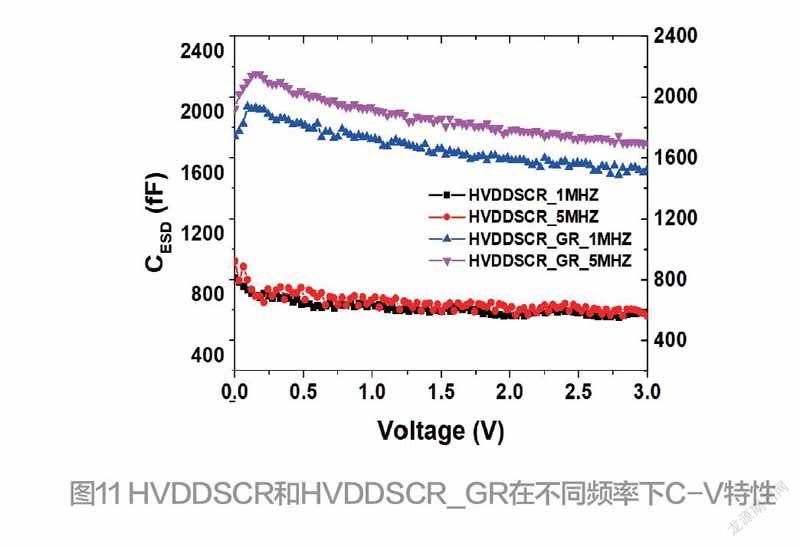

电容测试结果如图11所示,高压工艺下不带保护环的DDSCR器件等效电容在1000fF以下。在1MHz频率下零偏压时HVDDSCR的寄生电容为810fF,HVDDSCR_GR电容为1740fF。在5MHz频率下HVDDSCR_GR的电容值由HVDDSCR的922fF增加到1922fF。通过计算得到在1MHz下HVDDSCR与HVDDSCR_GR的正向FOM值分别为19.7和10.6,反向FOM值分别为39.8和11.7,验证了HVDDSCR_GR器件的综合能力最佳,与低压工艺分析一致。

5结语

论文分别在高低压工艺下制备了带保护环和不带保护环的DDSCR器件,TLP测试结果表明,P型保护环对器件的触发点、维持点以及鲁棒性影响不大,并未带来较大变化,原因是DDSCR器件泄放电流的主要路径存在于器件内部,P型保护环不会影响器件的泄放静电能力。而C-V测试结果发现,P型保护环会引入新的结电容,使得DDSCR器件的寄生电容网络发生变化,从而增大DDSCR器件的寄生电容。