新型低栅源漏电容射频LDMOS器件设计*

马荣晶,刘斯扬,魏家行,孙伟锋

(东南大学国家专用集成电路系统工程技术研究中心,南京210096)

新型低栅源漏电容射频LDMOS器件设计*

马荣晶,刘斯扬,魏家行,孙伟锋*

(东南大学国家专用集成电路系统工程技术研究中心,南京210096)

为了降低栅源寄生电容Cgs,提出了一种带有阶梯栅n埋层结构的新型射频LDMOS器件;采用Tsuprem4软件对其进行仿真分析,重点研究了n埋层掺杂剂量和第二阶梯栅氧厚度对栅源寄生电容Cgs的影响,并结合传统的射频LDMOS基本结构对其进行优化设计。结果表明:这种新型结构与传统的射频LDMOS器件结构相比,使得器件的栅源寄生电容最大值降低了15.8%,截止频率提高了7.6%,且器件的阈值电压和击穿电压可以维持不变。

射频LDMOS;栅源寄生电容Cgs;Tsuprem4;优化

射频横向双扩散金属氧化物半导体(RF LDMOS)器件具有线性度好、增益高、以及价格低廉等优势[1-3],并且其易于和CMOS工艺集成[4],因此被广泛应用于GSM/CDMA移动通讯基站、数字广播电视发射和射频通讯领域中[5-6]。

截止频率作为射频LDMOS频率特性的一个重要指标,直接决定了器件的工作频率[7]。提高射频LDMOS的截止频率特性,需要减小LDMOS栅源寄生电容Cgs和栅漏寄生电容Cgd[8]。近年来学者们一直致力于减小栅漏寄生电容Cgd的研究,如Wilson P H[9]等人提出了槽栅结构,电子科技大学的王一鸣和张波[10]等人提出了槽型漂移区结构,而很少有人研究栅源寄生电容Cgs的减小。本文从减小栅源寄生电容Cgs的角度出发,提出了一种带有阶梯栅n埋层结构的新型射频LDMOS器件,并借助Tsuprem4工具模拟,分析第二阶梯栅氧的厚度与其下n埋层的掺杂剂量对栅源寄生电容Cgs的影响,并最终给出优化结构。

1 结构与分析

1.1 器件结构

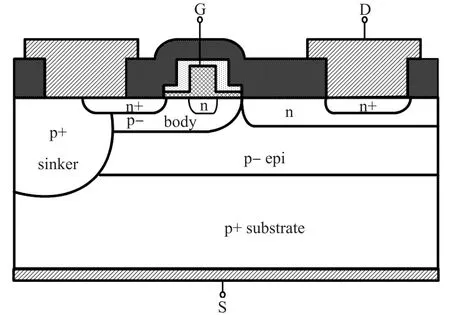

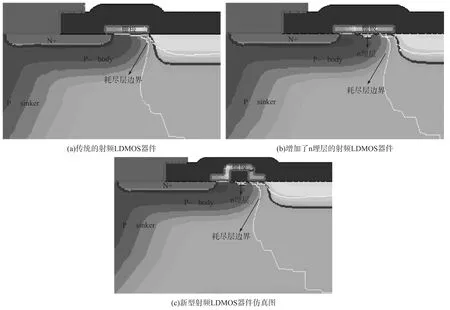

传统的射频LDMOS结构和本文提出的新型射频LDMOS结构分别如图1和图2所示。

图1传统的射频LDMOS器件中,其外延层浓度为1×1015cm-3,P-body的掺杂剂量为1.5×1014cm-2,P+Sinker的掺杂剂量为1×1016cm-2,沟道长度为1.2 μm,n-漂移区的长度为4.0 μm、掺杂剂量为1.5× 1012cm-2,栅氧厚度为35nm。整个器件的击穿电压为90 V,阈值电压为1.8 V。图2为本文提出的带有阶梯栅n埋层的新型射频LDMOS器件,与传统结构相比,不同之处在于新结构在P-body中添加了n型埋层,且该n埋层上方的栅氧厚度(称为第二阶梯栅氧)明显厚于P-body沟道区上方的栅氧厚度,形成了阶梯型栅氧。另外,为了减小n型埋层对器件阈值电压的影响,设计中增加了P-body的长度,使得有效的p型沟道区长度保持不变,即新型射频LD⁃MOS器件除了n埋层和第二阶梯栅氧之外,其他的结构参数与传统的射频LDMOS器件保持一致。

图1 传统的射频LDMOS器件结构

图2 新型射频LDMOS器件结构

1.2 理论分析

对于射频LDMOS器件,栅源寄生电容主要由栅极与P-body区域重叠的氧化层电容组成,该电容为金属-绝缘体-半导体系统形成的MIS电容[11-12],是绝缘体电容Ci和半导体电容Cs的串联。减小该电容一般从两方面入手:一是增大栅氧厚度,从而减小绝缘体电容;二是增大半导体耗尽的宽度。

图3(a)、图3(b)和图3(c)显示的分别是传统的射频LDMOS器件、仅添加了n埋层的射频LDMOS器件和本文提出的新型射频LDMOS器件在固定栅压和漏压(Vgs=10 V,Vds=28 V)情况下的耗尽区分布图。通过对比图3(a)和图3(b)可以发现,n型埋层的存在辅助了P-body向P型外延层的耗尽,使得耗尽区面积增大,通过平板电容原理可知,这样半导体耗尽区电容得到了减小。另外,为了不显著减小阈值电压,保持器件有效的p型沟道区长度不变,P-body的长度增加了,这样势必会带来绝缘体电容的增加。因此本文提出了增加n型埋层上方的栅氧厚度的方法,也就是阶梯状栅氧结构,来减小绝缘体电容。由图3(b)和图3(c)的对比可以发现,阶梯状栅氧不会对耗尽层的大小产生影响,且由于n型埋层的存在,其上方的栅氧厚度可以做到很厚,这样就可以抑制由于n型埋层的引入所带来的绝缘体电容的增大。

图3 射频LDMOS器件在Vgs=10 V,Vds=28 V时的耗尽区分布图

2 器件的优化设计

根据上面的分析可知,本文提出的具有阶梯栅n埋层的射频LDMOS新结构具有减小栅源寄生电容的作用,下面针对该新结构,通过变化阶梯栅的厚度和n埋层的掺杂剂量来优化器件的栅源寄生电容。

2.1 n埋层掺杂剂量对栅源寄生电容的影响

图4为n埋层掺杂剂量对栅源寄生电容影响的曲线图,研究选择的第二阶梯栅氧厚度分别为0.2 μm、0.3 μm和0.4 μm。从图中可以看出,栅源寄生电容的大小随着n埋层掺杂剂量的增加先减小后增大,n埋层的掺杂剂量存在一个最优值。这是因为当n埋层掺杂剂量很小时,低浓度n埋层的辅助耗尽作用并不明显,而随着n埋层掺杂剂量的增大,辅助耗尽作用开始显现出来,导致栅源寄生电容开始减小。然而,当n埋层掺杂剂量大到一定程度时,n埋层由于浓度很高不能完全耗尽,辅助耗尽作用受到了限制,因此栅源寄生电容反而随着n埋层掺杂剂量的增加而增加,最终保持不变。对于本文提出的具有阶梯栅n埋层的射频LDMOS器件,n埋层存在一个最优掺杂剂量值,大小为1.0×1013cm-2。

图4 n埋层掺杂剂量对栅源寄生电容的影响

2.2 第二阶梯栅氧厚度对栅源寄生电容的影响

图5为第二阶梯栅氧厚度对栅源寄生电容影响的曲线图。研究选择的掺杂剂量分别为1.0× 1013cm-2、2.0×1013cm-2和3.0×1013cm-2。从图5可以看出,栅源寄生电容随着第二阶梯栅氧厚度的增大不断减小,但是随着第二阶梯栅氧厚度越来越厚,栅源寄生电容减小的趋势变缓。正如1.2节所述,栅源寄生电容是由绝缘体电容Ci和半导体电容Cs串联而成,随着第二阶梯栅氧厚度的增大,绝缘体电容减小,因此栅源寄生电容随着第二阶梯栅氧厚度的增大而减小很容易理解。但是,随着绝缘体电容的减小,其在栅源寄生电容中所占比例也相应减小,从而导致栅源寄生电容的减小趋势变缓。从减小栅源寄生电容的角度来说,第二阶梯栅氧的厚度越厚越好,但是从工艺和可靠性角度考虑,第二阶梯栅氧的厚度并不宜过厚。因此,最终选取第二阶梯栅氧的厚度为0.45 μm。

图5 第二阶梯栅氧厚度对栅源寄生电容的影响

综上所述,对于本文提出的具有有阶梯栅n埋层的射频LDMOS器件,n埋层的掺杂剂量和第二阶梯栅氧厚度对栅源寄生电容都有一定的影响。栅源寄生电容随着n埋层掺杂剂量的增加先减小后增大,存在一个最优值;对于第二阶梯栅氧厚度,栅源寄生电容随着第二阶梯栅氧厚度的增加而减小,但是考虑到做厚栅氧的工艺成本较高且可靠性不好,因此第二阶梯栅氧的厚度也不宜过厚。根据上述研究结果,最终确定n埋层的掺杂剂量为1.0×1013cm-2,第二阶梯栅氧厚度为0.45 μm。

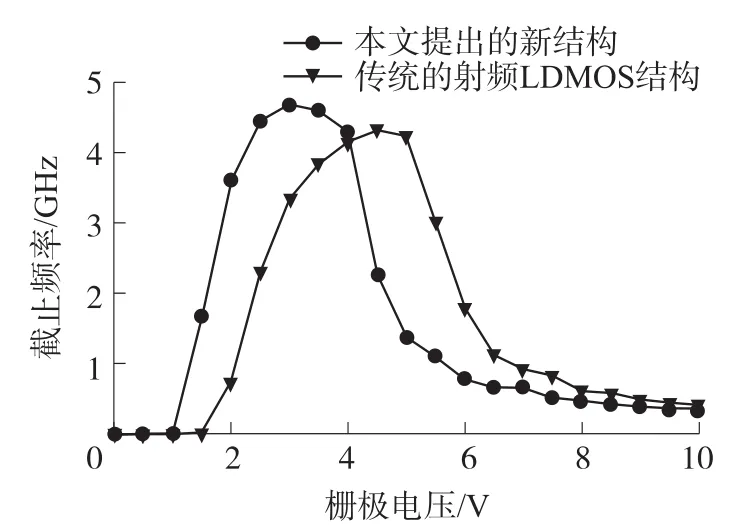

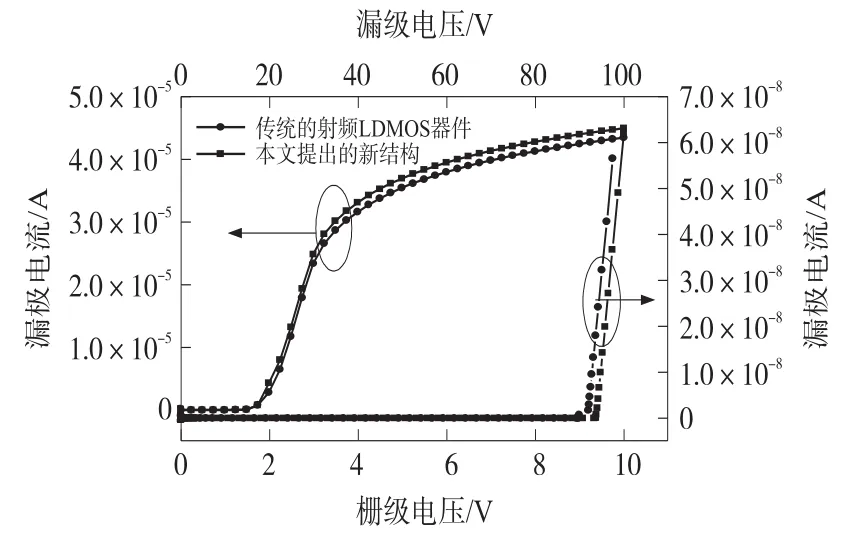

在重新设计了新型射频LDMOS器件的结构参数后,本文对传统射频LDMOS器件和新型射频LDMOS器件进行了仿真分析。图6和图7分别为两种器件的栅源寄生电容和截止频率的仿真曲线。

图6 两种器件的栅源寄生电容曲线对比图

图7 两种器件的截止频率曲线对比图

从图中可以看出,相比于传统的射频LDMOS器件,本文提出的新结构使得栅源寄生电容最大值降低了15.8%,截止频率提高了7.6%。当然,相比于传统结构,由于n埋层的引入,新结构的栅源寄生电容和截止频率最大值也向左发生了漂移。此外,本文还仿真了两种器件的阈值电压和击穿电压曲线图,结果如图8所示。从图8可以看出,新结构对器件的阈值电压和击穿电压几乎没有产生影响。

图8 两种器件的阈值电压和击穿电压曲线对比图

3 总结

本文从减小栅源寄生电容的角度出发,提出了一种带有阶梯栅n埋层结构的新型射频LDMOS器件,并采用Tsuprem4软件对新结构进行了仿真分析和优化设计。研究发现,n埋层的掺杂剂量对于栅源寄生电容来说存在一个最优值,而在一定程度上提高第二阶梯栅氧的厚度可以减小栅源寄生电容,但是从工艺和可靠性角度考虑,第二阶梯栅氧厚度也不宜做得过厚。最终仿真结果表明,本文提出的具有阶梯栅n埋层的射频LDMOS器件结构,能有效的减小器件的栅源寄生电容,提高器件的截止频率,且可以使得器件的阈值电压和击穿电压基本保持不变。

[1]Wood,Alan,Brakensiek W.Application of RF LDMOS Power Transistors for 2.2 GHz Wideband-CDMA[C]//1998 IEEE Radio and Wireless Conference,1988.RAWCON 98,1998:309-312.

[2]王佃利,刘洪军,吕勇,等.硅LDMOS射频功率器件的发展历程与趋势[J].固体电子学研究与进展,2011,02:141-146,173.

[3]Kashif A.Svensson C.Wahab Q.High Power LDMOS Transistor for RF-Amplifiers[C]//International Bhurban Conference on Ap⁃plied Sciences and Technology,2007.IBCAST 2007,2007:1-4.

[4]Burger W.R.Recent Advances in RF-LDMOS High-Power IC De⁃velopment[C]//IEEE International Conference on IC Design and Technology,2009.ICICDT‘09,2009:35-38.

[5]Theeuwen S J C H,Qureshi J H.LDMOS Technology for RF Pow⁃er Amplifiers[J].IEEE Transistors on Micro Theory and Tech⁃niques,2012:1755-1763.

[6]Hou Fucheng,Zhang Yaohui.RF LDMOS Power Transistor for Multi-Carrier GSM Base Station[C]//2014 IEEE International Wireless Symposium(IWS),2014:1-3.

[7]Gruner D,Sorge R,Bengtsson O,et al,Analysis,Design,and Eval⁃uation of LDMOS FETs for RF Power Applications up to 6 GHz[C]//IEEE Transactions on Microwave Theory and Techniques,2010:4022-4030.

[8]Chiu Chia-Sung,Chen Kunming,Huang Guowei,et al,Capacitance Characteristics Improvement and Power Enhancement for RF LDMOS Transistors Using Annular Layout Structure[C]//IEEE Transactions on Microwave Theory and Techniques,2011:638-643.

[9]Wilson P H A.Trench Gate LDMOS for RF Applications[C]//The 11th IEEE International Symposium on Electron Devices for Mi⁃crowave and Optoelectronic Applications,2003:43-47.

[10]王一鸣,李泽宏,王小松,等.射频功率LDMOS槽型漂移区结构优化设计[J].半导体学报,2006(8):1441-1446.

[11]Chen Xiaofei,Shen Yading,Zou Xucheng,et al.A New High Perfor⁃mance RF LDMOS with Vertical n+n-p-p+Drain StruScture[C]// 2013 IEEE 10th International Conference on ASIC,2013:1-4.

[12]Chen Kunming,Huang Guowei,Chen Boyuan,et al,LDMOS Tran⁃sistors High-Frequency Performance Enhancement by Strain[J].IEEE Electron Device Letters,2012:471-473.

马荣晶(1991-),女,硕士生,主要研究方向为GaN HEMT器件,jingjingdelan@ 163.com;

孙伟锋(1977-),男,博士,教授,博士生导师,主要从事数模混合电路、功率器件与功率集成电路、高压射频器件的研究,swffrog@seu.deu.cn。

The Sign of New RF LDMOS Device with Low Cgs*

MA Rongjing,LIU Siyang,WEI Jiaxing,SUN Weifeng*

(National ASIC System Engineering Research Center,Southeast University,Nanjing 210096,China)

In order to reduce gate-source parasitic capacitance Cgs,a new RF LDMOS structure with a step gate oxide and an additional n buried layer under the gate is introduced.The Tsuprem4 tools are used for the simulation and analysis,study is mainly focused on the influences upon Cgsfrom the doping concentration of n buried layer and the depth of the second step gate oxide,after that,the optimization design of the device is carried out.Results show that comparing to conventional RF LDMOS,this new structure reduces the maximum Cgsby 15.8%and improves the cutoff frequency by 7.6%,while the threshold voltage and breakdown voltage remain unchanged at the same time.

RF LDMOS;gate-source parasitic capacitance;Tsuprem4;optimization

TN432

A

1005-9490(2015)06-1228-04

2520

10.3969/j.issn.1005-9490.2015.06.003

项目来源:港澳台科技合作专项项目(2014DFH10190);青蓝工程项目和东南大学研究生科研基金项目(YBPY1403)

2015-03-09 修改日期:2015-04-07